WOJSKOWA AKADEMIA TECHNICZNA

Instytut Teleinformatyki i Automatyki

Technika Mikrokomputerowa

Temat: Konfigurowanie sterowników przerwań płyt głównych IBM PC

Paweł Garkowski

I5X1S0

System obsługi przerwań sprzętowych

Najbardziej aktywnym elementem komputera jest sam procesor. Niektóre z bloków funkcjonalnych, które składają się na jego otoczenie, wykonują operacje rozciągające się w czasie na wiele cykli zegarowych. Urządzenia te nie wymagają udziału procesora dla wykonania zleconych im zadań. Są to zwykle mniej lub bardziej niezależne kontrolery, często wyposażone we własny procesor. Na ogół wystarczy, by procesor zaprogramował rejestry sterujące tego urządzenia, wydając tym samym polecenie wykonania operacji.

Zainicjowana przez CPU operacja, jakkolwiek może trwać tysiące cykli zegarowych procesora, musi się kiedyś zakończyć (choćby błędem). Musi więc istnieć sposób poinformowania procesora o tym fakcie. Istnieją tutaj zasadniczo dwie możliwości:

procesor okresowo wysyła zapytanie do urządzenia. Częstotliwość „odpytywania" jest ustalana przez wykonywany program i sposób stanowi kompromis pomiędzy szybkością reakcji procesora na zakończenie operacji a spowolnieniem jego pracy nad zadaniem pierwszoplanowym. Kod procedury odpytywania musi być zintegrowany z programem, co powiększa jego rozmiar. Zbyt częste odpytywanie hamuje wykonywanie bieżącego programu. Zbyt długie przedziały czasowe między kolejnymi odpytywaniami i nierównomiernie napływający strumień danych mogą spowodować, że część z nich zostanie utracona na skutek przepełnienia nie opróżnianego bufora wewnętrznego obsługiwanego urządzenia;

urządzenie samo zgłasza wykonanie zadania. W najbliższym dogodnym dla siebie momencie procesor przerywa realizację aktualnie wykonywanego programu by, zapamiętawszy stan swoich rejestrów, przejść do realizacji procedury reagującej na zgłoszenie urządzenia. Kod tej procedury na ogół nie znajduje się w ciele programu, lecz w pamięci stałej komputera.

Metoda opisana w punkcie pierwszym znana jest też pod nazwą polling i nie znajduje praktycznego zastosowania w komputerach PC. W drugim przypadku mówimy, że wystąpiło przerwanie (ang. interrupt) sprzętowe (gdyż pochodzące od urządzenia, a nie jest instrukcją programu). Ta forma sterowania przepływem danych jest w PC szeroko wykorzystywana. Znajduje ona zastosowanie w obsłudze urządzeń intensywnie wymieniających dane z pamięcią operacyjną, a więc przede wszystkim łącz szeregowych i równoległych, kontrolerów dysków, kart sieciowych oraz urządzeń, które dostarczają dane w sposób nieregularny - klasycznym przykładem jest tutaj klawiatura komputera. Trudno sobie wyobrazić bardziej rozsądne podejście do obsługi klawiatury, niż reagowanie na naciśnięcie klawisza za pomocą obsługi przerwania pochodzącego od sterownika klawiatury. W praktycznych zastosowaniach komputera (szczególnie wyposażonego w myszkę) klawiatura może przecież godzinami nie wysyłać żadnego znaku.

Procesor posiada zwykle tylko jedno wejście INT sygnalizujące przerwanie sprzętowe. Ponadto architektura PC zakłada, że każde przerwanie ma pewien priorytet, tzn. obsługa zgłoszeń uwzględnia nie tyle moment ich nadejścia, co raczej stopień ich ważności. Już samo to założenie wymaga rozróżniania zgłoszeń poprzez przyporządkowanie każdemu z urządzeń oddzielnego kanału wejściowego.

Konieczne stało się więc zastosowanie specjalizowanego układu zajmującego się wyłącznie ich obsługą. Funkcję kontrolera przerwań w komputerze XT pełni układ 8259A, a w modelach AT i PS/2 - dwa takie układy połączone kaskadowo. W nowszych rozwiązaniach płyt głównych komputerów AT nie znajdziemy ich jako samodzielnych układów scalonych, gdyż wchodzą one przeważnie w skład jednego z układów wysokiej skali integracji, tworzących „obudowę" procesora. Ze względu jednak na konieczność zachowania zgodności architektury można się odwoływać do ich rejestrów.

Kontroler 8259A ma osiem linii wejściowych, które przyjmują sygnały zgłoszeń. Układy 8259A mogą być łączone w kaskady, powielając tym samym liczbę dostępnych wejść. Istnieje również (nie wykorzystywana w architekturze PC) możliwość sterowania zewnętrznym buforem pośredniczącym między układem a silnie obciążonymi magistralami systemowymi.

Układ scalony 8259A

Montowany w IBM-PC/XT/AT układ scalony 8259A produkowany był między innymi przez firmy Intel i AMD. Mógł pracować nie tylko w trybie zgodnym z procesorami 8088/86/286, ale również z 8080/8085. Został on zaprojektowany przed powstaniem procesora 80286, w późniejszej fazie podzielił los innych bloków architektury i został wchłonięty przez układ chipset przy zachowaniu zgodności na poziomie rejestrów.

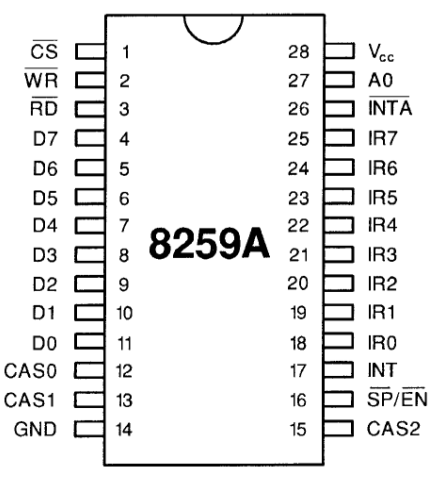

Rozkład wyprowadzeń

układu 8259A

IR0-IR7 (Interrupt Reąuesi) - każde z tych wyprowadzeń może być połączone z co najwyżej jednym urządzeniem, które wymuszając wysoki poziom logiczny na przypisanym sobie wejściu zgłasza żądanie obsługi przerwania. Wejście IR0 posiada najwyższy, a IR7 najniższy priorytet;

~CS (Chip Select) - wejście umożliwiające procesorowi wprowadzenie układu w tryb programowania;

~WR (Write) - procesor wymusza niski poziom logiczny na tym wejściu, chcąc zapisywać dane do wewnętrznych rejestrów układu;

~RD (Read) - procesor wymusza niski poziom logiczny na tym wejściu, chcąc odczytywać dane z wewnętrznych rejestrów układu;

D0-D7 dwukierunkowa magistrala danych, służąca do komunikacji między procesorem i kontrolerem (zapis i odczyt rejestrów wewnętrznych) oraz przekazywania procesorowi numeru przerwania;

CAS0-CAS2 (Cascade) - lokalna magistrala adresowa, używana przy kaskadowym połączeniu układów 8259A. Umożliwia ona zaadresowanie do 8 takich układów;

~SP/EN (Slave Program/Enable Buffer) - w buforowanym trybie pracy pełni rolę wyjścia (EN) sterującego buforem zewnętrznym. W trybie nie buforowanym jest to wejście (~SP) konfigurujące układ jako Master (~SP=1) lub Slave (~SP=0);

INT (Interrupt) - wyjście to połączone jest bezpośrednio z wejściem INTR procesora, jeżeli układ 8259A pracuje jako Master. Układ pracujący w trybie Slave połączony jest swoim wyjściem INT z jednym z wejść IRn kontrolera Master;

~INTA (Interrupt Acknowledge) - wejście to połączone jest z wyjściem INTA procesora. Przyjmuje ono sygnał potwierdzenia przyjęcia przerwania przez CPU;

A0 wejście istotne jedynie w trybie programowania, służące do rozróżniania rozkazów;

Vcc wejście napięcia zasilającego (+5V);

GND masa zasilania;

Cykl przyjęcia zgłoszenia

Układ 8259A dysponuje trzema 8-bitowymi rejestrami:

IMR - Interrupt Mask Register - Rejestr Maski Przerwania

IRR - Interrupt Request Register - Rejestr Zgłoszenia Przerwania

ISR - Interrupt Service Register - Rejestr Obsługi Przerwania

Pozycja bitowa n każdego z nich odpowiada jednemu z wejść IRn.

Schemat blokowy układu 8259A

Urządzenie połączone z wejściem o numerze n zgłasza przerwanie wymuszając wysoki poziom logiczny na linii IRn. Ustawiając bit n w rejestrze IMR można spowodować ignorowanie wszelkich przerwań nadchodzących tą linią. Jeżeli wspomniany bit jest wyzerowany, informacja o przerwaniu przekazywana jest dalej i powoduje ustawienie bitu n w rejestrze IRR. Priorytet zgłoszeń na wejściach IR0-IR7 nie jest jednakowy i maleje ze wzrostem numeru wejścia. Ponieważ jednocześnie mogą nadchodzić zgłoszenia z wielu linii, układ oceny priorytetu wybiera jednorazowo tylko jeden z nich - ten o najwyższym priorytecie. Jednocześnie aktywowany jest sygnał INT, informujący procesor o konieczności obsługi przerwania. Jeżeli obsługa przerwań nie jest programowo zablokowana, procesor reaguje sygnałem potwierdzenia na wyjściu ~INTA, które jest połączone z wejściem ~INTA układu 8259A. Wybrany przez układ oceny priorytetu bit rejestru IRR przekazywany jest teraz do rejestru ISR. Oznacza to, że w tym momencie obsługiwane jest przerwanie z linii o numerze odpowiadającym ustawionej pozycji bitowej rejestru ISR.

Procesor wysyła teraz drugi impuls ~INTA. Kontroler przerwań odpowiada na niego wystawieniem na szynę danych D0-D7 wektora przerwań o następującej budowie:

bit 7 |

bit 6 |

bit 5 |

bit 4 |

bit 3 |

bit 2 |

bit 1 |

bit 0 |

bity 7-3 bity te, stanowiące tzw. offset, można ustalić na etapie programowania kontrolera

bity 2-0 numer ustawionego w rejestrze ISR bitu.

Procesor traktuje ten bajt jako numer procedury obsługi przerwania, do wykonania której teraz przejdzie.

Jeżeli kontroler pracuje w tzw. trybie automatycznym (AEOI - Automatic End Of Interrupt), w momencie przejścia do wykonywania procedury obsługi przerwania zerowany jest odpowiedni bit rejestru ISR. W przeciwnym wypadku (tryb EOI) wyzerowania tego bitu dokonuje sama procedura obsługi przerwania wysyłając rozkaz EOI (End of Interrupt) do kontrolera. Tryb pracy kontrolera (AEOI/EOI) określany jest w fazie programowania.

Niezależnie od trybu pracy, moment wyzerowania bitu rejestru ISR odpowiadającego aktualnie obsługiwanemu kanałowi oznacza gotowość kontrolera do przyjęcia następnego zgłoszenia. Należy tu jeszcze raz podkreślić, że zgłoszenia nie są obsługiwane w miarę nadchodzenia, istotny natomiast jest ich priorytet. Oznacza to, że przy pełnej kolejce oczekujących na liniach IR1-7 zgłoszeń (bity 7-1 rejestru IRR ustawione) zarejestrowanie zgłoszenia na linii IR0 spowoduje zrealizowanie go w pierwszej kolejności, tj. po zakończeniu aktualnie wykonywanego cyklu obsługi.

Kaskadowe łączenie kontrolerów przerwań

Dla zwielokrotnienia liczby wejść układy 8259A dają się łączyć w grupy. Teoretycznie możliwe jest połączenie 9 układów (jeden Master + 8 układów Slave) i uzyskanie 8 x 8 = 64 linii przerwań. W modelach AT i PS/2 zastosowano kaskadowe połączenie dwóch kontrolerów uzyskując tym samym 8+7=15 wejść, bowiem jedno z wejść układu Master używane jest do dołączenie układu Slave. Należy zaznaczyć, że połączenie takie prowadzi do przegrupowania priorytetów wejść; w naszym przypadku wejścia IR8-15 (układu Slave) otrzymują wyższy priorytet niż wejścia IR3-7 układu Master.

Przyporządkowanie urządzeń liniom IRQ w modelach XT, AT i PS/2

Model XT |

|||||

Linia IRQ |

Urządzenie |

Wektor |

Linia IRQ |

Urządzenie |

Wektor |

0 |

Zegar systemowy |

08h |

4 |

COM1 |

0Ch |

1 |

Klawiatura |

09h |

5 |

Kontroler dysku twardego |

0Dh |

2 |

Zarezerwowane |

0Ah |

6 |

Kontroler dyskietek |

0Eh |

3 |

COM2 |

0Bh |

7 |

LPT1 |

0Fh |

Modele AT i PS/2 |

|||||

Linia IRQ |

Urządzenie |

Wektor |

Linia IRQ |

Urządzenie |

Wektor |

0 |

Zegar systemowy |

08h |

8 |

Zegar czasu rzeczywistego |

70h |

1 |

Klawiatura |

09h |

9 |

wolne |

71h |

2 |

Wejście dla układu Slave |

0Ah |

10 |

wolne |

72h |

3 |

COM2 |

0Bh |

11 |

wolne |

73h |

4 |

COM1 |

0Ch |

12 |

Mysz PS/2 |

74h |

5 |

Wolne lub LPT2 |

0Dh |

13 |

Koprocesor arytmetyczny |

75h |

6 |

Kontroler napędu dysków elastycznych |

0Eh |

14 |

1. kontroler dysku twardego |

76h |

7 |

LPT1 |

0Fh |

15 |

2. kontroler dysku twardego |

77h |

Wektor oznacza numer indeksu wskazującego adres procedury obsługi danego przerwania, umieszczony w tablicy wektorów przerwań, która znajduje się w pamięci w obszarze 00000h-003FFh i zawiera 4-bajtowe pozycje reprezentujące adresy procedur obsługi przerwania.

Układy połączone są między sobą trzema liniami adresowymi CAS0-CAS2, które dla kontrolera Master są wyjściami, a dla Slave wejściami. Każdy z kontrolerów rozpoznaje swoją rolę (Master lub Slave) badając poziom sygnału na wejściu ~SP/EN. Zero logiczne na tym wejściu konfiguruje układ jako Slave, a jedynka logiczna jako Master.

Do obydwu kaskadowo połączonych kontrolerów doprowadzony jest z procesora sygnał ~INTA, lecz tylko układ Master łączy się swoim wyjściem INT z wejściem INTR procesora.

Obsługa zgłaszanych przerwań przez tak połączone układy nieco się komplikuje. Przerwania nadchodzące bezpośrednio do układu Master, tj. pojawiające się na liniach IRQ0-IRQ1 i IRQ3-IRQ7 obsługiwane są tak, jak to opisano wcześniej. Odebranie zgłoszenia na linii n układu Slave (IRQ8-IRQ15) powoduje wyzwolenie reakcji opisanej poniżej.

Schemat kaskadowego połączenia dwóch układów 8259A

Fazy obsługi przerwań od układu Slave

Zgłoszenie ustawia bit n rejestru IRR w układzie Slave i powoduje, po opracowaniu priorytetów, wysłanie sygnału INT do układu Master.

Układ Master otrzymuje zgłoszenie na linii IR2, co powoduje ustawienie bitu 2 w jego rejestrze IRR.

Układ Master, opracowawszy priorytety własnych zgłoszeń, wysyła sygnał INT do procesora.

Procesor (jeżeli nie zablokowano obsługi przerwań sprzętowych) odpowiada pierwszym sygnałem ~INTA.

Układ Master adresuje liniami CAS0-CAS2 układ Slave odpowiadający za obsługę zgłoszonego przerwania.

W obu układach następuje jednoczesne przesunięcie bitu odpowiadającego obsługiwanemu kanałowi (bit 2 w układzie Master i bit n w układzie Slave) z rejestru IRR do rejestru ISR.

Drugi impuls ~INTA wygenerowany przez CPU nakazuje układowi Slave wystawienie na szynę danych (D0-D7) bajtu danych - wektora przerwań, traktowanego jako numer procedury obsługi przerwania zgłoszonego na linii n.

W trybie AEOI zerowane są rejestry ISR (bit n w układzie Slave i bit 2 w układzie Master). W trybie EOI procedura obsługi przerwania wysyła dwa sygnały EOI: jeden do układu Master i drugi do układu Slave.

Programowanie kontrolera przerwań

Tryb pracy układu 8259A ustalany jest programowo. Układ otrzymuje w fazie programowania 2 - 4 bajty konfiguracyjne ICW1 - ICW4 (Initialization Command Word), które decydują o późniejszym zachowaniu systemu obsługi przerwań. Programując układy 8259A, procesor komunikuje się z nimi przez następujące porty:

Model XT

Adres portu |

Dostępne rejestry |

Tryb dostępu |

020h |

IRR, ISR, wektor przerwań |

do odczytu |

|

ICW1, OCW2, OCW3 |

do zapisu |

021h |

IMR |

do odczytu |

|

ICW2, ICW3, ICW4, OCW1 |

do zapisu |

Model AT

Adres portu |

Dostępne rejestry |

Tryb dostępu |

020h dla linii IRQ0-IRQ7 |

IRR, ISR, wektor przerwań |

do odczytu |

|

ICW1, OCW2, OCW3 |

do zapisu |

0A0h dla linii IRQ8-IRQ15 |

IRR, ISR, wektor przerwań |

do odczytu |

|

ICW1, OCW2, OCW3 |

do zapisu |

021h dla linii IRQ0-IRQ7 |

IMR |

do odczytu |

|

ICW2, ICW3, ICW4, OCW1 |

do zapisu |

0A1h dla linii IRQ8-IRQ15 |

IMR |

do odczytu |

|

ICW2, ICW3, ICW4, OCW1 |

do zapisu |

Inicjowanie pracy układu

Procesor przekazuje przez port 020h (Master) lub 0A0h (Slave) pierwszy bajt inicjujący ICW1.

Bajt ICW1:

0 |

0 |

0 |

1 |

bit 3 |

0 |

bit 1 |

bit 0 |

bity 7-4 0001, sygnatura rozkazu

bit 3 1 - oznacza wyzwalanie wejść IRQ poziomem napięcia,

0 - wyzwalanie zboczem (zmianą poziomu sygnału z 0 na l - ten tryb pracy jest powszechnie stosowany w PC)

bit 2 0

bit l l - oznacza pojedynczy układ (XT),

0 - obecność kaskady układów (AT lub PS/2)

bit 0 l - oznacza, że będzie wysłany bajt ICW4,

0 - oznacza brak bajtu ICW4

• Procesor przekazuje przez port 021 h (Master) lub 0A1h (Slave) drugi bajt inicjujący ICW2.

Bajt ICW2:

bit 7 |

bit 6 |

bit 5 |

bit 4 |

bit 3 |

0 |

0 |

0 |

bity 7-3 przemieszczenie (offset) wektora przerwań

bity 2-0 000.

Jeżeli w systemie obecne są dwa układy 8259A (decyduje o tym bit 1 bajtu ICW1), procesor wysyła trzeci bajt inicjujący ICW3. Budowa tego bajtu jest różna dla układu Master i Slave.

Bajt ICW3 (Master):

bit 7 |

bit 6 |

bit 5 |

bit 4 |

bit 3 |

bit 2 |

bit 1 |

bit 0 |

bity 7-0 jedynka na pozycji n oznacza, że wejście n połączone jest z wyjściem INT układu Slave. Zero na tej pozycji oznacza, że wejście n jest wolne lub połączone z obsługiwanym urządzeniem.

Bajt ICW3 (Slave):

0 |

0 |

0 |

0 |

0 |

bit 2 |

bit 1 |

bit 0 |

bity 7- 3 00000

bity 2-0 zakodowany dwójkowo numer wejścia układu Master, które jest połączone z wyjściem INT układu Slave. Nadaje to układowi Slave numer identyfikacyjny, który jest porównywany z adresem ustawianym przez układ Master na liniach CAS0-CAS2. Uaktywnia się więc tylko adresowany układ. Jest to rozwiązanie ogólne stosowane w dużych systemach; w PC adresowany jest i tak tylko jeden układ Slave.

• Kontroler oczekuje teraz bajtu ICW4, jeżeli zostało to zaanonsowane w bajcie ICW1 (bit 0).

Bajt ICW4

0 |

0 |

0 |

bit 4 |

bit 3 |

bit 2 |

bit 1 |

bit 0 |

bity 7-5 000

bit 4 w komputerach PC/XT/AT i PS/2 zawsze zero. Jedynka na tej pozycji modyfikuje sposób klasyfikacji priorytetów, co ma zastosowanie w wielokrotnych kaskadowych połączeniach kontrolerów, spotykanych w dużych systemach

bit 3 wartość l oznacza buforowany tryb pracy; końcówka ~SP/EN układu 8259A przestaje być wtedy wejściem przełączającym tryb pracy Master/Slave i staje się wyjściem sterującym zewnętrznym buforem szyn systemowych. Ta możliwość znajduje zastosowanie wyłącznie w dużych systemach z silnie obciążonymi magistralami systemowymi

bit 2 l = Master, 0 = Slave. Bit ten używany jest do programowego konfigurowania danego układu jako Master lub Slave w sytuacji gdy ustawiony jest bit 3 i nie ma możliwości używania do tego celu końcówki ~SP/EN

bit l jedynka oznacza tryb AEOI, tj. automatyczne zerowanie odpowiedniego bitu rejestru ISR w momencie przekazania sterowania do procedury obsługi przerwania. Wartość 0 oznacza, że procedura obsługi przerwania sama musi się zatroszczyć o wyzerowanie tego bitu wysyłając rozkaz EOI do kontrolera (lub kontrolerów, jeżeli przerwanie pochodzi od układu Slave)

bit 0 1 - oznacza normalny tryb pracy, dostosowany do procesorów 8086/88; po drugim impulsie ~INTA procesorowi przekazywany jest 8-bitowy wektor przerwań.

0- na tym bicie przełącza układ w tryb 16-bitowy, tj. 8259A wysyła bezpośrednio 16-bitowy adres procedury obsługi przerwania (a nie 8-bitowy numer, który jest dopiero indeksem w tablicy adresów) w porcjach po osiem bitów - wystawienie drugiej połowy adresu wyzwalane jest wtedy trzecim impulsem ~INTA pochodzącym od CPU.

Opisane powyżej polecenia zawarte w bajtach ICW1 - ICW4 zapewniają konfigurowanie układu jeszcze przed rozpoczęciem obsługi zgłoszeń. Konfigurację kontrolera przerwań przeprowadzają procedury inicjalizacyjne BIOS-u wykonywane po włączeniu komputera jeszcze przed załadowaniem systemu operacyjnego.

Istnieją też rozkazy, które można przekazywać kontrolerowi podczas jego pracy modyfikując tym samym dynamicznie system obsługi przerwań stosownie do bieżących potrzeb. Układ 8259A rozpoznaje trzy rozkazy OCW1 - OCW3 (Operation Control Word)

• Rozkaz OCW1 podawany jest przez port 021h (dla układu Master) lub 0A1h (Slave):

bit 7 |

bit 6 |

bit 5 |

bit 4 |

bit 3 |

bit 2 |

bit 1 |

bit 0 |

bity 7-0 jedynka na pozycji bitowej n maskuje (blokuje) linię zgłoszeń n.

• Rozkaz OCW2 podawany jest przez port 020h (dla układu Master) lub 0A0h (Slave):

bit 7 |

bit 6 |

bit 5 |

0 |

0 |

bit 2 |

bit 1 |

bit 0 |

bity 7-5 001 - nie adresowany rozkaz EOI

011 - adresowany rozkaz EOI; powoduje wyzerowanie w rejestrze ISR pozycji bitowej adresowanej bitami 2-0, pozostałe kombinacje bitów 7-5 mają zastosowanie w dużych systemach, gdzie obsługiwanych jest wiele urządzeń o jednakowym priorytecie (decyduje wówczas kolejność zgłoszeń).

bity 4-3 00, sygnatura rozkazu

bity 2-0 Zakodowany dwójkowo numer linii, której dotyczy polecenie EOI.

Rozkaz OCW3 podawany jest przez port 020h (układ Master) lub 0A0h (Slave)

0 |

bit 6 |

bit 5 |

0 |

1 |

bit 2 |

bit 1 |

bit 0 |

bit 7 0

bity 6-5 10 - wyzerowanie maski specjalnej,

11 - ustawienie maski specjalnej, pozostałe kombinacje bitów 6 - 5 są ignorowane

bity 4-3 01 - sygnatura rozkazu

bit 2 1 - polling

bity 1-0 10 - rozkaz odczytu rejestru IRR; kontroler wystawia do portu 020h (Master) lub 0A0h (Slave) zawartość rejestru IRR,

11 - rozkaz odczytu rejestru ISR; kontroler wystawia do portu 020h (Master) lub 0A0h (Slave) zawartość rejestru ISR

Pozostałe kombinacje bitów 0 i 1 są ignorowane.

Polling

Istnieje również inna forma przekazywania informacji pomiędzy kontrolerem przerwań a procesorem - tzw. polling. Końcówka ~INTA układu 8259A nie może być wtedy połączona z wyjściem ~INTA procesora, można więc to wejście wykorzystać inaczej. Wysłanie przez procesor rozkazu OCW3 z ustawionym bitem 2 oznacza skierowanie zapytania do kontrolera (polling). Układ 8259A odpowiada wystawieniem do tego samego portu, z którego otrzymał rozkaz OCW3, bajtu danych o następującej strukturze:

bit 7 |

x |

x |

x |

x |

bit 2 |

bit 1 |

bit 0 |

bit 7 l - istnieje zgłoszenie oczekujące na obsługę,

0 - brak zgłoszeń

bity 6-3 nie używane

bity 2-0 zakodowany binarnie numer linii, na której oczekuje zgłoszenie.

Każdy rozkaz odczytu portu jest traktowany jako sygnał uzgodnienia (odpowiednik sprzętowego sygnału ~INTA) od procesora.

Przerwanie niemaskowalne (NMI)

Przerwanie to również zaliczane jest do grupy przerwań sprzętowych, bowiem nie można go wygenerować instrukcją kodu maszynowego. W przeciwieństwie do przerwań odbieranych liniami IRQ, które obsługiwane są przez dedykowany do tego celu kontroler 8259A, sygnał przerwania NMI kierowany jest bezpośrednio do końcówki NMI procesora. Wysoki sygnał logiczny na tym wejściu prowadzi, natychmiast po zakończeniu wykonywania bieżącego rozkazu, do wywołania procedury INT 2. Przerwanie takie nie może być zamaskowane ani rozkazem procesora, ani przez operacje na rejestrze IMR kontrolera 8259A. Ma ono najwyższy priorytet ze wszystkich przerwań sprzętowych.

Wywołanie przerwania NMI w przypadku komputerów PC ma miejsce po stwierdzeniu błędu parzystości pamięci operacyjnej, co należy uznać za sytuację uniemożliwiającą dalsze użytkowanie komputera. Procedura obsługi INT 2 wyprowadza na monitor stosowny komunikat i wstrzymuje pracę systemu. Jedynym wyjściem w tym momencie jest ponowny restart systemu w nadziei, że błąd parzystości spowodowany został na przykład chwilową utratą styku lub przegrzaniem modułów RAM, a nie ich trwałym uszkodzeniem. Źródłem tego przerwania może też być sygnał generowany przez uszkodzony koprocesor arytmetyczny.

Przerwanie niemaskowalne, nie jest „absolutnie nie do zamaskowania". Rozpatrzmy moment włączenia komputera i uruchomienia procedur inicjalizujących BIOS-u. Jednym z ich zadań jest budowa tablicy wektorów przerwań, tj. stałego miejsca w „niskim" obszarze pamięci operacyjnej, w którym umieszczane są czterobajtowe adresy punktów wejścia do procedur obsługi wszystkich przerwań. Jednocześnie inicjalizowane są wszystkie inne rejestry systemu. Własną inicjalizację przeprowadzają układy obsługi pamięci dynamicznej. Może się zdarzyć, że układ kontroli parzystości RAM stwierdzi błąd i wywoła tym samym procedurę obsługi przerwania INT 2. Adres punktu wejścia do tej procedury może jednak nie być jeszcze ustawiony i wskazywać przypadkowe miejsce w pamięci. Procesor, podejmując wykonanie programu od tego miejsca, najprawdopodobniej zawiesi się. Jedną z pierwszych operacji, jakie musi wykonać BIOS uruchamiając komputer, jest więc zamaskowanie przerwania NMI. Odpowiada to ustawieniu bitu 7 portu o adresie 0A0h (w XT) lub 070h (w AT). Manipulując samodzielnie tym bitem należy zachować szczególną ostrożność - port ten bowiem steruje również pracą pamięci konfiguracji CMOS-RAM.

Bezpiecznie można to zrobić w następujący sposób, pokazany w języku C:

unsigned char i;

i = inp(0x70);

i = i & 0x7f; // wyzeruj bit 7, NMI aktywne

outp(0x70,i);

i = inp(0x70);

i = i | 0x80; // ustaw bit 7, NMI zablokowane

outp (0x70,i);

Przykład programu w języku C maskującego kanał 0, co powoduje zatrzymanie procesu odmierzania czasu systemowego.

#include <dos.h>

#include <conio.h>

#include <stdio.h>

void zegar (void) // pokazuje czas i czeka na naciśnięcie klawisza

{

struct time czas;

while( ! kbhit ( ) )

{

gettime (&czas);

gotoxy (10, 10);

printf ("%02i:%02i:%02i", czas. ti_hour, czas. ti_min, czas. ti_sec) ;

}

getch( );

}

void main(void)

{

clrscr () ;

zegar () ;

outp (0x21, 0x01) ; // zamaskowany kanał 0 -> zatrzymaj zegar

zegar () ;

outp (0x21, 0x00) ; // uruchom zegar

zegar () ;

}

Wyszukiwarka

Podobne podstrony:

referat TM, WAT, semestr IV, Systemy wbudowane

ściąga(1), WAT, semestr IV, Systemy wbudowane

kody, WAT, semestr IV, Systemy wbudowane

Egzamin6, WAT, semestr IV, Systemy wbudowane

Mikrokontroler 8051(1), WAT, semestr IV, Systemy wbudowane

Sylabus(1), WAT, semestr IV, Systemy wbudowane

arch powerPC, WAT, semestr IV, Systemy wbudowane

Przerwania, WAT, semestr IV, Systemy wbudowane

1AlfabetStasiaka, WAT, semestr IV, Systemy wbudowane

swb-sciaga, WAT, semestr IV, Systemy wbudowane

system przerwan, WAT, semestr IV, Systemy wbudowane

ściąga(1), WAT, semestr IV, Systemy wbudowane

Sprawko swb, WAT, semestr IV, Systemy wbudowane

Przeglad ukladow graficznych ATI, WAT, semestr IV, Systemy wbudowane

odpowiedzi egzamin, Informatyka WEEIA 2010-2015, Semestr IV, Systemy Wbudowane, Inne, egzamin

więcej podobnych podstron