1Uklad scalony - mikrominiaturowy uklad elektroniczny charakteryzujacy się tym ze wszystkie lub czesc elementow wraz z polaczeniami sa wykonane nierozlaczalnie w 1 cyklu technologicznym.

PODZIAL:

-warstwowe(element sa scalane na powieazchni podloza)

-hybrydowe(dolaczenie delementow aktywnych do ukladow warstwowych)

-monokrystaliczne(wszystkie elementy czynnne i bierne scalone w 1 strukturze)

2SYSTEM PRZERWAŃ:

Mikroprocesor obsluguje przerwanie w okreslonym cyklu:

-procesor po uzyskaniu przerwania identyfikuje jego numer,

-odklada do stosu zawartosc rejestru flagowego iadres powrotny

-ustala adres procedury obslugi przerwania laduje go do rejestu IP

-konczy procedure przerwania instrukcja IRET

3Adresowanie ukladow we-wy:

-jednolite adresowanieukladow pamieci iukladow we-wy

-oddzielne -II-

Mikroprocesor - uklad cyfrowy o wysokim stopniu scalenia zdolnym do wykonywania operacji cyfrowych według dostarczonych mu instrukcji.jest przeznaczony do przetwarzania informacji poprzez realizację sekwencji elementarnych operacji które należą do zbioru zwanego listą rozkazów.

4SYSTEM MIKROPROCESOROWY:

W prawie każdym mikroprocesorze można wyróżnić trzy podstawowe bloki:

blok wykonawczy

blok sterujący

blok magistral

Blok wykonawczy składa się z zespołów:

ALU - jednostka arytmetyczno-logiczna (Arithmetic Logic Unit) - wykonuje operacje logiczne na dostarczonych jej danych; warunkuje moc obliczeniową mikroprocesora;

akumulatora - rejestr, wykorzystywany przez ALU; z akumulatora pobierany jest argument i do niego zapisywany jest wynik operacji.

4Blok sterujący zbudowany jest z:

licznika rozkazów - rejestr, wskazujący adres rozkazu, który ma zostać pobrany i wykonany przez mikroprocesor; stan licznika jest automatycznie zwiększany o 1, po pobraniu rozkazu (inkrementacja stanu licznika);

dekodera rozkazów - służy do dekodowania rozkazów i przesyłania odpowiednich sygnałów sterujących do mikroprocesora.

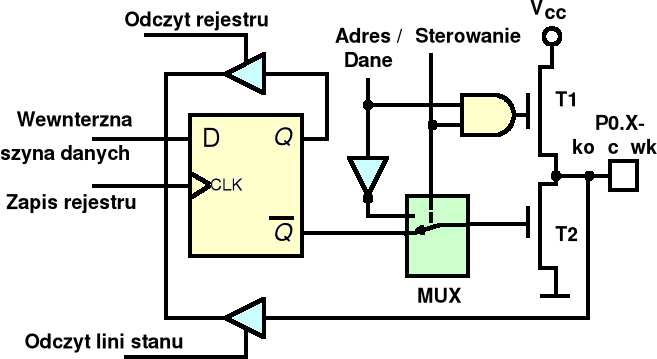

5Blok magistral służy do komunikacji pomiędzy poszczególnymi zespołami, jak również komunikacji z otoczeniem. Wyróżnia się magistrale:

magistrala wewnętrzna - służy do komunikacji wewnątrz struktury logicznej mikroprocesora i użytkownik nie ma do niej dostępu;

magistrala danych - jest dwukierunkową szyna, przekazująca sygnały reprezentujące dane lub rozkazy pomiędzy jednostką centralną (CPU) a pamięciami lub układami we/wy;

magistrala sterująca - dwukierunkowa szyna, przesyłająca sygnały zapewniające pracę mikroprocesora; m.in. przesyła sygnał taktujący mikroprocesor, lub sygnał zapisu do- i odczytu z pamięci;

magistrala adresowa - jednokierunkowa szyna, na którą wystawiany jest adres komórki pamięci, w której znajduje się informacja do odczytu lub do której ma ona być zapisana

Zasada działania mikroprocesora (cykl rozkazowy)

6 Cykl rozkazowy mikroprocesora:

do licznika rozkazów zapisywany jest adres pierwszego rozkazu do wykonania;

wysłanie na szynę adresową zawartości licznika rozkazów;

kod rozkazu jest pobierany z pamięci i przez szynę danych przesyłany jest do

rejestru a następnie - dekodera rozkazów;

licznik rozkazów zwiększany jest o 1 (I faza cyklu rozkazowego - pobranie rozkazu);

w dekoderze następuje zdekodowanie rozkazu;

wygenerowanie (przez CU) odpowiednich sygnałów sterujących pracą mikroprocesora (II faza cyklu - operacje wewnętrzne);

wykonanie rozkazu (III faza cyklu).

7 MIKROPROCESOR JEDNOUKŁADOWY:

To autonomiczny układ scalony z wyspecjalizowanym mikroprocesorem, pamieciami RAM ROM oraz układami WE/WY zintegrowanymi w jednej obudowie.

ROM - nie zapisywalna pamięć, przez-naczona tylko do odczytu (Read Only Memory) - przechowywanie kodów rozkazów, wykonywanych przez mikro-procesor

RAM - pamięć o swobodnym dostępie (Random Access Memory), dostępna dla użytkownika, przeznaczona do zapisu i odczytu danych i wyników operacji wykonywanych przez mikroprocesor

Urządzenia wejścia / wyjścia ( monitory, wyświetlacze, drukarki, klawiatury, myszki), służą do dwukierunkowej komunikacji pomiędzy systemem a użytkownikiem. Są obsługiwane za pomocą specjalnych układów wejścia / wyjścia, które przekazują i wzmacniają odpowiednie sygnały, sterujące pracą tych urządzeń.

Zegar - służy do taktowania bloków mikroprocesora za pomocą impulsów.

8 Ortogonalność - unifikacja instrukcji według następujących zasad:

każda instrukcja może operować na dowolnym rejestrze roboczym; procesor nie ma więc wyróżnionych rejestrów, które są specjalizowane do wykonywania określonych rodzajów operacji;

każda instrukcja może wykorzystywać dowolny tryb adresowania argumentów;

nie ma ukrytych związków między instrukcjami (efektów ubocznych), które powodowałyby nieprzewidziane reakcje systemu w zależności od kontekstu użycia rozkazów w programie;

kody rozkazów i formaty instrukcji są zunifikowane; w szczególności wszystkie instrukcje zajmują w pamięci programu taką samą liczbę bajtów;

ortogonalność zbioru instrukcji radykalnie upraszcza budowę układu sterowania, który może realizować cykl wykonania każdego rozkazu według identycznego algorytmu; stąd prostszy układ sterowania może pracować znacznie szybciej, dlatego cykl rozkazowy ulega skróceniu.

9 Podział ARCHITEKTURY PROCESORA ze względu na mapę pamięci:

Von-Neumanna (klasyczna);

Harwardzką;

zmodyfikowaną harwardzką.

10 Architekturę Von-Neumana charakteryzuje:

jednolita przestrzeń adresowa, w której umieszczone są wszystkie pamięci, rejestry i układy we/wy;

podział przestrzeni adresowej na pamięć programu, pamięć danych oraz obszar we/wy jest czysto umowny i zależy wyłącznie od rozmieszczenia tych elementów w obszarze adresowym podczas projektowania systemu;

jedna szyna danych - wspólna dla danych i programu;

ułatwione programowanie, gdyż dostęp do danych, programu i urządzeń we/wy odbywa się przy użyciu zunifikowanych rozkazów wykorzystujących te same tryby adresowania nie istnieje tu potrzeba wprowadzania specjalnych rozkazów pozwalających na przepływ danych pomiędzy pamięcią ROM i RAM.

11 Architekturę harwardzką charakteryzuje:

rozdzielenie obszarów adresowych pamięci danych i programu (wewnętrznych i czasami zewnętrznych);

użycie dwóch oddzielnych szyn dla danych i rozkazów, dzięki czemu w trakcie pobierania argumentów wykonywanej właśnie instrukcji można równocześnie zacząć pobieranie następnego słowa rozkazowego (pre-fetch); skraca to cykl rozkazowy i zwiększa szybkość pracy;

niejednoznaczność adresów, ponieważ są one takie same w pamięć RAM i ROM;

zastosowanie różnych rozkazów dla pamięci programu i dla pamięci danych;

różna szerokość (długość słowa) magistrali danych i rozkazów;

utrudniony przepływ danych z pamięci programu do obszaru pamięci operacyjnej, co uniemożliwia stosowanie jednej z podstawowych technik programistycznych (look-up tables) - nie jest możliwe indeksowane przesłanie danych z pamięci ROM do RAM.

12 Zmodyfikowana architektura harwardzka

Zmodyfikowana architektura harwardzka jest rozwiązaniem pośrednim, łączącym zalety architektury harwardzkiej i Von-Neumanna. Charakteryzuje się następującymi cechami:

obszary pamięci ROM i RAM są rozdzielone, ale charakteryzują się taką samą długością słowa;

przesyłanie stałych z pamięci ROM do rejestrów i pamięci RAM - możliwe jest dzięki multiplekserom MUX i odpowiedniej organizacji magistrali pamięci ROM i RAM;

jedynym rejestrem niewidocznym jako komórka pamięci RAM jest rejestr akumulatora;

w procesorze istnieje możliwość budowy stałych tablic wektorów w pamięci ROM, co pozwala na budowę szybkich algorytmów dekodowania złożonych struktur danych.

13Podział ARCHITEKTURY PROCESORA ze względu na typ listy instrukcji:

CISC (complex instruction set computer);

RISC (reduced instruction set computer).

Architektura CISC charakteryzuje się następującymi własnościami:

rozbudowaną liczbą instrukcji (często powyżej 100);

niezachowaniem cechy ortogonalności;

wąskim wyspecjalizowaniem instrukcji, współpracujących na ogół tylko z określonymi rejestrami i wymagających stosowania określonych trybów adresowania.

Architektura RISC jest rozwiązaniem o zredukowanej liście instrukcji,

odznacza się następującymi cechami:

procesor jest zbudowany zgodnie z architekturą harwardzką;

procesor wykorzystuje przetwarzanie potokowe (pipeling) w celu zwiększenia szybkości wykonywania programu;

zbiór realizowanych instrukcji jest ograniczony i spełnia warunki ortogonalności (symetrii);

w procesorze tego typu zamiast prostego rejestru instrukcji stosuje się pamięć FIFO (first-in first-out), która gromadzi kolejkę instrukcji; instrukcje pobierane z pamięci programu do kolejki w cyklu pre-fetch opuszczają ją w takiej samej kolejności i są kierowane do poszczególnych układów wykonawczych.

14 Charakterystyka przetwarzania potokowego (PIPELINING):

Jeden z układów procesora potokowego wykonuje rozkaz, a drugi, niezależny układ w tym samym czasie pobiera następny rozkaz z pamięci, co podwaja wydajność procesora. Stopień równoległości konstrukcji procesorów wynosi od trzech do siedmiu niezależnych bloków funkcjonalnych wykonujących jednocześnie pobranie rozkazu, jego zdekodowanie, obliczenie adresu argumentu, pobranie argumentu, wykonanie operacji i przechowanie wyniku.

Potokowa architektura procesora jest bardzo wydajna, gdy nie występują przerwania, instrukcje warunkowe oraz przede wszystkim skoki, bowiem jest ona bardzo wrażliwa na nie.

Arytmetyka przetwarzania potokowego

Podstawowe parametry charakteryzujące przetwarzanie potokowe:

k - ilość etapów na jakie dzieli się wykonanie każdego rozkazu

n - ilość wykonanych rozkazów

f - częstotliwość taktowania

całkowity czas wykonania programu bez przetwarzania potokowego:

Ts=nk*1/f

całkowity czas wykonania programu z potokowaniem:

Tp=k/f+(n-1)/f

k/f - to czas po jakim pierwszy rozkaz zostanie wykonany

(n-1)/f - czas wykonania reszty rozkazów

współczynnik przyspieszenia - zależy od ilości stopni w potoku

S=Ts/Tp=nk/(k+(n-1))

Ograniczenia przetwarzania potokowego

Podstawowe ograniczenia występujące w przetwarzaniu potokowym:

częstotliwość uzyskiwania wyników jest ograniczona przez czas trwania najdłuższego z etapów;

rozwiązanie gdzie dodatkowo dzielone są etapy na mniejsze części nazywane jest przetwarzaniem superpotokowym (superpipelined pipeline lub superpipelining);

dodatkowe przyspieszenie przetwarzania można uzyskać dzięki współbieżnemu wykonywaniu rozkazów w bliźniaczych potokach. Taki rodzaj potokowania nazywa się potokowaniem superskalarnym;

Typy zakłóceń

W przetwarzaniu potokowym występują następujące zakłócenia:

hazardy strukturalne - wynikają z konfliktów sprzętowych, niektóre kombinacje instrukcji nie mogą być wykonywane jednocześnie ze względu na konflikt zasobów

hazardy danych - pojawiają się wtedy, gdy do obiektu danych (rejestry, komórki pamięci, rejestry flag) zwracają się lub zmieniają go dwa różne rozkazy umieszczone tak blisko w programie, że potokowanie powoduje zachodzenie na siebie ich wykonań. Wśród hazardów danych także wyróżnia się trzy typy:

czytanie po zapisie (Read after Write) - RAW

zapis po odczycie (Write after Read) - WAR

zapis po zapisie (Write after Write) - WAW

Sposoby usuwania zakłóceń

Zatrzymanie potoku - jeżeli ujawniono rozkaz j-ty, który znajduje się w stanie zakłócenia z wcześniejszym rozkazem i-tym, to wszystkie kolejne rozkazy są zatrzymane dopóki rozkaz i-ty nie przejdzie przez punkt krytyczny konfliktu;

Zatrzymanie rozkazu j-tego - jeżeli rozkazy j+1, j+2 są wprowadzone do potoku, i powstaje możliwość wyprzedzenia rozkazu j-tego; przy badaniach na istnienie zakłóceń dla rozkazów j+1, j+2 należy również przewidzieć, czy nie ma konfliktów z rozkazem j-tym. Jeżeli takie zakłócenie zostanie wykryte, to wykonanie tych rozkazów (j+1, j+2) jest także wstrzymane aż do momentu, gdy rozkaz j-ty nie otrzyma zezwolenia na kontynuowanie przejścia przez potok.

15 System mikroprocesorowy - samodzielny układ mikroprocesora, współpracujących z nim pamięci oraz urządzeń wejścia-wyjścia.

Klasyfikacja pamięci

SYSTEM PRZERWAŃ

Mikroprocesor obsługuje przerwanie w określonym cyklu:

procesor po uzyskaniu zgłoszenia przerwania identyfikuje jego numer

odkłada do stosu zawartość rejestru flagowego i adres powrotny

ustala adres procedury obsługi przerwania, ładuje go do rejestru IP

kończy procedurę przerwania instrukcją IRET

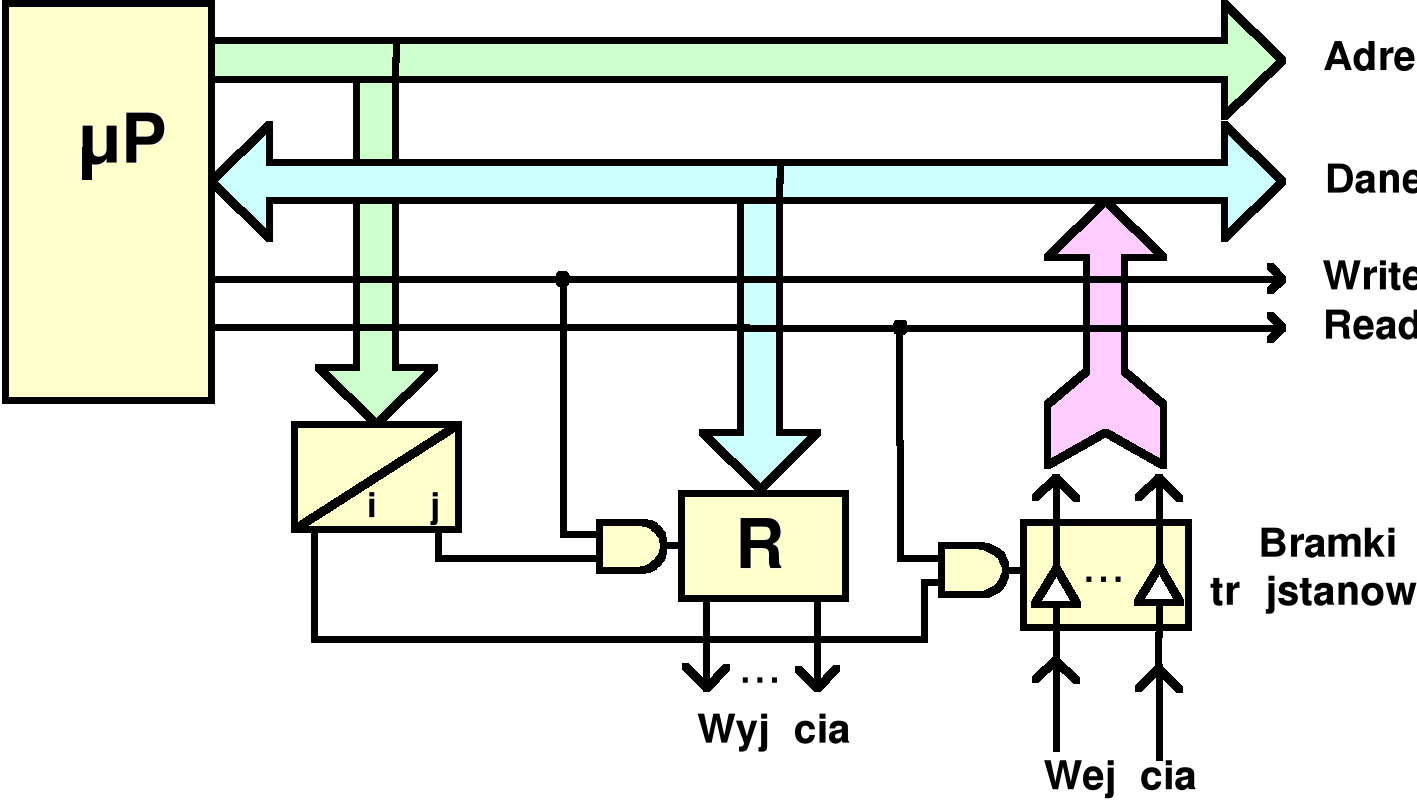

Układy wejścia - wyjścia

służą do wymiany danych między procesorem i pamięcią operacyjną a urządzeniami zewnętrznymi. Procesor jest połączony z układami wejścia - wyjścia i z pamięcią operacyjną za pomocą magistrali wejścia - wyjścia, w skład której wchodzą : magistrale danych, adresów i sterowania - liczba linii poszczególnych magistral jest różna dla różnych procesorów.

16 Podstawowe typy układów wejścia - wyjścia:

Układy transmisji szeregowej:

Transmisja szeregowa może odbywać się w dwojaki sposób:

Transmisja synchroniczna

Transmisja asynchroniczna

Specjalne układy wykorzystywane do transmisji szeregowej:

UART - (Universal Asynchronous Recever-Transmitter) - układ asynchr. nadajnika-odbiornika

USRT - układ synchronicznego nadajnika-odbiornika

USART - uniwersalny układ synchronicznego-asynchronicznego odbiornika-nadajnika.

Układy transmisji równoległej:

Układy proste

Układy programowe

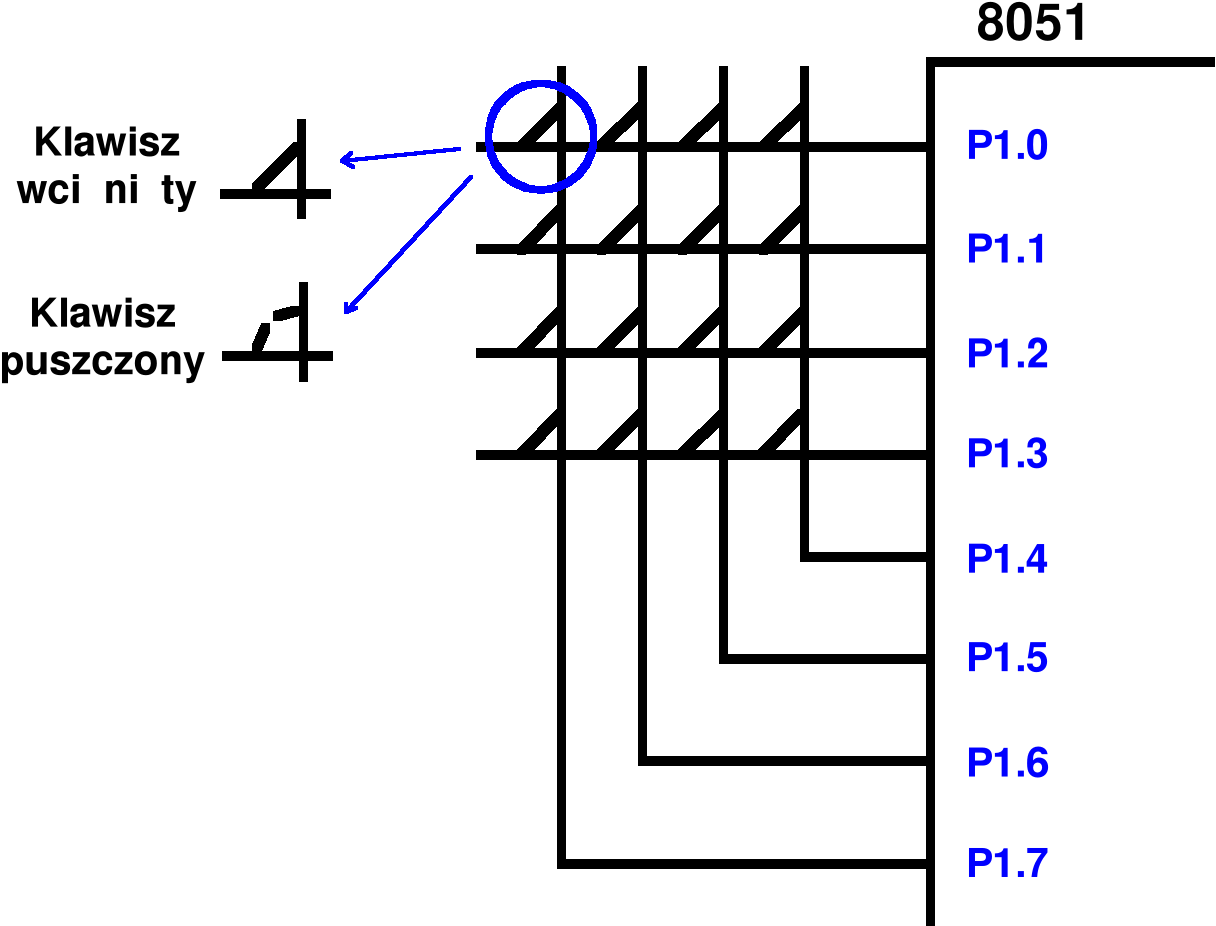

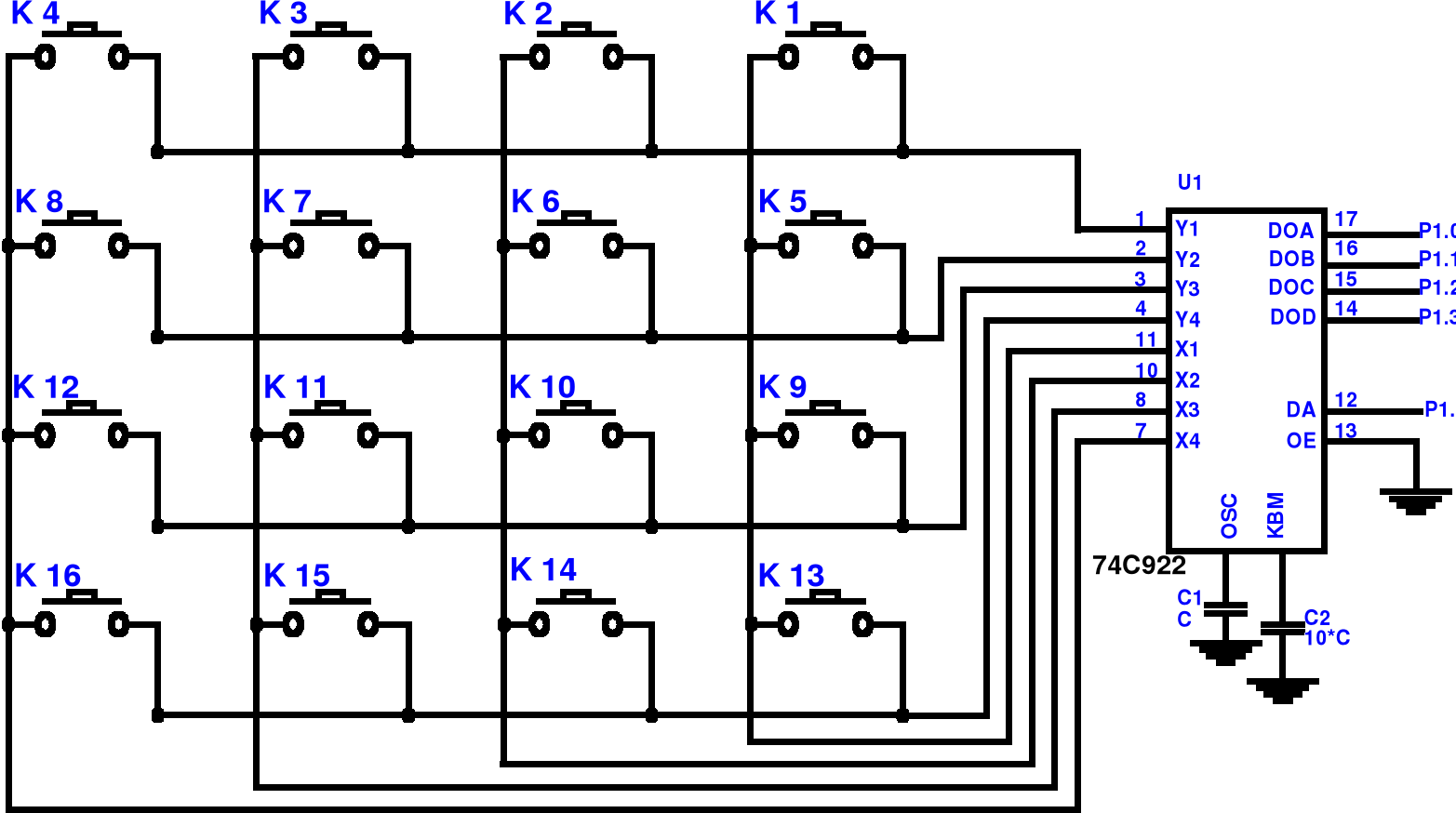

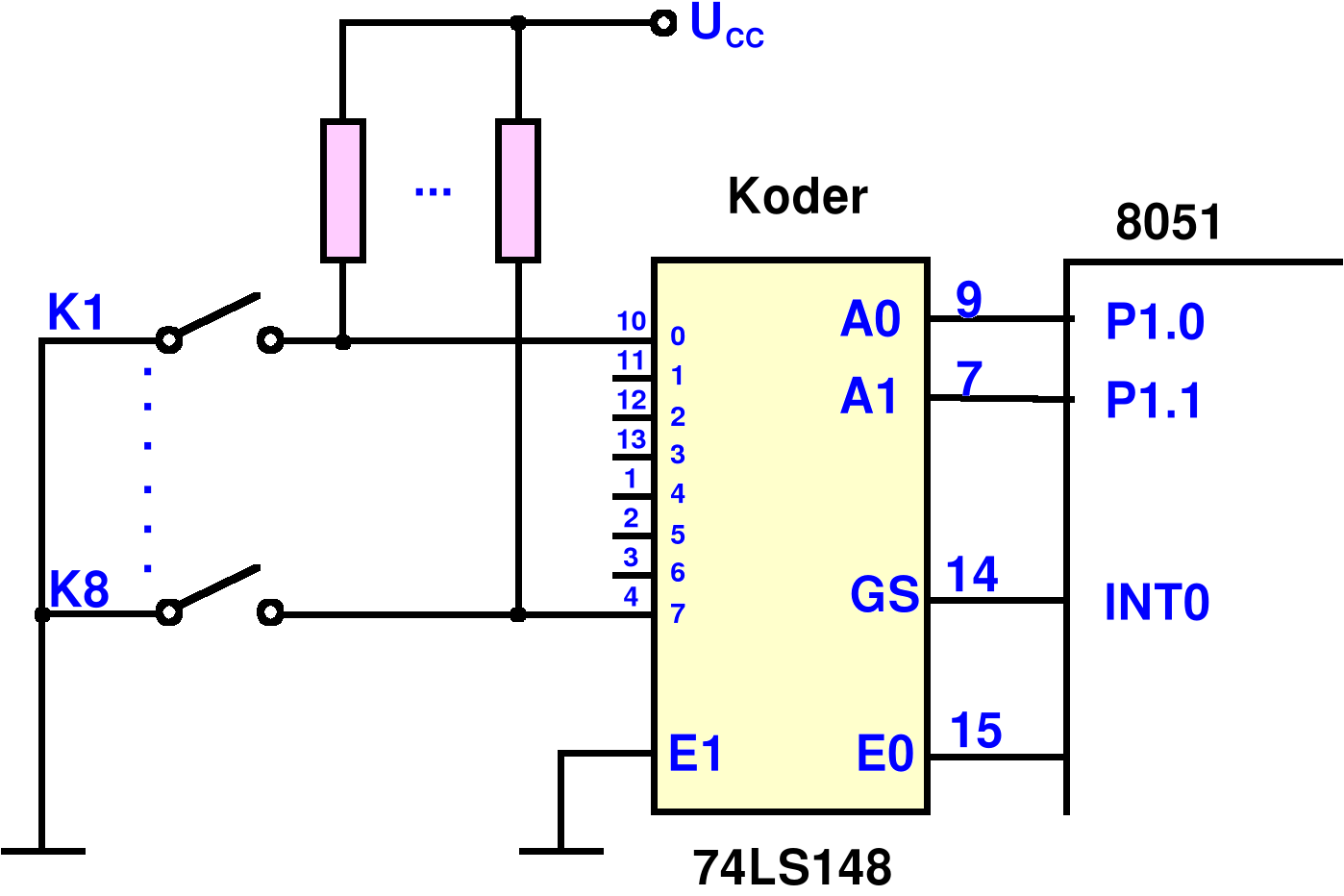

17 KLAWIATURY

Jednym z najważniejszych układów do wprowadzania danych i poleceń sterujących

przez użytkownika do pamięci mikrokontrolera jest klawiatura. Klawiatura może być

zbudowana jako połączenie kilku przycisków wspólnym końcem lub poszczególne

przyciski mogą być zorganizowane w postaci matrycy. W zależności od dostępności

portów wejściowych i wymaganej liczby klawiszy stosuje się różnego rodzaju układy

wejściowe.

Ogólny podział klawiatur, ze względu na technologię "wciskania klawiszy":

Mechaniczne

Foliowe

Pojemnościowe

Hallotronowe i Kontaktronowe

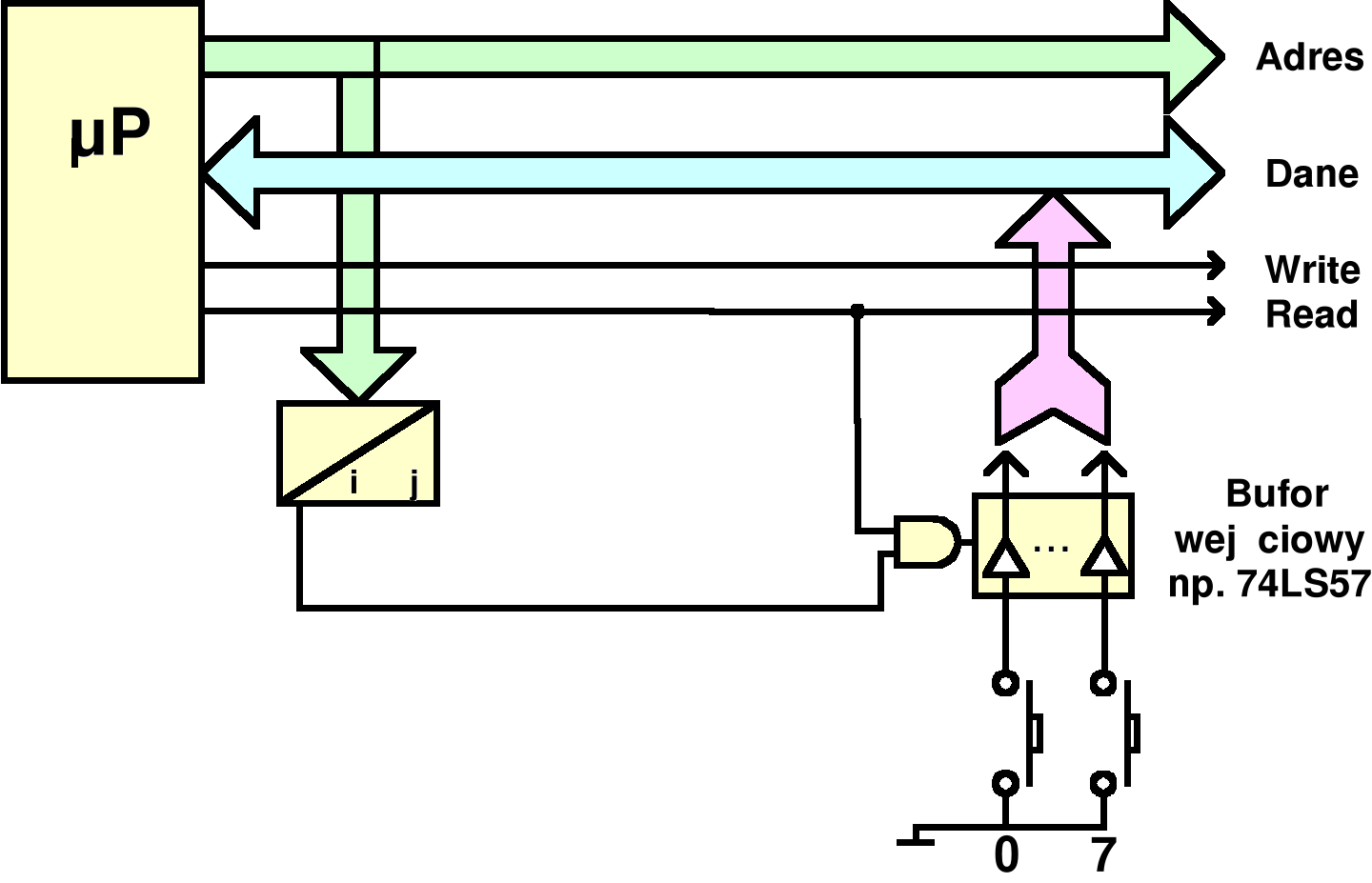

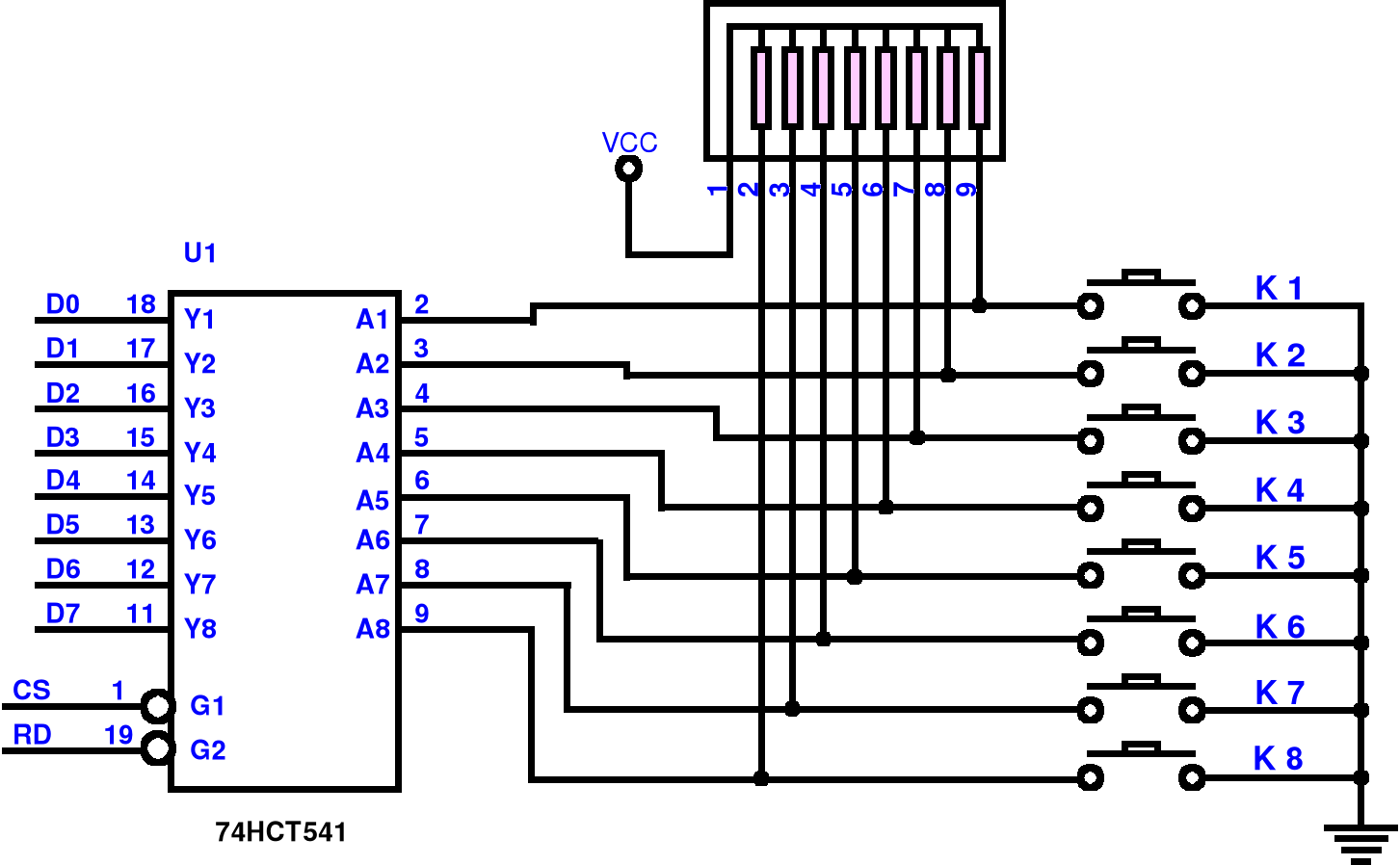

Dołączanie klawiatury do magistrali danych poprzez bufor wejściowy

Najprostszy sposób dołączania klawiatury do mikroprocesora - do wolnego portu

Z zastosowaniem rezystorów podciągających

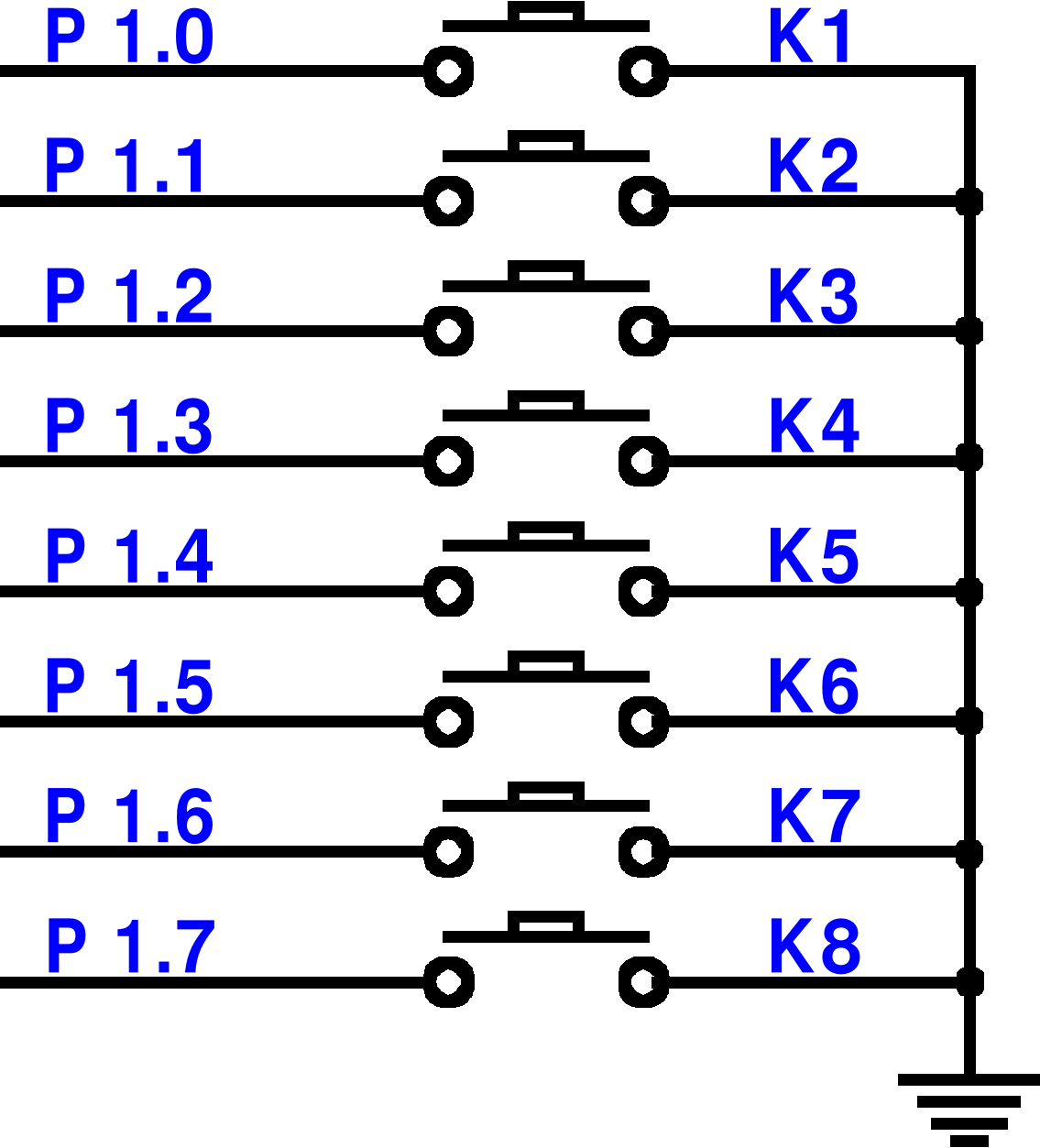

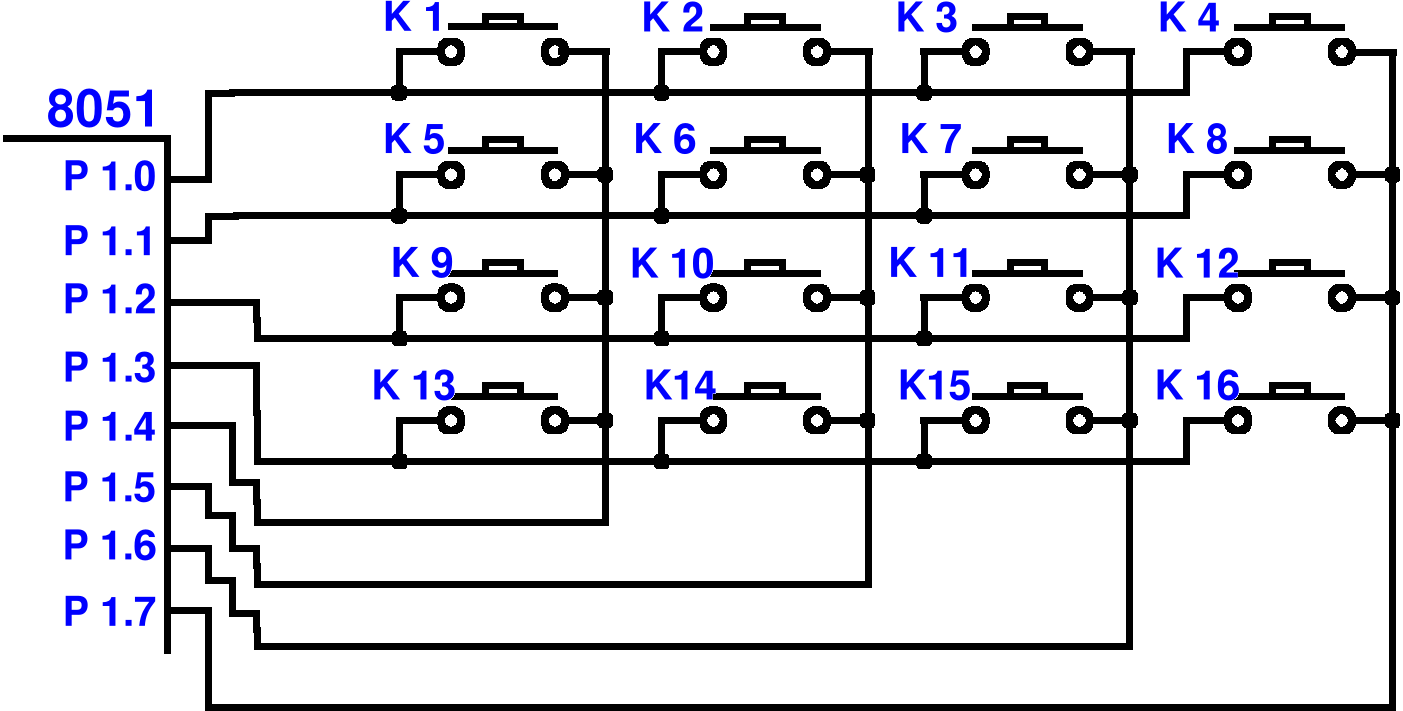

Klawiatura Matrycowa - zmniejszenie liczby linii we/wy kosztem komplikacji

procedur programowych

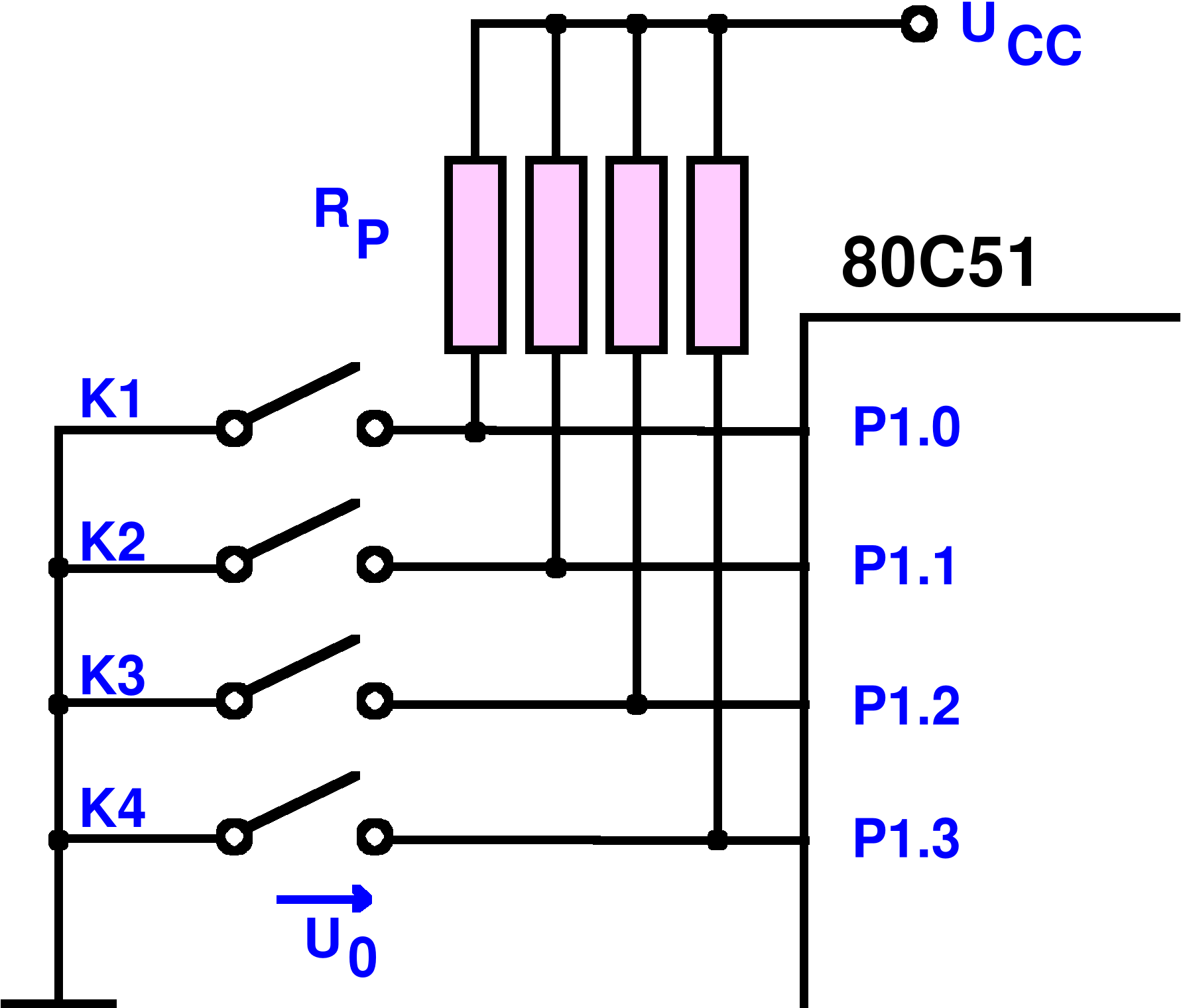

Port P1 ma tzw. wewnętrzne rezystory podciągające ( pull-up ). Dzięki tej

właściwości można dołączyć klawiaturę 8-stykową lub matrycową 4x4

Program do obsługi klawiatury matrycowej służy do ustawienia kolejno stanu logicznego O na poszczególnych liniach portu P l (od P 1.4 do P 1.7) i odczytania stanu linii od P 1.0 do P 1.3. Naciśnięty przycisk wymusza stan O

Dołączenie ośmiu styków klawiatury lub np. wyłączników krańcowych poprzez

zewnętrzny port wejściowy

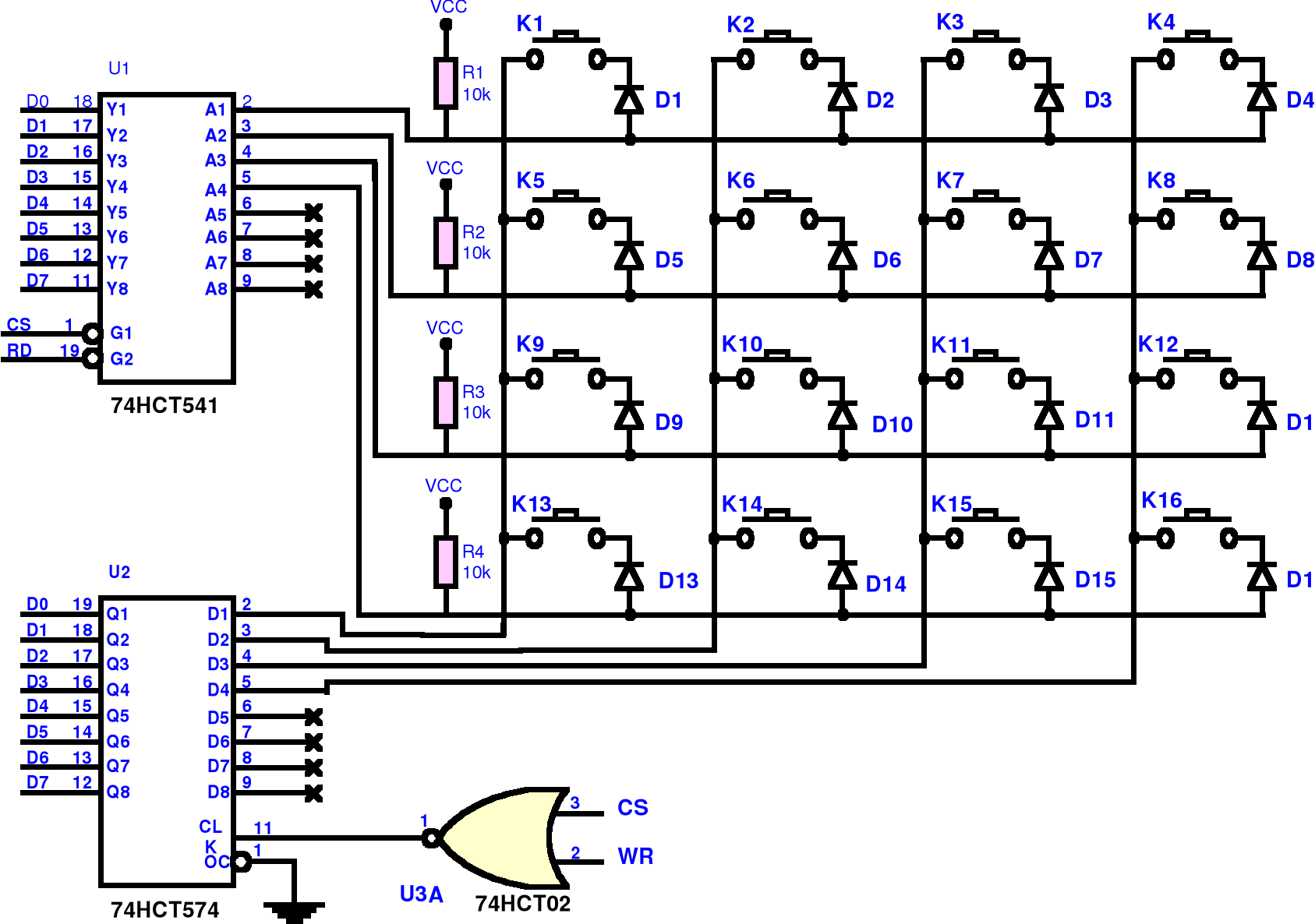

Dołączenie klawiatury matrycowej 4x4 (16 przycisków) do zewnętrznego portu

wejścia / wyjścia

Podłączenie klawiatury poprzez specjalizowany układ 74C922

Zastosowanie kodera priorytetowego jako urządzenia pośredniczącego

18 Wyświetlacz, wskaźnik (z ang. Display),

jest to urządzenie wyjściowe służące do obrazowania niewielkiej ilości danych (cyfry, symbole, litery). Wyświetlacz w dużym stopniu ułatwia komunikację użytkownika z układem.

Ogólny podział wyświetlaczy, ze względu na technologię:

Jarzeniowe

Diodowe (LED)

Ciekłokrystaliczne (LCD)

Właściwości wyświetlaczy

Wyświetlacze LED:

wysoka wydajność świecenia

niski pobór mocy

długa żywotność

duża niezawodność

Wyświetlacze LCD:

niewielki pobór mocy (0,1nW/cm2)

niskie napięcie sterowania

możliwość stosowania różnego rodzaju oświetlenia

możliwość uzyskania różnobarwnych obrazów

możliwość uzyskania różnych kształtów elementu wyświetlanego

Podłączanie wyświetlacza 7-segmentowego do mikroprocesora

Podłączenie dwóch wyświetlaczy do mikroprocesora

Podłączenie czterech wyświetlaczy 7-segmentowych do mikroprocesora poprzez

dekodery typu CD4511

8051

Adresowanie ukladow we-wy :3

Architekturę harwardzką charakteryzuje 11

Architekturę Von-Neumana 10

Blok magistral 5

Blok sterujący 4

Charakterystyka przetwarzania potokowego (PIPELINING) 14

Cykl rozkazowy mikroprocesora 6

KLAWIATURY 17

MIKROPROCESOR JEDNOUKŁADOWY 7

Ortogonalność8

Podstawowe typy układów wejścia - wyjścia 16

Podział ARCHITEKTURY PROCESORA ze względu na mapę pamięci 9

Podział ARCHITEKTURY PROCESORA ze względu na typ listy instrukcji 13

System mikroprocesorowy - samodzielny układ mikroprocesora,

współpracujących z nim pamięci oraz urządzeń wejścia-wyjścia 15

SYSTEM PRZERWAŃ: 2

Uklad scalony 1Wyświetlacz, wskaźnik 18

Zmodyfikowana architektura harwardzka 12

Wyszukiwarka

Podobne podstrony:

Diody, Politechnika Rzeszowska - Elektronika i telekomunikacja 2012-2017, II rok

54+, Politechnika Rzeszowska, Elektrotechnika, semestr 2, Fizyka Lab, Sprawozdania, Fizyka Laborator

1B+, Politechnika Rzeszowska, Elektrotechnika, semestr 2, Fizyka Lab, Sprawozdania, Fizyka Laborator

44 sprawozdanie czyjeś, Politechnika Rzeszowska, Elektrotechnika, semestr 2, Fizyka Lab, Sprawozdani

Laboratorium fizyka ćw 1A, Politechnika Rzeszowska, Elektrotechnika, semestr 2, Fizyka Lab, Sprawozd

elektra P4, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektronik

elektra M4, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektronik

Elektra M-2spr, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektr

elektra M5, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektronik

Pytania 2012!!!, medycyna, II rok, fizjologia, giełdy

elektra M6a, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektroni

Bo wyklady 15 godz. 2012, Zarządzanie, II rok, ćwiczenia(2)

elektra p1, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektronik

elektra p1i, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektroni

Elektra p3 2, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektron

Elektra M-3spr, Studia, SiMR, II ROK, III semestr, Elektrotechnika i Elektronika II, Elektra, Elektr

więcej podobnych podstron