Temat : PRZERZUTNIKI

Bramki elementarne :

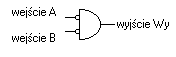

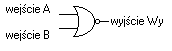

AND ( „i” koniunkcji)

AND NOT AND - NAND AND

(bramka AND z zanegowanym wyjściem) (z zanegowanymi wejściami)

A B Wy Wy Wy

0 0 0 1 1

0 1 0 1 0

1 0 0 1 0

1 1 1 0 0

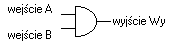

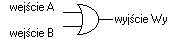

b) OR ( „lub” suma)

OR NOT OR - NOR OR

(bramka OR z zanegowanym wyjściem)(z zanegowanymi wejściami)

A B Wy Wy Wy

0 0 0 1 1

0 1 1 0 1

1 0 1 0 1

1 1 1 0 0

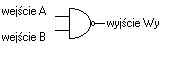

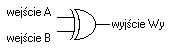

EXOR

A B Wy

0 0 0

0 1 1

1 0 1

1 1 0

Układy kombinacyjne i sekwencyjne :

Układy kombinacyjne są to układy w których stany wyjścia są zdeterminowany przez aktualny stan wejścia (takimi układami są na przykład sieci bramek). Takie układy nie posiadają pamięci i nie zachowują wspomnień przeszłości.

Układy sekwencyjne posiadają możliwości zapamiętywania stanów wcześniejszych. Umożliwia to zastosowanie ich w konstrukcjach układów wykonujących wiele operacji.

Przerzutniki ( flip-flop) :

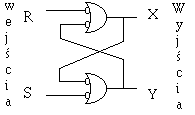

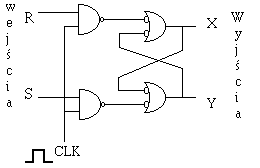

Przerzutnik typu RS - (R - reset -wyzeruj S - set - ustaw) :

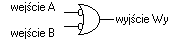

Jest to układ zbudowany z bramek logicznych typu OR z zanegowanymi wejściami według poniższego schematu :

Układ ten posiada dwa stabilne stany (przerzutnik bistabilny), od poprzedniego stanu zależy w którym ze stanów się obecnie znajdzie. Działanie takiego typu przerzutnika opisuje tabela :

R S X Y Stan przerzutnika

L L N i e d o z w o l o n y

L H L H „ 0 ”

H L H L „ 1 ”

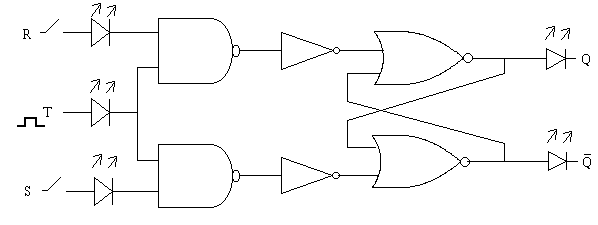

Przerzutnik synchroniczny RS :

W urządzeniach synchronicznych operacje realizujące w nich są wykonywane wyłącznie w chwilach wyznaczonych przez zbocze narastające lub zbocze opadające sygnału prostokątnego przyjmującego wyłącznie wartości odpowiadające 0 i 1, zwane sygnałami synchronizującymi lub taktującymi (clock signal). Poniższy schemat przedstawia najprostszy przerzutnik synchroniczny typu RS, zbudowany jak przerzutnik RS z dodatkowymi parą bramek NAND :

Tablica prawdy takiego przerzutnika jest następująca :

R S X Y stan przerzutnika

L L „ Bez zmiany ”

H L H L „ 1 ”

L H L H „ 0 ”

H H Z a b r o n i o n y

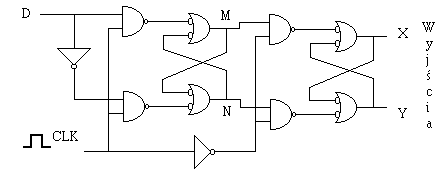

Przerzutnik D :

Przerzutnik typu D jest przerzutnikiem dwuzboczowym (master-slave). Poniższy rysunek przedstawia schemat ideowy takiego układu :

Poniższa tabela przedstawia przejścia w przerzutniku typu D :

D C X Y stan przerzutnika

H lub L L zachowuje wartość poprzednią

L H L H „ 1 ”

H H H L „ 0 ”

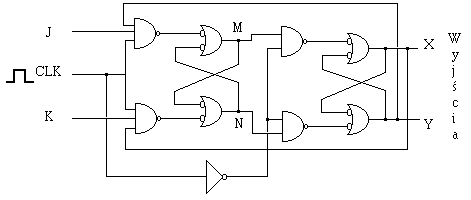

Przerzutnik typu JK :

Jest to przerzutnik podobny w działaniu do przerzutnika typu D z tą różnicą że posiada on dwa wejścia danych. Schemat takiego przerzutnika przedstawiam poniżej :

Tablica prawdy jego wygląda następująco :

J K stan przerzutnika

L L zachowuje wartość poprzednią

L H „ 0 ”

H L „ 1 ”

H H zmienia wartość na przeciwną

Rejestry :

Jest to układ służący do przechowywania informacji. Rejestry dzielą się ze względu na sposób wprowadzania i wyprowadzania informacji następująco na :

szeregowe ( szeregowe wprowadzanie i wyprowadzanie informacji - kolejno bit po bicie )

równolegle (równoległe wprowadzanie i wyprowadzanie informacji - jednocześnie do wszystkich i po wszystkich pozycjach rejestru )

szeregowo - równolegle (szeregowe wprowadzanie i równoległe wyprowadzanie informacji )

równolegle - szeregowo (równoległe wprowadzanie i szeregowe wyprowadzanie informacji )

Wykonanie ćwiczenia :

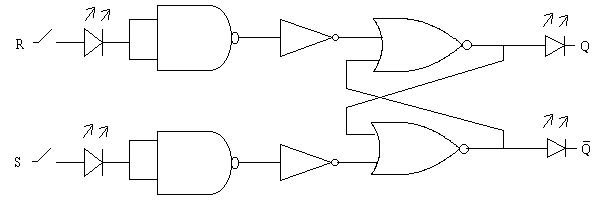

1. Korzystając z modułów 7400 (zestawu bramek typu OR z zanegowanym wyjściem),7402 (zestawu bramek z zanegowanym wyjściem) i 7404 (zestawu negatorów) zestawu UNILOG-2 zbudowałem przerzutnik typu R-S według poniżej przedstawionego schematu :

Tablica prawdy dla takiego układu uzyskana doświadczalnie wygląda następująco :

R |

S |

Stan przerzutnika |

L H L H |

L L H H |

Początkowy L H „1” H L „0” L L zabroniony |

Pokrywa się ona z przewidywaniami teoretycznych rozważeń na podstawie budowy tego układu. W stanie niskim na wejściach R i S pozostaje na wyjściach stan początkowy (zależności od pozostawienia go). W stanie R wysokim (S niskim) doświadczalnie uzyskałem stan przerzutnika „1” ,a dla R niskiego - S wyskoki stan przerzutnika „0”. Są to wyniki odwrotne do przewidywanych wyników, ale jest to spowodowane brakiem zastosowania jednego negatora, co w konsekwencji daje efekty negacji na wyjściach. Przy stanie wejściowym wysokim otrzymujemy na wyjściu stany niskie jest to stan zabroniony.

Przeprowadzone doświadczenie dowodzi poprawności działania przerzutnika typu R - S.

2. Korzystając z modułów 7400 (zestawu bramek typu OR z zanegowanym wyjściem),7402 (zestawu bramek z zanegowanym wyjściem) i 7404 (zestawu negatorów) zestawu UNILOG-2 zbudowałem synchroniczny przerzutnik typu R-S według poniżej przedstawionego schematu :

Tablica prawdy dla takiego układu uzyskana doświadczalnie wygląda następująco :

R |

S |

Stan przerzutnika |

L H L H |

L L H H |

Zachowany poprzedni L H „1” H L „0” T 0 nieokreślony |

|

|

|

|

|

|

Jak w punkcje1ćwiczenia wszelkie przewidywania teoretyczne pokryły się z wynikami doświadczalnymi.

Co dowodzi zgodności działania synchronicznego przerzutnika typu R - S.

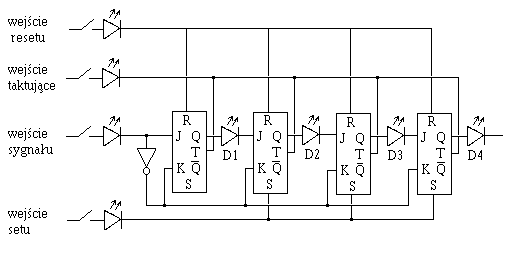

Korzystając z zestawów przerzutników typu J - K zbudowałem według poniższego schematy

4-bitowy rejestr przesuwający. Posiada on dwa wejścia sterujące wejściem Resetu i wejściem Setu. Poza tym jedno wejście sterujące wejściami J i K. Każde z wejść podłączyłem do diody świecącej dzieki czemu mogłem kontrolować stany na nich.

Zastosowanie negatora pomiędzy wejściami J a K daje gwarancje, że podczas wykonywania demonstracji nie wystąpi zabroniony stan wejścia. Zastosowanie czterech dodatkowych diud świecących na wyjściach Q, przy każdym z przerzutników (D1,D2,D3,D4) umożliwia mi kontrolowanie wyniku doświadczenia. Uzyskane wyniki przedstawiam w poniższej tabeli :

Wejście Resetu |

Wejście setu |

Wejście sygnału |

Wejście taktującego |

Wynik na wyjściach D1 D2 D3 D4 |

1 1 1 1 1 1 1 1 1 1 1 1 1 1

1 0 0 |

1 1 1 1 1 1 1 1 1 1 1 1 1 1

0 1 0 |

0 1 0 1 0 0 0 0 0 0 0 0 0 0

dowolny dowolny dowolny |

0 0 1 0 1 0 1 0 1 0 1 0 1 0

dowolny dowolny dowolny |

1 1 1 1 1 1 1 1 0 1 1 1 0 1 1 1 0 0 1 1 0 0 1 1 1 0 0 1 1 0 0 1 1 1 0 0 1 1 0 0 1 1 1 0 1 1 1 0 1 1 1 1 1 1 1 1

1 1 1 1 0 0 0 0 0 0 0 0 |

Jak widać w powyższej tabelce przy stanie wysokim wejścia Reset i Set układ badany wykazywał poprawność działania, jako 4-bitowy rejestr przesuwający ( przesuwanie wiadomości co takt zegara taktującego na wejściu taktującym ). Zmiana stanu na wejściu Set na stan niski przy stanie wysokim Resetu powoduje włączenie na wyjściu stanów wysokich, bez względu na wprowadzane dane na wejście. Zmiana stanu Reset z wysokiego na niski, bez względu na zmiany w pozostałych wejściach resetuje zawartość rejestru - na wyjściach otrzymujemy stany niskie.

Wszystkie uzyskane doświadczalnie wyniki są zgodne z wynikami teoretycznymi co dowodzi poprawności badanego układu.

Wyszukiwarka

Podobne podstrony:

8018

8018

8018

praca-magisterska-wa-c-8018, Dokumenty(2)

8018

8018

8018

8018

więcej podobnych podstron