Laboratorium układów elektronicznych |

||||

Temat ćwiczenia: Wzmacniacze Napięciowe z tranzystorami MOS |

||||

Wydział:

|

Kierunek: Elektronika i Telekomunikacja |

Rok: II |

||

Imię i nazwisko:

|

Data wykonania ćwiczenia:

|

Uwagi:

|

Rok akademicki:

|

|

DANE:

Tranzystor BF245B

R0 = 22[kΩ]

ku0 = -15[V/V]

fd(3 dB) = 50[Hz]

UDD = 15[V]

USS = -15[V]

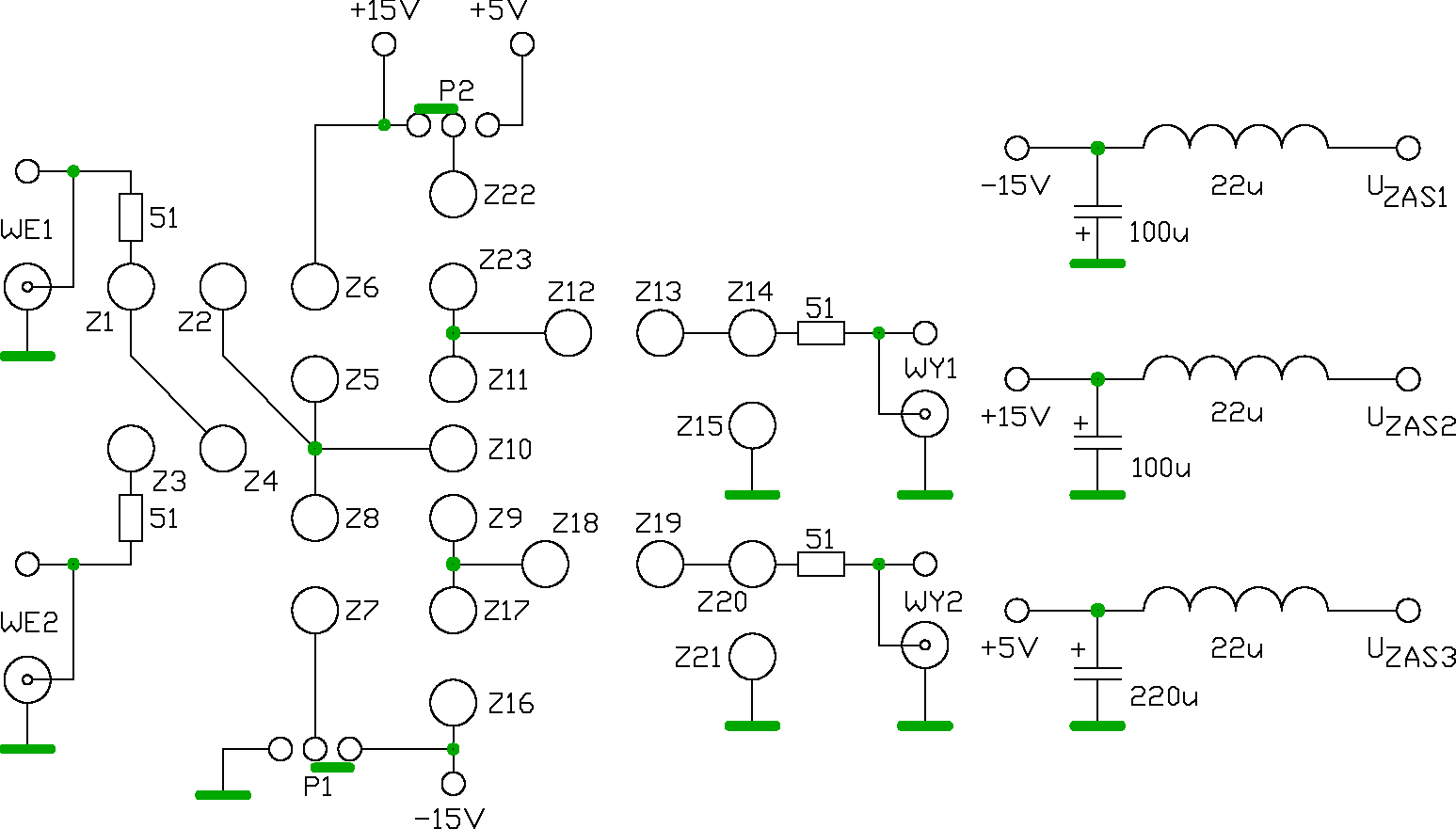

Schemat:

Rys 1. Schemat ideowy rezystorowego wzmacniacza napięciowego z tranzystorem JFET w konfiguracji OS

Rys 2. Małosygnałowy schemat zastępczy wzmacniacza w zakresie średnich częstotliwości

Obliczenia:

Przyjmujemy, że: R = 1 [MΩ].

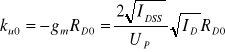

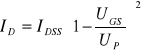

Wychodząc z wzmocnienia napięciowego w zakresie średnich częstotliwości:

, gdzie RD0 = RD||R0

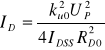

oraz przyjmując założenie, że dla składowej stałej potencjał drenu wynosi 0, otrzymujemy wyrażenie na prąd drenu:

![]()

Przyjmujemy:

![]()

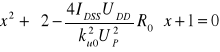

Po przekształceniach otrzymujemy równanie kwadratowe:

Do obliczeń potrzebne będą wartości napięcia progowego tranzystora UP (od -3,9[V] do -4,1[V], przyjmujemy wartość uśrednioną UP = -4[V]) i prądu nasycenia IDSS (od 12[mA] do 13[mA], przyjmujemy wartość uśrednioną IDSS = 12,5[mA]).

Po rozwiązaniu powyższego równania otrzymujemy dwie wartości x:

x1 = 0,47 lub x2 = 2,11

i odpowiednio dla tych wartości:

RD1 = 10[kΩ], RD2 = 46,5[kΩ]

z powyższych wyników wybieramy RD1 gdyż przy RD2 tranzystor zaczyna się odcinać

RD0 = 7[kΩ]

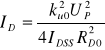

Liczymy prąd drenu:

ID = 1,47[mA]

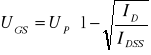

Napięcie bramka-źródło (UGS) oblicza się na podstawie równania charakterystyki tranzystora w zakresie nasycenia:

UGS = -2,63[V]

Wartość RS wyznaczamy z zależności:

![]()

RS = 1,8[kΩ]

Następnie obliczamy napięcie dren-źródło w celu sprawdzenia położenia punktu pracy w obszarze nasycenia:

![]()

UDS = 12,35[V]

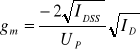

Transkonduktancja układu wynosi:

gm = 2,14[mS]

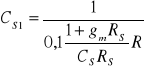

Pojemność blokującą źródło CS wyliczymy przekształcając wzór:

![]()

, gdzie ![]()

stąd:

![]()

CS = 8[μF]

Biegun ![]()

można uznać za dominujący, gdy:

![]()

![]()

![]()

Z powyższych wzorów wyliczamy CS1:

CS1 = 30[nF]

Dla powyższych wartości elementów przeprowadziliśmy symulację w programie PSpice, oraz dobraliśmy elementy z szeregu E24 dla rezystorów oraz z szeregu E6 dla kondensatorów i uzyskaliśmy charakterystykę amplitudowo-częstotliwościową zgodną z założonymi danymi projektowymi:

RD = 10[kΩ] CS = 10[μF]

RS = 1,8[kΩ] CS1 = 33[nF]

RG = 1[MΩ]

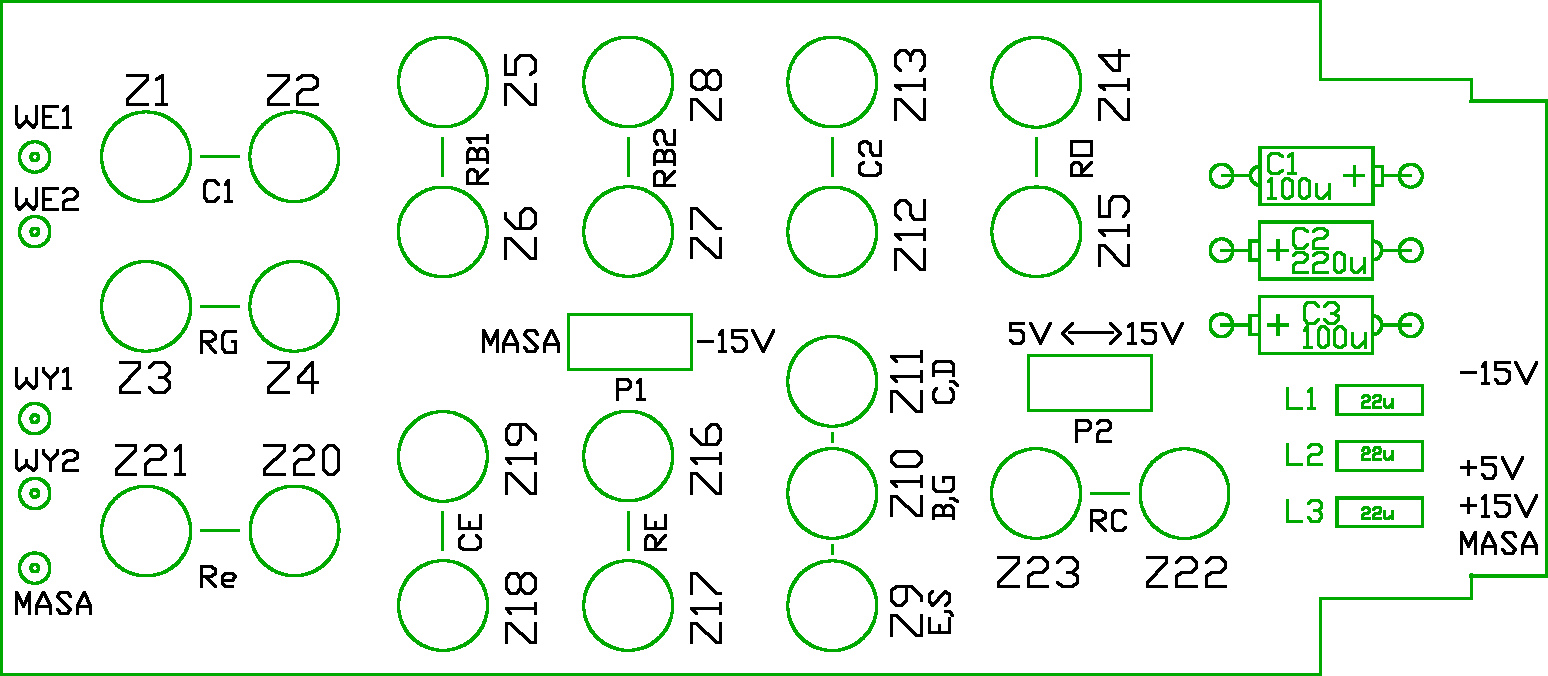

Schemat połączeń układu

Schemat ideowy badanego wzmacniacza na wkładce DWT 1.

Wygląd płytki drukowanej wkładki DWT 1.

Schemat blokowy połączeń aparatury.

Sprzęt niezbędny do wykonania ćwiczenia:

DWT 1 - wkładka dydaktyczna wzmacniacza tranzystorowego,

SGS 1 - wkładka generatora sinusoidalnego przestrajanego,

SD 1 - wkładka przetwornika ac/dc wartości szczytowej,

SN 4222- wkładka przełącznika ac,

SR 1 - wkładka rozgałęziacza sygnału ac,

oscyloskop dwukanałowy,

woltomierz cyfrowy,

częstościomierz cyfrowy,

miernik zniekształceń nieliniowych,

podwójna rama z zasilaczami,

tranzystory wymienne,

rezystory wymienne,

kondensatory wymienne, zwory.

Sprawozdanie

Ad. 5.2 Weryfikacja projektu:

Zmierzony punkt pracy:

bez obciążenia:

UGS = -2,38[V]

UDS = 12,35[V]

UD = 0,01[V]

ID = 1,498[mA]

z obciążeniem:

UGS = -2,38[V]

UDS = 12,345[V]

UD = 0,00[V]

ID = 1,500[mA]

Otrzymane wzmocnienie: kusmax = -16[V/V]

Częstotliwości graniczne: fd = 43[Hz]

fg = 149[kHz]

Ad. 5.2.4 Problemy:

Wyznaczona doświadczalnie wartość wzmocnienia pokrywa się z założoną. Minimalna różnica jest spowodowana tolerancją wartości elementów.

Kształt sygnału wyjściowego jest niezniekształcony aż do wartości międzyszczytowej około 16[V] (patrz charakterystyka przejściowa). Natomiast przy wyższych wartościach tego sygnału następuje zniekształcenie (spłaszczenie) wierzchołków sinusoidy, co jest spowodowane wchodzeniem tranzystora w obszar liniowy lub w odcięcie. Obrazuje to zagięcie charakterystyki przy wyższych napięciach wejściowych

Ad 5.3.2 Częstotliwości graniczne:

W celu wyznaczenia częstotliwości granicznych wzmacniacza, korzystając ze znalezionego wcześniej maksymalnego wzmocnienia w zakresie średnich częstotliwości obliczamy graniczną wartość wzmocnienia (kus max - 3dB). Następnie, znając amplitudę przebiegu wejściowego obliczamy graniczną amplitudę sygnały wyjściowego. Dalej szukamy częstotliwości, przy których przebieg wyjściowy przyjmuje takie amplitudy. Znalezione w ten sposób częstotliwości to górna i dolna częstotliwość graniczna wzmacniacza, wynoszą one: fd = 43[Hz], fg = 149[kHz]. Dolna częstotliwość graniczna wzmacniacza jest zgodna z przewidywaniami, natomiast górna jest wyraźnie niższa od tej uzyskanej na drodze symulacji. Może być to spowodowane większymi niż w symulacji rzeczywistymi pojemnościami wewnętrznymi tranzystora.

1

Wyszukiwarka

Podobne podstrony:

wzmacniacz operacyjny - konspekt+sprawozdanie, Elektronika i telekomunikacja, AUE - Analogowe Układy

wzmacniacz OE - konspekt+sprawozdanie, Elektronika i telekomunikacja, AUE - Analogowe Układy Elektro

Konspekt + sprawozdanie, Elektronika i telekomunikacja, AUE - Analogowe Układy Elektroniczne

generatory - konspekt, Elektronika i telekomunikacja, AUE - Analogowe Układy Elektroniczne

konspekt różnicowy, Elektronika i telekomunikacja, AUE - Analogowe Układy Elektroniczne

generatory - sprawozdanie, Elektronika i telekomunikacja, AUE - Analogowe Układy Elektroniczne

Sprawko Elektronika Wzmacniacz

SprawkoZalewska, Elektronika i telekomunikacja-studia, rok III, sem V, tbez

sprawko wzmacniacz we, Materiały PWR elektryczny, semestr 3, PODSTAWY ELEKTRONIKI, elektronika we

Sprawozdanie - BADANIE WZMACNIACZA OPERACYJNEGO, EiT, Analogowe układy elektroniczne, Sprawozdanie -

sprawozdanie 7 wzmacniacz tranzystorowy, Studia, Podstawy elektroniki, sprawka

Sprawko Elektronika Wzmacniacz

[8]konspekt new, Elektrotechnika AGH, Semestr II letni 2012-2013, Fizyka II - Laboratorium, laborki,

sprawko elektroforeza

matrialy, PWR [w9], W9, 5 semestr, Podstawy elektrotechniki Lab, MATERIAŁY, podst ele lab - swistak,

Sprawozdanie M6 B-7, AGH, MiBM - I rok, Elektrotechnika, Sprawka - elektro, M6

konspekt nr8, Elektrotechnika AGH, Semestr II letni 2012-2013, Fizyka II - Laboratorium, laborki, Fi

M5 Charakterystyki podstawowych elementów elektronicznych, AGH, MiBM - I rok, Elektrotechnika, Spraw

więcej podobnych podstron