1030

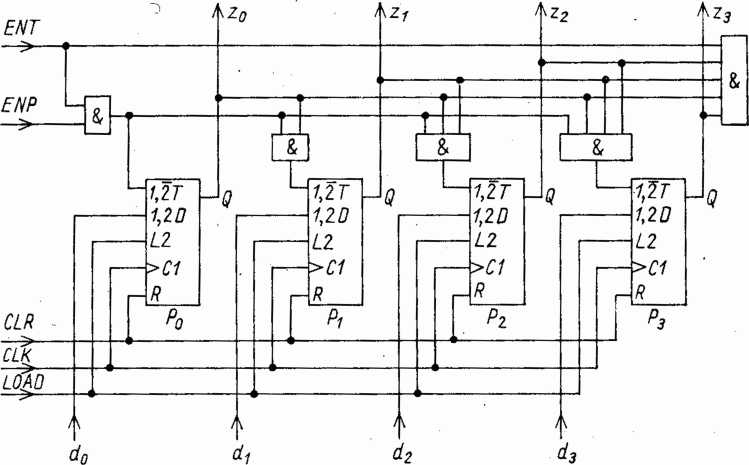

Rys. 10.30. Praktyczna realizacja scalonego licznika synchronicznego

ENT (ang. enable T) - zezwolenie T ENP (ang. enable P) — zezwolenie P CLR (ang. elear) — zerowanie CLK (ang. clock) — zegar

RCO (ang. ripple carry output) - wyjście przeniesienia szeregowego

Wyszukiwarka

Podobne podstrony:

Rys. 10.43. Najprostsza realizacja 4-bitowego rejestru przesuwającego DI (ang. data input) — wejście

Rys. 10.43. Najprostsza realizacja 4-bitowego rejestru przesuwającego Dl (ang. data input) — wejście

100B92 Przecinając stożek płaszczyzną nie przechodzącą przez jego wierzchołek, można uzyskać (rys. 1

Rys. 10.30. Zastosowanie łączników imadłowych do mocowania dźwigara na słupie Rys. 10J1. Konduktor d

Rys. 10.39. Synchroniczny licznik BCD Tablica 10.6. Wybrane scalone dekady synchroniczne Rodzaj

Rys. 10.29. Synchroniczny licznik dwójkowy

Image196 Rys. 4.168. Schematy logiczne liczników synchronicznych z przeniesieniami a) równoległymi,

Image219 Rys. 4.214 Zasada budowy licznika synchronicznego o dużej pojmności

Image235 akt w 2t C Dekada IV Rys. 4.242. Ośmiodekadowy licznik synchroniczny Rys. 4.243.

więcej podobnych podstron