168 169

166

W serii 74 produkowanych jest kilka układów Schmitta,bądź jako samodzielne przerzutnlkl, bądź jako bramki 5AND z wbudowanymi przsrzutnlkaml. Są to układy:

6 x przerzutnik Schmitta 7414 2 x NAND 4-wejściowy Schmitta 7413 '

4 x NAND 2-wejściowy Schmitta 74132

Przerzutnik Schmitta wykorzystywany jest do formowania impulsów (zmniejszania czasów narastania i opadania), czego jaskrawym przykładem może być zamiana przebiegu sinusoidalnego na prostokątny.

5.8. REJESTRY

Jeden.przerzutnik (najlepiej typu D) przechowuje jeden bit informacji! dla przechowywania informacji (liczby) wielobitowej potrzebny jest więc zespół przerzutników, zwany rejestrem.

5.8.1. Budowa rejestrów

Ze względu na sposób wprowadzania i wyprowadzania informacji rejestry dzielimy na:

- równoległe lub szeregowe, przy czym w rejestrze równoległym (Parallel Input Parallel Output = PIPO) zarówno wprowadzanie jak i wyprowadzanie informacji odbywa się równolegle, zaś w szeregowym SIPO, PISO, SISO przynajmniej jedna z tych operacji odbywa się szeregowo (Serial = S);

- synchroniczne lub asynchroniczne. zależnie od tego, czy wprowadzanie informacji do przerzutników odbywa się za pośrednictwem wejść informacyjnych czy też ustawiających.

UMI

cni*

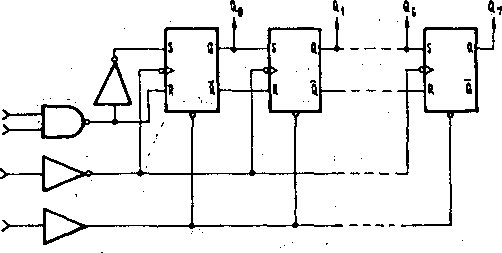

Rys. 5*52. Rejestr 74164 .

W najprostszym przypadku rejestr równoległy jest zespołem przerzutni- . ków D nie powiązanych ze sobą, ale wspólnie taktowanych (np. 7475, 74100, 74116, 74374), a czasami również wspólnie zerowanych (np. 74174, 74175)•

W takich rejestrach, tzw. buforowych, informacja wprowadzana jest synchronicznie, przy czym - zależnie od przeznaczenia rejestru - przerzutnik! mogą być taktowane poziomem (zatrzask} lub zboczem, albo Master-Slave.

Dla umożliwienia szeregowego wprowadzania lub wyprowadzania informacji wymaga się od rejestru zdolności jej przesuwania. Rozróżnia się przy tym rejestry przesuwające (Shift Register) jednokierunkowe lub dwukierunkowe.

Typowym przykładem rejestru przesuwającego w jednym .kierunku je3t 8-bi-towy rejestr SIPO pokazany na rys. 5.52. Składa się On z ośmiu przerzutników R3-MS połączonych W kaskadę, przy czym pierwszy pracuje jako D. Informacja wprowadzana jest poprzez jedno z wejść szeregowych SI (drugiedaje możliwość bramkowania) i wpisywana do pierwszego przerzutnika w czasie narastania zbocza impulsu zegarowego, a w czasie kolejnych narastających (dodatnich) zboczy impulsów zegarowych przesuwana do kolejnych przerzutników. Rejestr przesuwający jest synchronicznym układem sekwencyjnym, więc - jak pamiętamy - dla kontrolowanego przepływu informacji konieczne jest użycie przerzutników master-slawe lub taktowanych zboczem. W przypadku przerzutników taktowanych poziomem, informacja wejściowa propagowała

't

by się wzdłuż rejestru tak długo, jak długo trwał by impuls zegarowy. Rejestr można asynchronicznie zerować, czyli równolegle wpisywać zera.

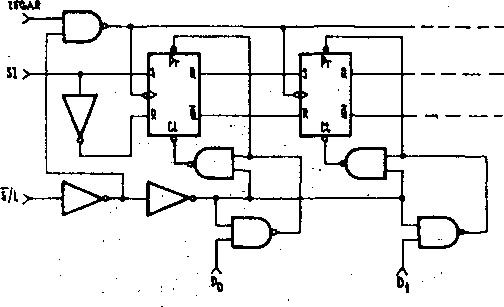

Przy przedstawionym sposobie łączenia przerzutników, wpisywanie równoległe dowolnych informacji wymaga zastosowania układów wpisujących i ste-rujących jak na rys. 5-53 (według tej zasady działa rejestr 74165).

Rys. 5-53. Początek rejestru jednokierunkowego z asynchronicznym wpisywaniem równoległym

Podanie 1-ki na wejście sterujące 5/L (Shift/Load - Przesuwanie/Ładowa-nie) powoduje zablokowanie wejścia zegarowego i wpisanie danych DQ, D^, .. poprzez wejścia ustawiające przerzutników. Przy S/L=0 wpisana informacja przesuwa się w czasie dodatnich zboczy zegara, przy czym, oczywiście.możliwe jest szeregowe wpisywanie nowej informacji poprzez "wejście SI.

Dla zrealizowania synchronicznego, wpisywania-równoległego należy(patrz rys. 5*54): ■' ■. , ' '} . | ’ i ' . "

- wszystkie przerzutnik! .rejestru przekształcić-w'D, '

I

Wyszukiwarka

Podobne podstrony:

168 169 168 V aerll. 74 produkowanych jest kilka układów Schmitta,bądź jako samodzielne przerzutnikl

Photo00255 500 g cały 1 kg 166. Melon 330 g 17 o g 767. Mandarynki 50 g 100 g 168, Nektarynki 150 g

168 Rozdział 6 tempa wzrostu ilości produkcji końcowa ocena jest pozytywna, gdyż wskazuje na podjęci

71395 Strona00181 - 101 - 166* Brzęczyk elektroniczny Obwód jest polęczony jako multiwibrator ,astab

DSC00780 Obecnie znanych jest kilka typów genów białek regulatorowych, których produkty białkowe bar

DSCN9507 (2) 18 I Ą& m i 166. g 168. 169. 170. 171. 172. „173. •174. 175. 176. •177. I

1. Wstęp Cykl produkcyjny jest to czas trwania procesu produkcyjnego wyrobu zawart

System sterowania głównego robota wyposażony jest w kilka współpracujących ze sobą programów, w skła

skanuj0277 286 Zrównanie lo wyznacza wielkość popytu przedsiębiorstwa na dany czynnik produkcji i je

więcej podobnych podstron