Image337

nika i jednoczesne odblokowanie bramki wejściowej licznika zliczającego do A + l. Impulsy zegarowe są teraz zliczane przez pozostałe dwa liczniki. Porównanie liczb jest zakończone z chwilą osiągnięcia stanu N+l przez obydwa liczniki LA i LB lub napełnienia licznika LA+1. Jeśli licznik LAf t nie napełni się podczas porównania, to rozpatrywane liczby nie różnią się o więcej niż o A. W celu otrzymania dodatkowej informacji o relacji między wielkościami liczb A i B należy uzupełnić rozważany komparator układem wykrywającym, w którym torze (w a czy w b) pojawi się wcześniej sygnał świadczący o stanie zerowym licznika. Przed dokonaniem następnej komparacji układ należy wyzerować. Przedstawiony układ sekwencyjny szczególnie dobrze nadaje się do zastosowania w tym przypadku, gdy liczby A i B mają postać ciągu impulsów.

4.5.3.4. Komparatory szeregowe

Jeśli w urządzeniu (systemie) jest stosowane szeregowe przetwarzanie informacji, wówczas do porównywania liczb i ustalenia relacji między nimi stosuje się komparator szeregowy.

Podobnie jak w przypadku komparatorów równoległych, przy rozpatrywaniu komparatorów szeregowych ograniczono się do przedstawienia układów służących do porównywania liczb dodatnich.

Jeśli dwie liczby dodatnie porównujemy począwszy od najbardziej znaczącego bitu, to liczbą większą jest liczba mająca większy pierwszy bit. W przypadku, gdy porównania dokonujemy począwszy od najmniej znaczącego bitu, to liczbą większą jest liczba mająca większy ostatni bit. Liczby dodatnie są równe, jeśli bity tych liczb na odpowiadających sobie pozycjach są jednakowe.

Rozwiązań układowych komparatorów szeregowych jest bardzo wiele. Ta mnogość rozwiązań wynika z faktu, że do zimplementowania takiego układu mogą być użyte różnego typu elementy logiczne. Kilka możliwych rozwiązań komparatorów zostanie przedstawione dalej.

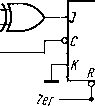

Schemat logiczny komparatora szeregowego służącego do określenia, czy zachodzi relacja A = B, czy A^zB jest przedstawiony na rys. 4.387. Przed po

Takt

■3 0

A*B

Rys. 4.387. Schemat logiczny

ą=£ komparatora szeregowego służącego do określania, czy między liczbami A i B zachodzi relacja A = B, czy A ^ Bi

równaniem układ powinien być wyzerowany. Stan wyjścia Q przerzutnika równy 1 po wyzerowaniu, zmieni się na 0, jeśli kolejne bity liczb A i B będą różne. Stan ten utrzymuje się aż do ponownego wyzerowania układu.

Przykłady implementacji komparatorów szeregowych służących do wyznaczania relacji A<C.B9A~B9A>B między liczbami A i B są przedstawione na rys. 4.388 i 4.389. W układach przedstawionych na rys. 4.388 porównanie jest dokonywane począwszy od najbardziej znaczącego bitu. Wynik pojawia się

Wyszukiwarka

Podobne podstrony:

Zestaw 1 8. W mikroprocesorze licznik rozkazów to A. licznik zliczający kolejne im

33 (81) - 62 - przed jednoczesnym pojawieniem się impulsów zliczanych na obu wejściach licznika rewe

Image143 rys. 4.91. Impuls „start” powoduje wpisanie informacji do rejestru i odblokowanie bramki B.

Image197 W przypadku licznika zliczającego w przód w naturalnym kodzie dwójkowym przerzutnik A repre

Image237 Liczniki zliczające wstecz Rozpatrzmy synchroniczną dekadę liczącą wstecz w naturalnym kodz

Image261 — wpisywanie liczby N do licznika i odliczanie (odejmowanie) impulsów wej

176 177 o 176 Przy łączeniu szeregowym każdy następny licznik zlicza impulsy prze-

176 177 o 176 Przy łączeniu szeregowym każdy następny licznik zlicza impulsy przeniesienia licznika

IMAG0470 _p£ Otwarcie bramki startn Zamknięcie bramki stop t=Tx N - zliczanych impulsów

31 (54) WEJŚCIA LICZNIKA 74193 Count up ICountdu-riCIear [i Wejścia równolegle Rys.4.3. Płyta czołow

Image253 lmulsy zliczane wprzód Impulsy zliczane wstecz Rys. 4.275. Ilustracja zmniejszenia czasu

więcej podobnych podstron