Image407

10'

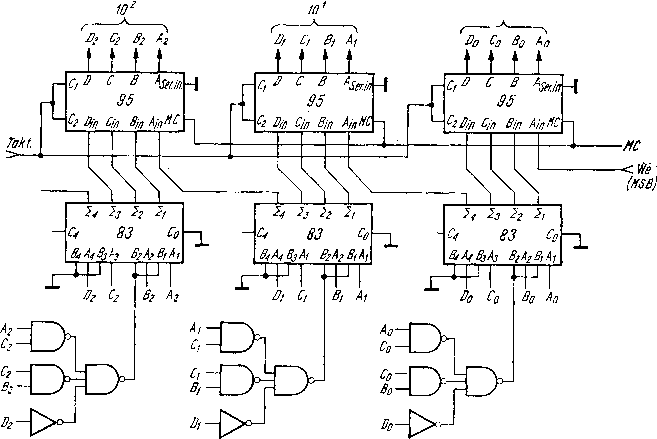

Rys. 4.476. Schemat logiczny przetwornika szeregowego BIN/BCD

DC

.BA

|

0 |

1 |

3 |

2 |

|

4 |

5 |

7 |

6 |

|

8 |

9 |

Rys. 4.477. Tablica Kamaugha dla układu korekcji przetwornika przedstawionego na rys. 4.476

4.6.6.3. Przetworniki równoległe

Przetworniki równoległe charakteryzują się jednoczesnym przetwarzaniem wszystkich bitów słowa kodu wejściowego.

Do konwersji równoległej są wykorzystywane trzy metody, a mianowicie:

— metoda sumacyjna,

— metoda tablicowa,

— metoda tablicowo-sumacyjna.

W celu przetworzenia całkowitej liczby BCD na liczbę BIN metodą suma-cyjną, należy zsumować odpowiednie rozkłady dwójkowe cyfr liczby BCD. Rozpatrzmy 2-cyfrową liczbę dziesiętną: D J. Można ją przedstawić w następującej postaci:

10D+J lub SD+2D + J

Jeżeli powyższe działania wykona się w arytmetyce dwójkowej, to otrzymamy odpowiednik dwójkowy tej liczby. Mnożenie przez 8 i przez 2 odpowiada prze-

Wyszukiwarka

Podobne podstrony:

Image352 Rys. 4.403. Schemat logiczny dwupoziomowego, szeregowego enkodera priorytetowego&

Image498 I 09 Rys. 4.627. Schemat logiczny programowanego generatora fali prostokątnej 9 o 09 99 9 9

skanuj0011 (180) co Ol Wejścia Rys. 4.372. Schemat logiczny dwupoziomowego, szeregowego enkodera pri

Image498 I 09 Rys. 4.627. Schemat logiczny programowanego generatora fali prostokątnej 9 o 09 99 9 9

Image295 Rys. 4.337. Schemat logiczny dwójkowego sumatora szeregowego służącego do realizacji operac

Image470 Rys. 4.585. Schemat logiczny rozdzielacza 16-wyjściowego Wyjścia (kod 1 z 64) Wejście >-

Image487 Rys. 4.610. Schemat logiczny generatora impulsów o czasie trwania impulsu wyjściowego progr

Image494 Rys. 4.620. Schemat logiczny generatora fali prostokątnej z niezależnym nastawianiem czasu

skanuj0025 (84) Wejścia £9,827 23222l 2° Rys. 4.392. Schemat logiczny dekodera matrycowego 10/1024

więcej podobnych podstron