Image505

o

I)przełącznik Pf w dolnym położeniu

•'“U LT

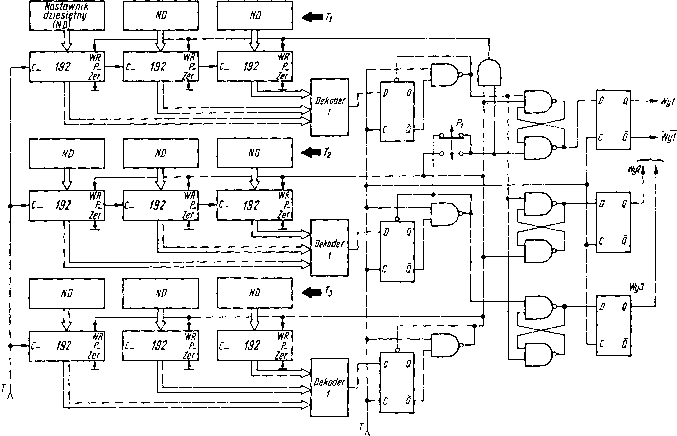

Rys. 4.639. Schemat logiczny uniwersalnego, programowanego generatora impulsów oraz par impulsów

^ II)przełącznik Pf w górnym położeniu

jt_ —n-

lr wnjiJLj:=:Lnj lt

Ul) przełącznik Pf w górnym położeniu

Wyż

Wy3

_r Ti

y

....

+-Tf

n

Rys. 4.640. Trzy rodzaje przebiegów uzyskiwanych z generatora, którego schemat przedstawiono na rys. 4.639

Dla generatora fali impulsów prostokątnych:

Tt = kT Tz — mT

gdzie: k = 1 -f- 998, m = 2 999.

Przykładowo:

Dla jednostki wzorcowej T = 100 ns T1 = 100 — 99800 ns,

T3=-200 ~~ 99900 ns.

Dla jednostki wzorcowej T = 1 ms T1 = 1 -f- 998 ms,

r3 = 2 -r- 999 ms.

Wyszukiwarka

Podobne podstrony:

Image503 Rys. 4.635. Schemat logiczny programowanego generatora par impulsówa --(25-55)Tb i Rys. 4.6

Image504 Nastawy Rys. 4.638 Schemat logiczny generatora przebiegów napięć o częstotliwościach wzorco

Image506 Rys. 4.641. Schemat logiczny programowanego generatora impulsów o dowolnych wzorach zero-je

Image537 Zrejestru Rys. 4.695. Schemat logiczny dynamicznego układu wyświetlania informacji numeryc

Image538 Rys. 4.697 Schemat logiczny fragmentu układu sterującego dynamicznym układem wyświetlani Uk

Image540

Image562 fd Wejścia / / Od rt Or Rys. 4.739. Schemat logiczny układu statycznego sterującego wskaźni

5WW10 Rys. 14. Płytka drukowana przełącznika cewek drivera (strona druku i elementów) Rys. 15. Schem

silowniki�4 -9~ Rys. 5.13. Sposób stercv/anis siłownikiem stałoprądkościowym SU.0WMIK Rys. 3.14. Sch

piaps 74 7. Układy peryferyjne ar— LT^S? Rys. 7.11. Schemat blokowy Umera Ute 2 i 8-bitowym rejestrz

Image537 Zrejestru Rys. 4.695. Schemat logiczny dynamicznego układu wyświetlania informacji numeryc

więcej podobnych podstron