piaps

74 7. Układy peryferyjne

ar— LT^S?

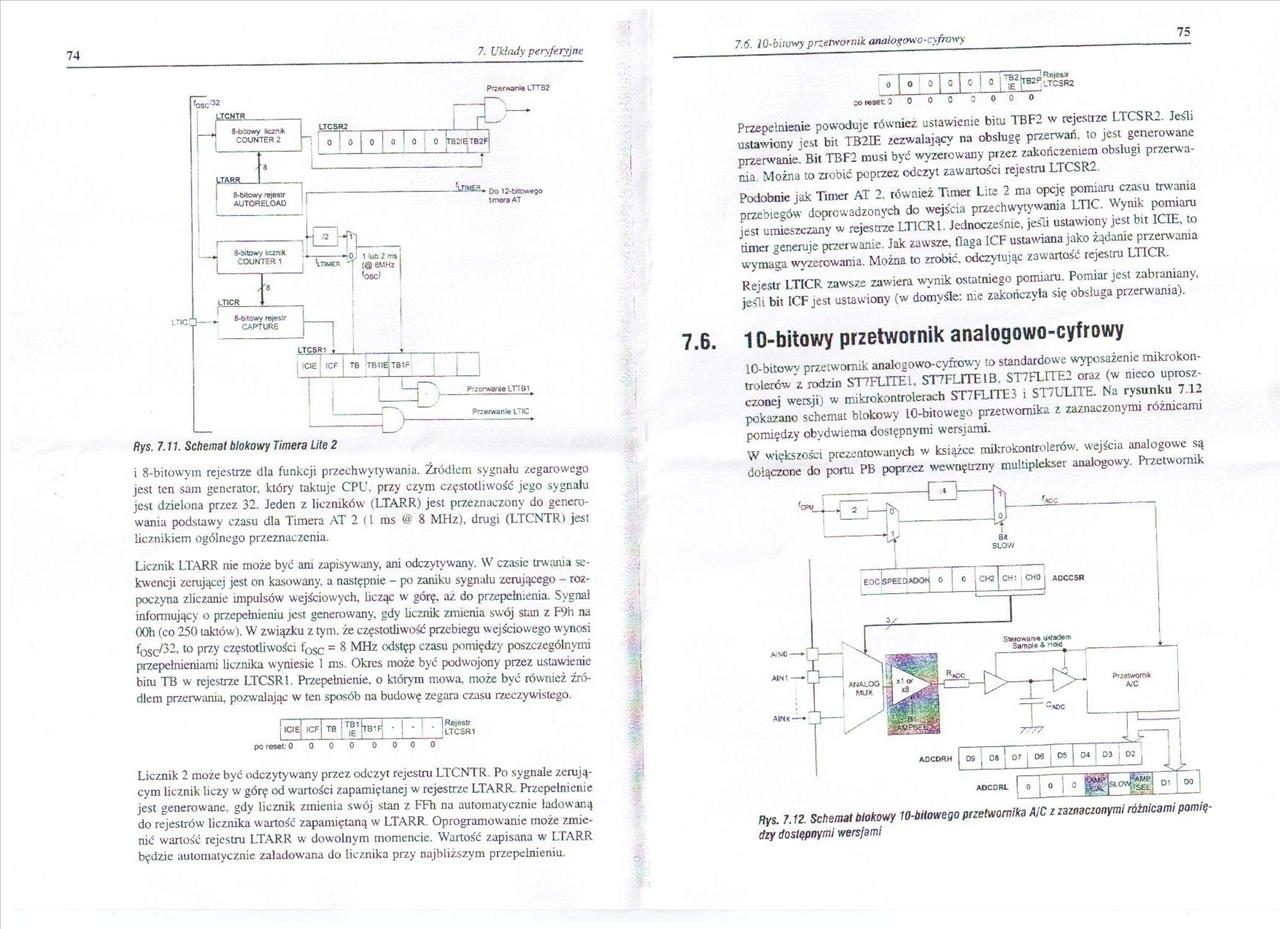

Rys. 7.11. Schemat blokowy Umera Ute 2

i 8-bitowym rejestrze dla funkcji przechwytywania. Źródłom sygnału zegarowego jest ten sam generator, który taktuje CPU. przy czym częstotliwość jego sygnału jest dzielona przez 32. Jeden z liczników (LTARR) jest przeznaczony do generowania podstawy czasu dla Timera AT 2(1 ras (fl 8 MHz). drugi (LTCNTR) jest licznikiem ogólnego przeznaczenia.

Licznik LTARR nie może być ani zapisywany, ani odczytywany. W czasie trwania sekwencji zerującej jest on kasowany, a następnie - po zaniku sygnału zerującego - rozpoczyna zliczanie impulsów wejściowych, licząc w górę. a/ do przepełnienia. Sygnał informujący o przepełnieniu jest generowany, gdy licznik zmienia swój stan z F9h na OOh (co 250 taktów). W związku z tym. że częstotliwość przebiegu wejściowego wynosi fosc/32. to przy częstotliwości fosc = 8 MHz odstęp czasu pomiędzy poszczególnymi przepełnieniami licznika wyniesie 1 ms. Okres może być podwojony przez ustawienie bitu TB w rejestrze LTCSRL Przepełnienie, o którym mowa. może być również źródłem przerwania, pozwalając w ten sposób na budowę zegara czasu rzeczywistego.

łOE ICF

•LTCSR1

po roi«( 0

0 o

0

Licznik 2 może być odczytywany przez odczyt rejestru LTCNTR Po sygnale zerującym licznik liczy w górę od wartości zapamiętanej w rejestrze LTARR. Przepełnienie jest generowane, gdy licznik zmienia swój stan z FFh na automatycznie ładowaną do rejestrów licznika wartość zapamiętaną w LTARR Oprogramowanie może zmienić wartość rejestru LTARR w dowolnym momencie. Wartość zapisana w LTARR będzie automatycznie załadowana do licznika przy najbliższym przepełnieniu.

»WMtO O 0 c 3 0 0 0

Przepełnienie powoduje również ustawienie bitu TBF2 w rejestrze I.TCSR2. Jeśli ustawiony jest bit TB2IF zezwalający na obsługę przerwań, to jest generowane przerwanie. Bil TBF2 musi być wyzerowany przez zakończeniem obsługi przerwania. Można to zrobić poprzez odczyt zawartos'ci rejestru LTCSR2

Podobnie jak Timer AT 2. rów nież Timer Lite 2 ma opcję pomiaru czasu trwania przebiegów doprowadzonych do wejścia przechwytywania LTIC. Wynik pomiaru jest umieszczany w rejestrze LT1CRI. Jednocześnie, jeśli ustawiony jest bit ICIE. to timer generuje przerwanie. Jak zawsze, flaga ICF ustawiana jako żądanie przerwania wymaga wyzerowania. Można to zrobić, odczytując zawartość rejestru LTICR.

Rejestr l.TICR zawsze zawiera wynik ostatniego pomiaru. Pomiar jest zabraniany. jeśli bit ICFjest ustawiony (w domyśle: nie zakończyła się obsługa przerwania).

7.6. 10-bitowy przetwornik analogowo-cyfrowy

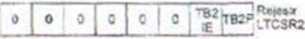

10-bitowy przetwornik analogowo-cyfrowy to standardowe wyposażenie mikrokontrolerów z rodzin ST7FLITEI. ST7FLITE1B. ST7FLITF2 oraz (w nieco uproszczonej wersji) w mikrokontrolerach ST7FLITE3 i ST7ULITE. Na rysunku 7.12 pokazano schemat blokowy 10-bitowego przetwornika z zaznaczonymi różnicami pomiędzy obydwiema dostępnymi wersjami.

W większości prezentowanych w książce mikrokontrolerów, wejścia analogowe są dołączone do portu PB poprzez wewnętrzny multiplekser analogowy. Przetwornik

V

Af

-ca—

AISO

■ta

JŁL

|

W |

B« SWW | |

|

EOCSP££D*OOt 0 |

C CH2 1 |

O’ CMO A CCC SR |

|

3/ |

J | |

|

S*«ns(• * -«« | ||

..-5-4

a«i-

Rys. 7.12. Schemat blokowy 10-bitowego przetwornika AJC z zaznaczonymi różnicami pomiędzy dostępnymi wersjami

Wyszukiwarka

Podobne podstrony:

Rys. 11. Schemat blokowy nadajnika radiofonicznego Oprócz wymienionych wyżej urządzeń służących do

Rys. 11. Schemat układu stycznikowego gwiazda - trójkąt Strona 16 z 20 Instrukcja Laboratoryjna: „ U

uklady logiczne 11 Rys. 11 Schemat obwodu bramki TTL (NAND) z otwartym kolektorem na wyjściu

443 3 11.4. UKŁADY CIEPLNE ELEKTROWNI JĄDROWYCH Z REAKTORAMI RÓŻNYCH TYPÓW Rys. 11.8. Schematy ideow

449 2 11.5. UKŁADY ELEKTRYCZNE ELEKTROWNI JĄDROWYCH 11.5. UKŁADY ELEKTRYCZNE ELEKTROWNI JĄDROWYCH Ry

DSC02364 (3) 74 74 Rys. 4.11 Schemat otektryciny stMmora napięcia z cyfrowo zadawanym napięciem Mody

269 (19) 268 Rozdział 5. Układy regulacji impulsowej Rys. 5.27. Schemat blokowy układu regulacji imp

254 2 5. UKŁADY CIEPLNE ELEKTROWNI I ELEKTROCIEPŁOWNI PAROWYCHb) Rys. 5.11. Schemat: a) rozprężacza;

Image505 o I)przełącznik Pf w dolnym położeniu • “U LT Rys. 4.639. Schemat logiczny uniwersalnego,

rys 2 11(1) Rysunek 2.11. Schemat blokowy karty EGA pracującej w trybie graficznym Do cyfrowego wejś

Rys. 11. Schemat przetwornika momentu obrotowego ze sprzęgłem rozłączającym dla samochodu osobowego.

Rys.2.11. Schemat kinematyczny trzywałkowej skrzyni biegów: 1 - wałek główny, 2 -

21006 spektroskopia016 32 E © k Rys. 11. Schemat fragmentu struktury pasmowej krzemu jako przykład p

więcej podobnych podstron