Image518

Układy translatorów sygnałów MOS/TTL i TTL/MOS

Układy translatorów sygnałów TTL/MOS

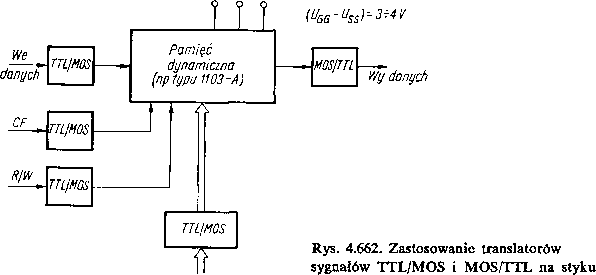

W pamięciach MOS-LSI — np. rozpowszechnionych pamięciach dynamicznych 1103, 1103-A (1024X1 bitów) — wymagane są translatory poziomów napięć TTL/MOS od strony wejścia i MOS/TTL — od strony wyjścia (rys. 4.662).

dss U6G UDD

We adresowe pamięć typu 1103-A/układy TTL

Podstawowe parametry statyczne pamięci 1103-A przedstawiono w tablicy 4.47.

Przy łączeniu układów pamięci w bloki o większej pojemności — linie adresowe, linie sygnałów wybierających (CE) oraz sterowania zapisem/odczytem {R/W) doprowadzane są do wielu wyprowadzeń układów pamięci. Linie sygnałów wejściowych w układach pamięci o większej pojemności wnoszą więc znaczne obciążenie pojemnościowe.

Dla przykładu, rozważmy pamięć o pojemności 4096 słów 16-bitowych, składającą się z układów pamięci typu 1103-A (rys. 4.663). W najbardziej niekorzystnym przypadku pojemności wejściowe będą przyjmowały następujące wartości:

— każda z 10 linii adresowych — 64X12 pF — 768 pF,

— każda z 4 linii CE — 16X28 pF = 448 pF,

— każda z 4 linii R/W — 16X19,5 pF = 312 pF,

— każda z 16 linii informacji wejściowej — 4X7,5 pF = 30 pF.

Do tych pojemności należy dodać pojemności montażu.

Prąd ładowania i rozładowania pojemności CL wymagany do zmiany napięcia o wartość A U w czasie At można wyliczyć z zależności:

clau

~ At

Jeżeli CL wyrazimy w pF, U — w woltach i t w nanosekundach, wówczas otrzymamy wartość prądu w miliamperach.

Wyszukiwarka

Podobne podstrony:

Image526 Układy translatorów sygnałów MOS/TTL Wyjścia układów MOS różnią się między sobą w zależnośc

Image527 Układy mogą być wykorzystywane do współpracy z elementami CMOS, RTL itp. Rys. 4.675. Transl

Image572 4.8.8. Układy wyjściowe mocyWzmacniacze mocy sterowane z bramek TTL Moc sygnału wyjściowego

Image510 4.8.2. Układy formowania i regeneracji sygnałów Układy formowania i regeneracji sygnałów

Image532 4.8.5. Układy współdziałające z klawiaturami Klawiaturą nazywa się zespół klawiszy (zestykó

Image561 Układy statycznego sterowania wskaźnikami W statycznych układach sterujących półprzewodniko

Image599 Układy arytmetyczno-logiczne wykonywane są w postaci modułowej, najczęściej o długości logi

Image563 Układy sekwencyjnego sterowania wskaźnikami Schemat ideowy układu sekwencyjnego sterowania

Image516 Jeżeli poziomy napięć sygnałów wejściowych różnią się od wymaganych dla elementów scalonych

więcej podobnych podstron