188

ROZDZIAŁ 9 ■ Magistrale l/O

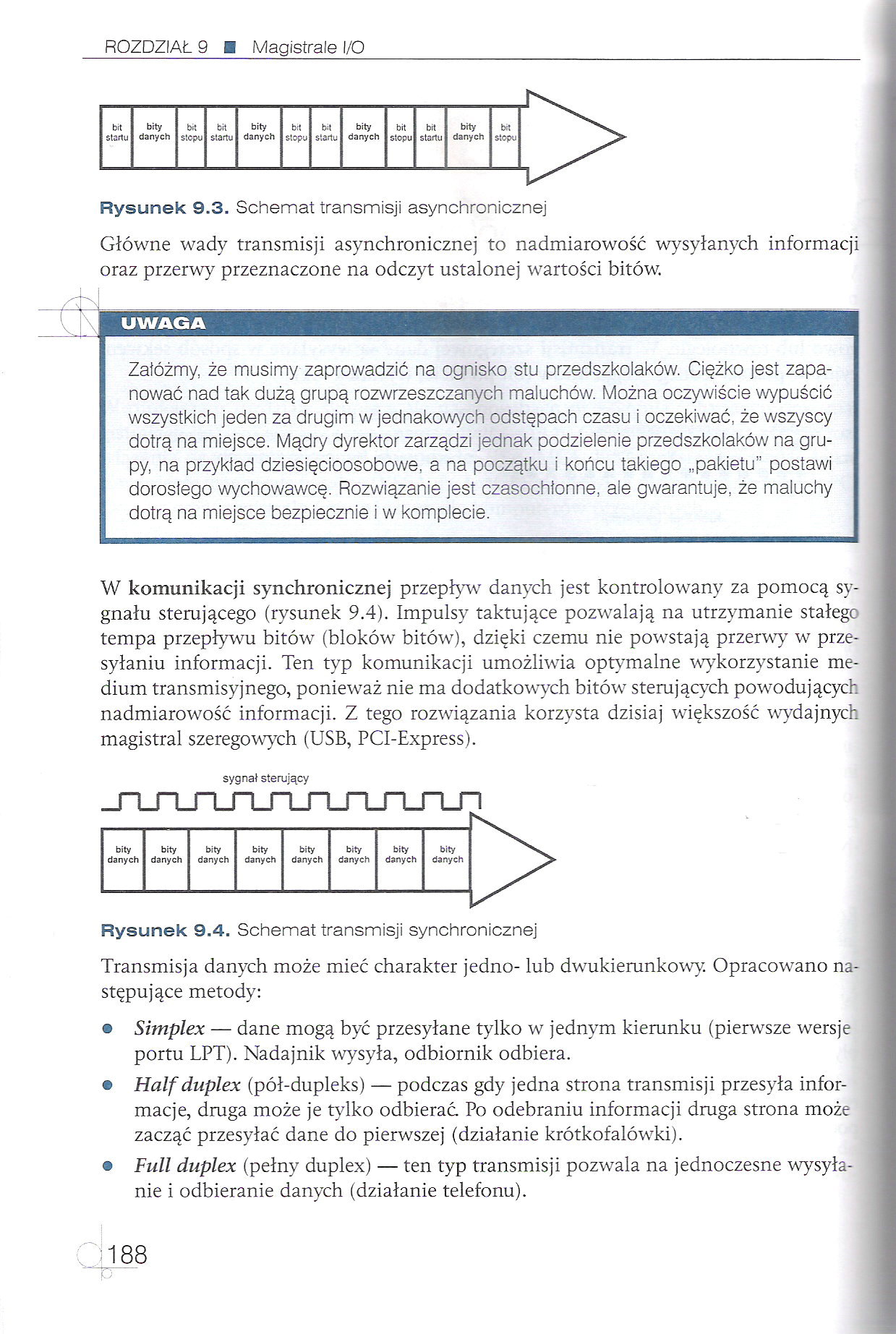

Rysunek 9.3. Schemat transmisji asynchronicznej

Główne wady transmisji asynchronicznej to nadmiarowość wysyłanych informacji oraz przerwy przeznaczone na odczyt ustalonej wartości bitów.

UWAGA

Załóżmy, że musimy zaprowadzić na ognisko stu przedszkolaków. Ciężko jest zapanować nad tak dużą grupą rozwrzeszczanych maluchów. Można oczywiście wypuścić wszystkich jeden za drugim w jednakowych odstępach czasu i oczekiwać, że wszyscy dotrą na miejsce. Mądry dyrektor zarządzi jednak podzielenie przedszkolaków na grupy, na przykład dziesięcioosobowe, a na początku i końcu takiego „pakietu” postawi dorosłego wychowawcę. Rozwiązanie jest czasochłonne, ale gwarantuje, że maluchy dotrą na miejsce bezpiecznie i w komplecie.

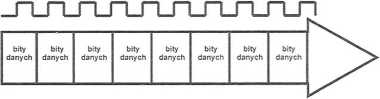

W komunikacji synchronicznej przepływ danych jest kontrolowany za pomocą sygnału stemjącego (rysunek 9.4). Impulsy taktujące pozwalają na utrzymanie stałego tempa przepływu bitów (bloków bitów), dzięki czemu nie powstają przerwy w przesyłaniu informacji. Ten typ komunikacji umożliwia optymalne wykorzystanie medium transmisyjnego, ponieważ nie ma dodatkowych bitów stemjących powodujących nadmiarowość informacji. Z tego rozwiązania korzysta dzisiaj większość wydajnych magistral szeregowych (USB, PCI-Express).

sygnał sterujący

Rysunek 9.4. Schemat transmisji synchronicznej

Transmisja danych może mieć charakter jedno- lub dwukierunkowy. Opracowano następujące metody:

® Simplex ■— dane mogą być przesyłane tylko w jednym kierunku (pierwsze wersje portu LPT). Nadajnik wysyła, odbiornik odbiera.

• Half duplex (pół-dupleks) — podczas gdy jedna strona transmisji przesyła informacje, druga może je tylko odbierać Po odebraniu informacji druga strona może zacząć przesyłać dane do pierwszej (działanie krótkofalówki).

• Fuli duplex (pełny duplex) — ten typ transmisji pozwala na jednoczesne wysyłanie i odbieranie danych (działanie telefonu).

188

v

Wyszukiwarka

Podobne podstrony:

ROZDZIAŁ 9 ■ Magistrale l/O Rysunek 9.18. Złącze interfejsu AMR obok gniazda PCI CNR (ang.

Slajd18 Mostek PL rozdzielenie magistrali PCI i lokalnej asynchroniczne działanie 5 Dekoderów

72277 skanuj0101 (27) Rozdział 4. ♦ Tablice i obiekty 113 Rysunek 4.8. Schematyczna struktura tablic

Rozdział 1 1Z1 w US u Rysunek 1.3. Schemat blokowy otwartego układu sterowania w -

Rysunek 2. Schemat rozdzielania chromatograficznego mieszaniny składającej się z dwóch składników A

img022 22 Rozdział 2 Dla u, £ 6° - (spadek < 10%) można przyjąć C;- C, - 0.8 Rysunek 2-3. Schemat

Foto2894 34 Rozdział 1 Rysunek 4. Schemat blokowy klasyfikacji infrastruktury komunalnej o charakter

107 Rozdział 4. ♦ Systemy cyfrowej transmisji bezprzewodowej Asynchroniczne łącze bezpołączeniowe

66219 skanuj0497 (2) Rozdział 20. ♦ Forum 515 Rysunek 20.1. Przykładowy wygląd głównej strony forum

Rozdział 1. Wprowadzenie Rysunek 1.12. Napęd z silnikiem asynchronicznym klatkowym zasilanym poprzez

o rysunek schematyczny - przedstawia w najprostszy sposób zasady działania lub budowy jakiegoś mecha

więcej podobnych podstron