Elektronikawzad35

w c Hżv6$ki - ELEKTRONIKA W ZADANIACH

C*tić I OblkMnic punktów pracy jirayrnpiów półprrewndnilcowych

Na granicy stanu nasycenia lp = Ib, = 0.107 mA. a zatem na podstawie (1.18.4) mamy:

(U 8.6)

f, _ 0,107 mA-12.86 kii +1,8 V

0,857

U w&, ~ T777Z - 3,7 V

Tak więc tranzystor T pozostaje w stanie aktywnym dla napięcia wejściowego w zakresie 2,1 V £ U we ^ 3.7 V.

Ad 4. Jak sprawdzono dla napięć 0 V < Uwe S 2,1 V tranzystor znajduje się w stanie odcięcia. Prąd kolektora nie płynie, napięcie wyjściowe wynosi + 12 V.

Dla napięcia wejściowego w zakresie 2,1 V < Uwe ^ 3,7 V prąd bazy, a zatem i prąd kolektora liniowo rośnie z napięciem, czyli napięcie wyjściowe liniowo zmienia się od 12 V do 0,2 V. Dla napięć 3,7 V < Uwe ^ 5,7 V przy założeniach upraszczających podanych w temacie napięcie wyjściowe pozostaje na poziomie 0,2 V. Prąd bazy jeszcze się wtedy zwiększa ponad wartość /«,, czyli tranzystor wchodzi głębiej w stan nasycenia i w rzeczywistym tranzystorze napięcie mogłoby jeszcze nieco się zmniejszyć. Dla napięć Uwe £ 5,7 V dioda D spolaryzowana w kierunku zaporowym odcina wejście od reszty układu.

Rys. 1.18.7

Dla Uwe = 0 7. wejścia układu wypływa prąd o wartości 0,64 mA. Dla napięć 0 V < Uwe < 5.7 V prąd ten maleje liniowo do zera. Przy wyższych napięciach wejściowych do punktu A wpływa tylko znikomy prąd wsteczny diody i w sytuacji (jak w temacie zadania), gdy możemy go pominąć nic już od Uwe nie zależy.

Przebieg charakterystyki przejściowej UwY-f(Uwn) pokazano na rysunku 1.18.7 linią ciągłą, a przebieg charakterystyki wejściowej

1we= f (Uwe) linią przerywaną.

Podłączenie drugiego napięcia wejściowego do punktu A przez drugą diodę prowadzi do uzyskania dwuwejściowej bramki NAND, tzn. układu realizującego na dwu logicznych (binarnych, dwuwartościowych) sygnałach wejściowych (w logice dodatniej) funkcję negacji iloczynu logicznego. Napięcie wyjściowe przyjmuje wartość niską(0 logiczne) tylko wtedy, gdy na obydwa wejścia podawane są napięcia o wartości odpowiadającej stanowi 1 logicznej (stanowi wysokiemu, czyli 12 V). Analizowany układ był stosowany w początkowym okresie rozwoju układów logicznych jako podstawowy układ tzw. techniki DTL (ang. diodę -transistor logie).

Zadanie 1.19

o--(*) ►

♦ O, -A* W **•

12.6 k

o—<h o

Dla pokazanego na rysunku układu bramki logicznej DTLZ, przy podawanym na wejście pierwsze napięciu zmieniającym się w zakresie 0 < Uwei ^ 12 V (i „wiszącym" drugim wejściu) należy:

1. wykreślić charakterystykę przejściową U wy = f (

Rys. 1.19.1

2. wykreślić charakterystykę wejściową fw£i = UUwei)\

3. przeanalizować sv jaki sposób na uzyskane w punktach 1 i 2 charakterystyki wpływają trzy możliwe sposoby podłączenia drugiego wejścia (zwarcie z pierwszym wejściem, podłączenie do potencjału zasilania i podłączenie do masy).

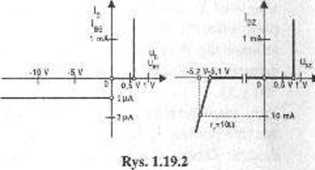

Zakładamy, że (patrz też charakterystyki złącza baza-cmitcr, diod wejściowych i diody Zenera na rysunku 1.19.2 obok):

- w stanie nasycenia tranzystora napięcie Uce wynosi U en* = 0.1 V i nie zależy od wartości prądu I<:;

- złącze baza-emiter tranzystora T znajdującego się w stanic aktywnym można zastąpić spadkiem napięcia Ubk = 0,6 V niezależnym od wartości prądu bazy; prąd zerowy la_o tranzystora jest bardzo mały, możliwy do pominięcia;

- współczynnik wzmocnienia prądowego tranzystora /3 = I (X).

- przewodzącą diodę Dl (i / lub D2) można zastąpić spadkiem napięcia Ud = 0.6 V niezależnym od wartości prądu diody;

- diodę DI (D2 lub złącze baza-emiter tranzystora) przy polaryzacji zaporowej można zastąpić SPM równą lpA;

- przewodzącą diodę Zenera (DZ) można zastąpić spadkiem napięcia Uuz - 0,8 V niezależnym od wartości prądu diody;

diodę Zenera w obszarze przebicia można zastąpić spadkiem napięcia Uz- 5.1 V i rezystancją dynamiczną r-/ = 10

Rozwiązanie

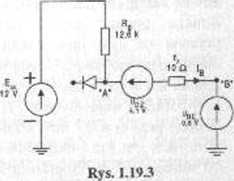

Ad 1. Wyodrębniamy obwód polaryzacji bazy (patrz rysunek 1.19.3) i obliczamy potencjał w punkcie A dla przypadku, gdy do diody wejściowej nie jest podłączone napięcie Uwe. tzn. obydwie diody Dl i D2 „wiszą w powietrzu” W tej sytuacji dioda Zenera pracuje w obszarze przebicia, a przez rczysior Rn, diodę DZ i złącze baza-emiter płynie prąd:

Wyszukiwarka

Podobne podstrony:

Elektronikawzad03 W. Ciązyiuki - ELEKTRONIKA W ZADANIACH Crąić I • OMicnnie punktów pracy przyrządów

Elektronikawzad06 W. Oąłyliski - ELEKTRONIKA W ZADANIACH C}a;ić I. Obliczanie punktów pracy pizynoid

Elektronikawzad10 W.OąŻyttaki ELEKTRONIKA W ZADANIACH Część I - Obliczanie punktów pracy piTyrapiów

Elektronikawzad17 W. Citfyńdci - ELEKTRONIKA W ZADANIACH Crętó I. Obliczenie punktów pracy pre>iz

Elektronikawzad18 W. Ciąayńdti ELEKTRONIKA W ZADANIACH C?ęić I- Obliczanie punktów pracy przyrządów

Elektronikawzad19 W. CmyteU T ELEKTRONIKA W ZADANIACH Cręłć l- Obliczanie punktów pracy przyu^ilów

Elektronikawzad20 w. CiążyAaki - ELEKTRONIKA W ZADANIACH Cxę«< I Oblicnuńe punktów pracy

Elektronikawzad25 W. CiątytaU - ELEKTRONIKA W ZADANIACH C.ręić I: Obliczanie punktów pracy ]irz)xadu

Elektronikawzad34 W. Cwzyński - ELEKTRONIKA W ZADANIACH Częic 1; Obliczanie punktów pracy przyrządów

Elektronikawzad37 w. Ciażyńłki - ELEKTRONIKA W ZADANIACH CzęW 1: Obłiczawc punktów pracy przyrządów

Elektronikawzad40 W. Cnźyński - ELEKTRONIKA W ZADANIACH Czttó 1: Obliczanie punktów pracy przyrządów

Elektronikawzad09 W CiąiyółW - ELEKTRONIKA W ZADANIACH Część 1: Obliczanie punktów pracy przyrządów

Elektronikawzad02 W CiąftyfoM TA EKTRONTKA W ZADANIACH Czcić I Obliczanie punktów pracy przyrządów

Elektronikawzad04 w Citfyński - ELEKTRONIKA W ZADANIACH Część I: Obliczanie punktów piacy przyrządów

Elektronikawzad05 w. CUiyAłki - ELEKTRONIKA W ZADANIACH Cięłć 1: Obliczanie punktów ptacy pnynądAw

Elektronikawzad07 W. Ciąży lulu - ELEKTRONIKA W ZADANIACH Casić 1. ObbczAiiic punktów pnący prcyradó

Elektronikawzad08 W. Ci*tvń*lu - tLhKTRONIK-A W ZADANIACH Czcić 1: Obliczanie punktów pracy przyrapl

Elektronikawzad11 W. CiąiyAsfci - ELEKTRONIKA W ZADANIACII Częśi I: OMiczaiue punktów pr»cy prryradó

Elektronikawzad12 w. CiąrytMki - ELEKTRONIKA W ZADANIACH Cię<Ć I: Obliczanie punktów pnący przyrz

więcej podobnych podstron