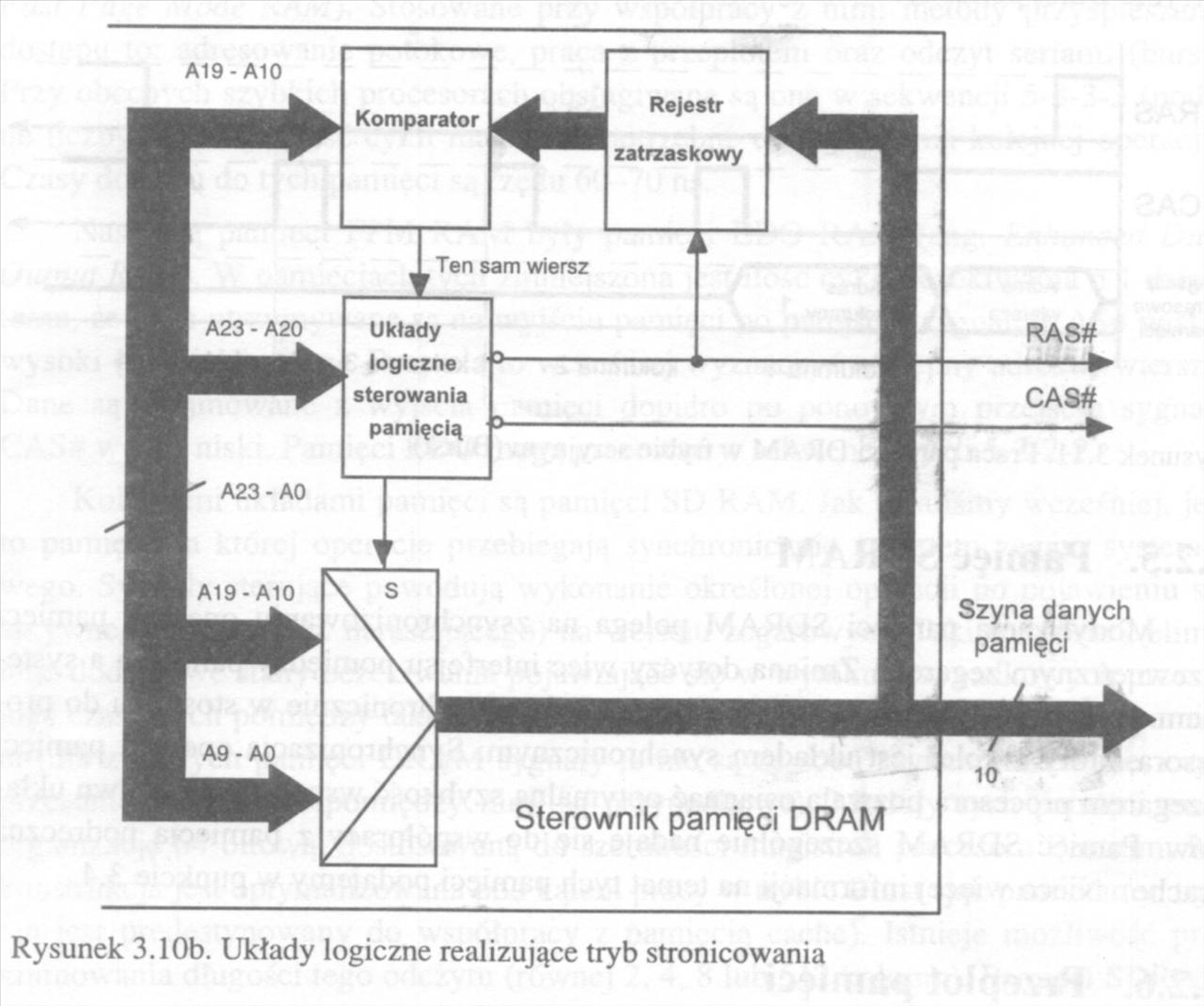

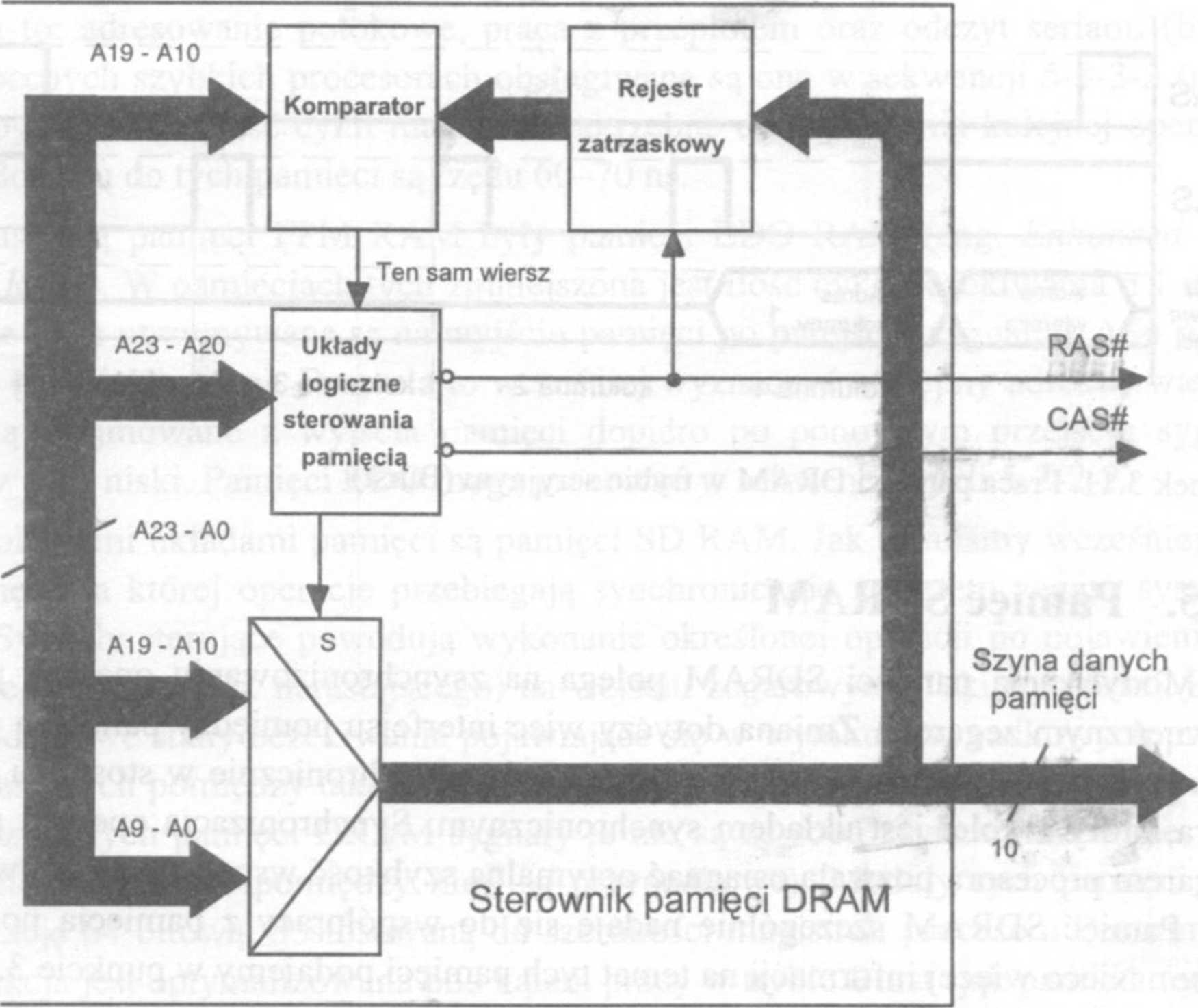

rys 3 10b

Rysunek 3.1 Ob. Układy logiczne realizujące tryb stronicowania

Wyszukiwarka

Podobne podstrony:

rys 4 18 Rysunek 4.18. Układy wejścia/wyjścia współadresowalne z pamięcią operacyjną

rys 3 10a Rysunek 3.10a. Praca pamięci DRAM w trybie stronicowania

uklady logiczne 1 Rys. 1A Realizacja funkcji OR za pomocą dwóch wyłączników i żarówki. Żarówka A zaś

Image641 Załącznik 2 — Układy do realizacji podstawowych funkcji logicznych

Rys. 1. Przykład urządzenia logicznego realizującego funkcję blokady przy osłonie

013 5 Zadanie 2.12. Jałcie funkcje logiczne realizują układy przedstawione na rysunkua. x o-y o- Z O

- układy logiczne sekwencyjne, których zadaniem jest realizacja przebiegu procesu

uklady logiczne 10 o»5V Rys. 10 Wieloemiterowy tranzystor wejściowy w bramce NAND można przedst

uklady logiczne 11 Rys. 11 Schemat obwodu bramki TTL (NAND) z otwartym kolektorem na wyjściu

uklady logiczne 12 Rys. 12 Przerzutnik Schmitta wytwarza sygnał cyfrowy z sygnału analogowego

uklady logiczne 15 Eo-MP I Kanał typu p aJrf -°Q Kanał łypu n felGND.Masa)Rys. 15Obwód inwertera CMO

uklady logiczne 18 Bramko TTl z otwartym kolektorem Bramka CMOS lfco=5V!) =o— Bramka CMOS Bramk

uklady logiczne 2 Rys. 2 Bramka NAND zbudowana z dwóch tranzystorów. Wyjście A przechodzi

uklady logiczne 6 00 01 Q2 03 Rys. 6

uklady logiczne 8 o*5V Rys. 8 W bramkach z serii 74L zastosowano rezystory o większej rezystanc

uklady logiczne 9 Rys. 9 Niskie napięcie nasycenia diod Schottkyego zapobiega w bramkach TTL-S i TTL

rys 2 1 2 2 5 V 2,4V 0,4V 0V Rysunek 2.1. Określenie poziomów logicznych celu zmniejszenia

więcej podobnych podstron