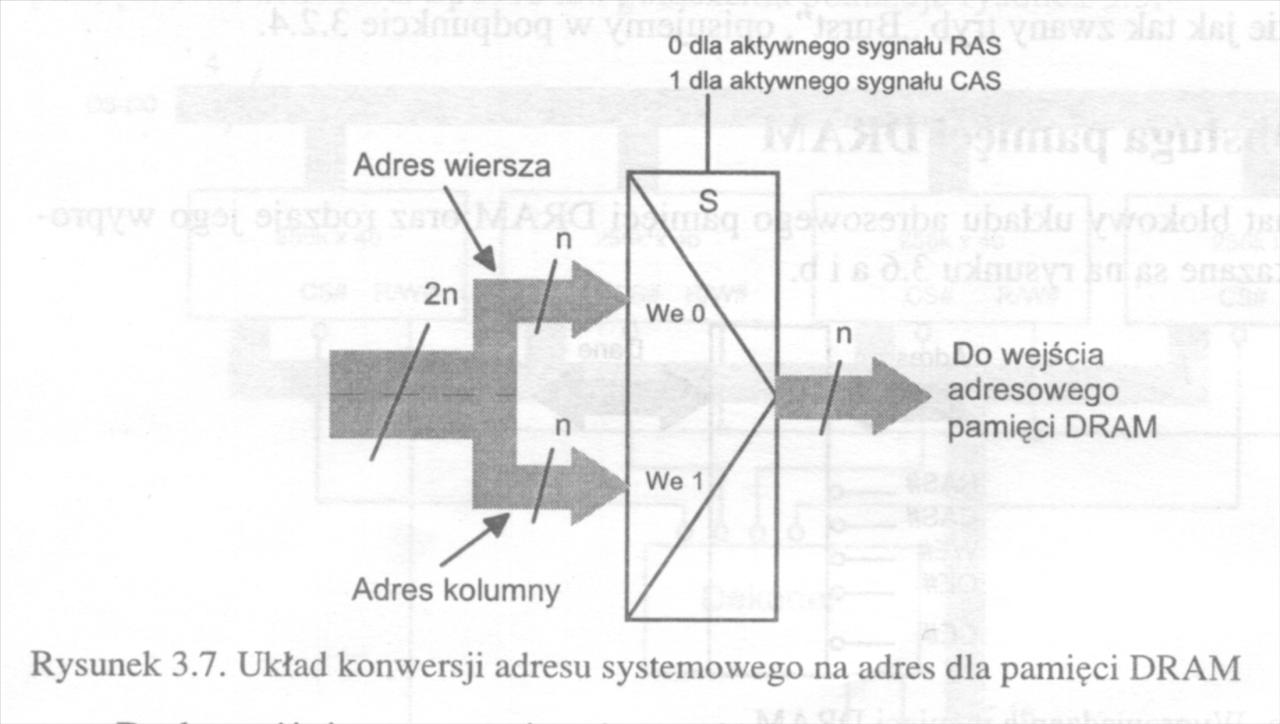

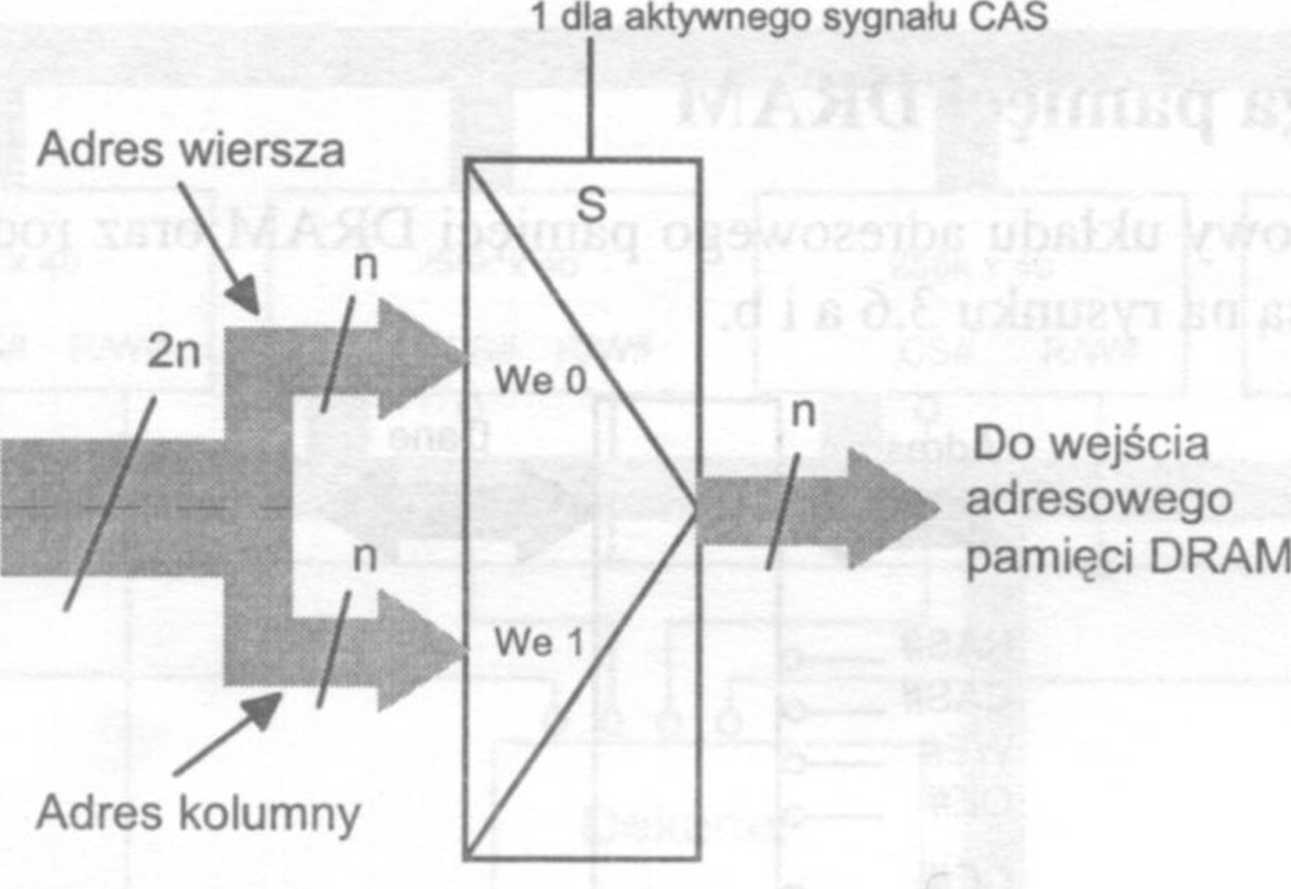

rys 3 7

O dla aktywnego sygnału RAS

Rysunek 3.7. Układ konwersji adresu systemowego na adres dla pamięci DRAM

Wyszukiwarka

Podobne podstrony:

P1050568 (2) Rys. 6. Schemat badanego układu. Proszę połączyć układ według schematu przedstawionego

Rys. 5.37 Rys. 5.38 o + * I •l Wyłącznik świateł o- Prosty układ sygnalizacyjny (lys.

24970 MaszynaW 04 PI P 2 K3 Rys. 1.2. Przebiegi czasowe syg

rys 2 10 Zakodowana liczba 3 0 Wyjście z sygnałem wyróżnionym % Rysunek 2.10. Symbol dekodera w

rys 2 21 Wersja x2Wersja x4 Rysunek 2.21. Sygnały taktujące transmisję danych na magistrali AGP

rys 2 59 Rysunek 2.59. Przykład różnicy w budowie modułu dla pamięci buforowanej i niebuforowanej (d

rys 2 5 we/wy O we/wy 08286 , OE Rysunek 2.5. Układ transcivera (nadajnika/odbiomika) 18286

rys 2 8 Argument A Argument B n - ilość bitów Sygnały sterujące Rysunek 2.8. Symbol jednostki

rys 3 6a Adres RAS# CAS# WE# OE# CE#Rysunek 3.6a. Wyprowadzenia pamięci DRAM

rys 6 2 Gniazdo rozszerzające ISA Rysunek 6.2. Układ przerwań w systemie ISA

81607 skanuj0016 (26) Założony kierunek ruchu *3 Rysunek D-18.6 Gdy założymy, żc układ porusza się j

fotografowanie architektury7 Rys. M Jest bardzo zniekształcony, nienaturalny. Rysunek 8ł pokazuje sz

więcej podobnych podstron