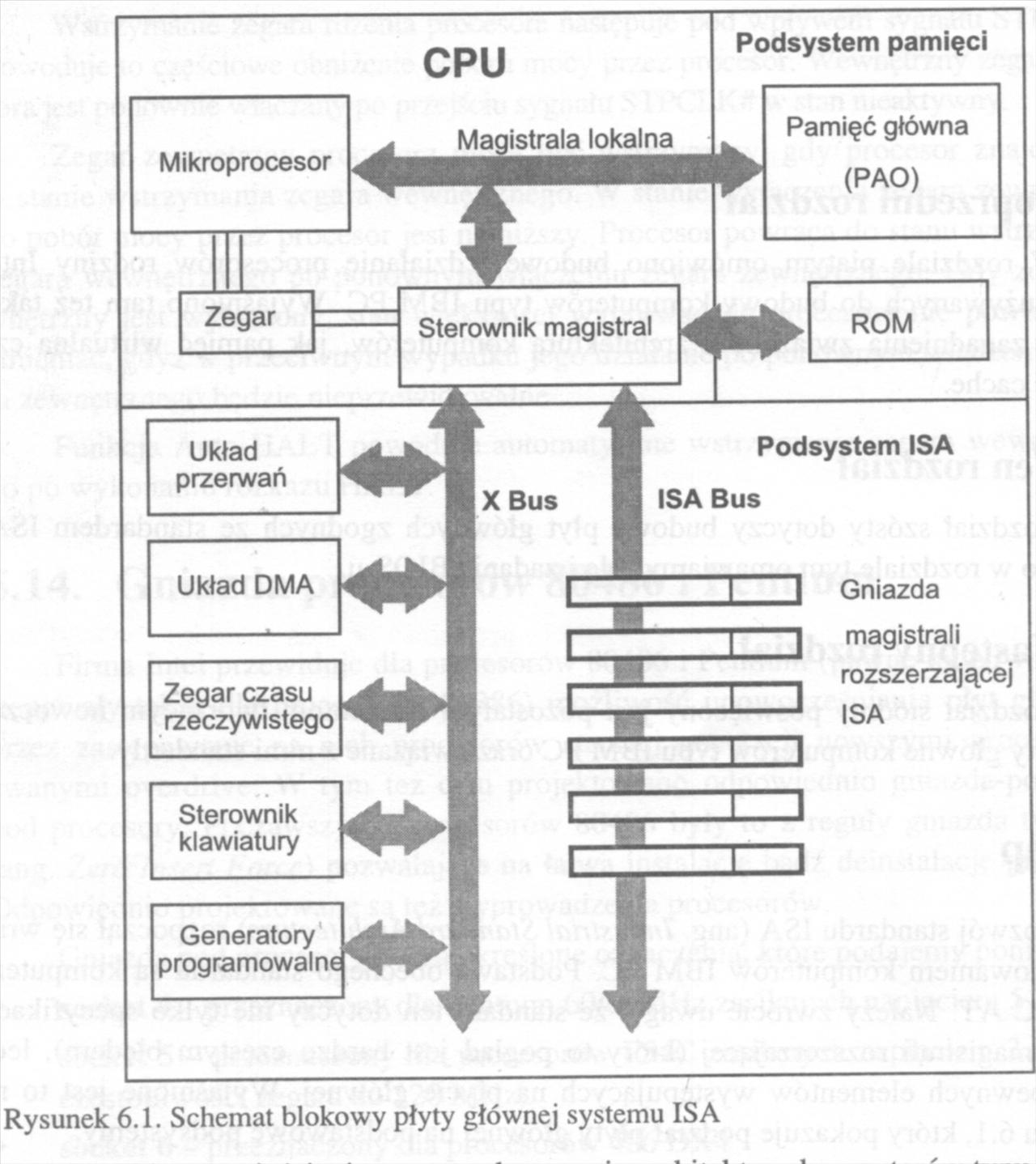

rys 6 1

CPU

Podsystem pamięci

|

Mikroprocesor |

^ Magistrala lokalna |

Pamięć główna | |

|

(PAO) | |||

Sterownik magistral

ROM

Zegar

Układ

przerwań

Podsystem ISA

X Bus

ISA Bus

Układ DMA

Zegar czasu rzeczywistego

Gniazda

magistrali

rozszerzającej

ISA

Sterownik

klawiatury

Generatory

programowaln

Rysunek 6.1. Schemat blokowy płyty głównej systemu ISA

Wyszukiwarka

Podobne podstrony:

rys 6 1(1) CPU (mikroprocesor) Podsystem pamięci Układy sterujące współpracą układów na płycie

rys 2 52 53 Mikroprocesor Magistrala pamięci 200 MHz Rysunek 2.52. Klasyczny sposób komunikacji pami

Slajd13 Magistrala lokalna PCIProcesor Pamięć podręczna ► Pamięć

rys 2 20 CPU Magistrala lokalna Magistrala Karta 528

odczytDRAM rys. 3.3. Cykl odczytu pamięci DRAM

XXX Rys. 4.119 Charakterystyki pamięci a) wyjściowa, b) wejściowi [ns] a b [ns] .t

rys 2 26a b Interfejs pamięci Rysunek 2.26 a. Schemat blokowy akceleratorowej karty graficznej 3D U

rys 5 5 Adres OOOOOh i i Pamięć Początek segmentu (zawartość rejestru segmentowego* 16) 64

rys 6 9 Rysunek 6.9. Mapa pamięci komputera IBM PC z systemem DOS

więcej podobnych podstron