rys 2 52 53

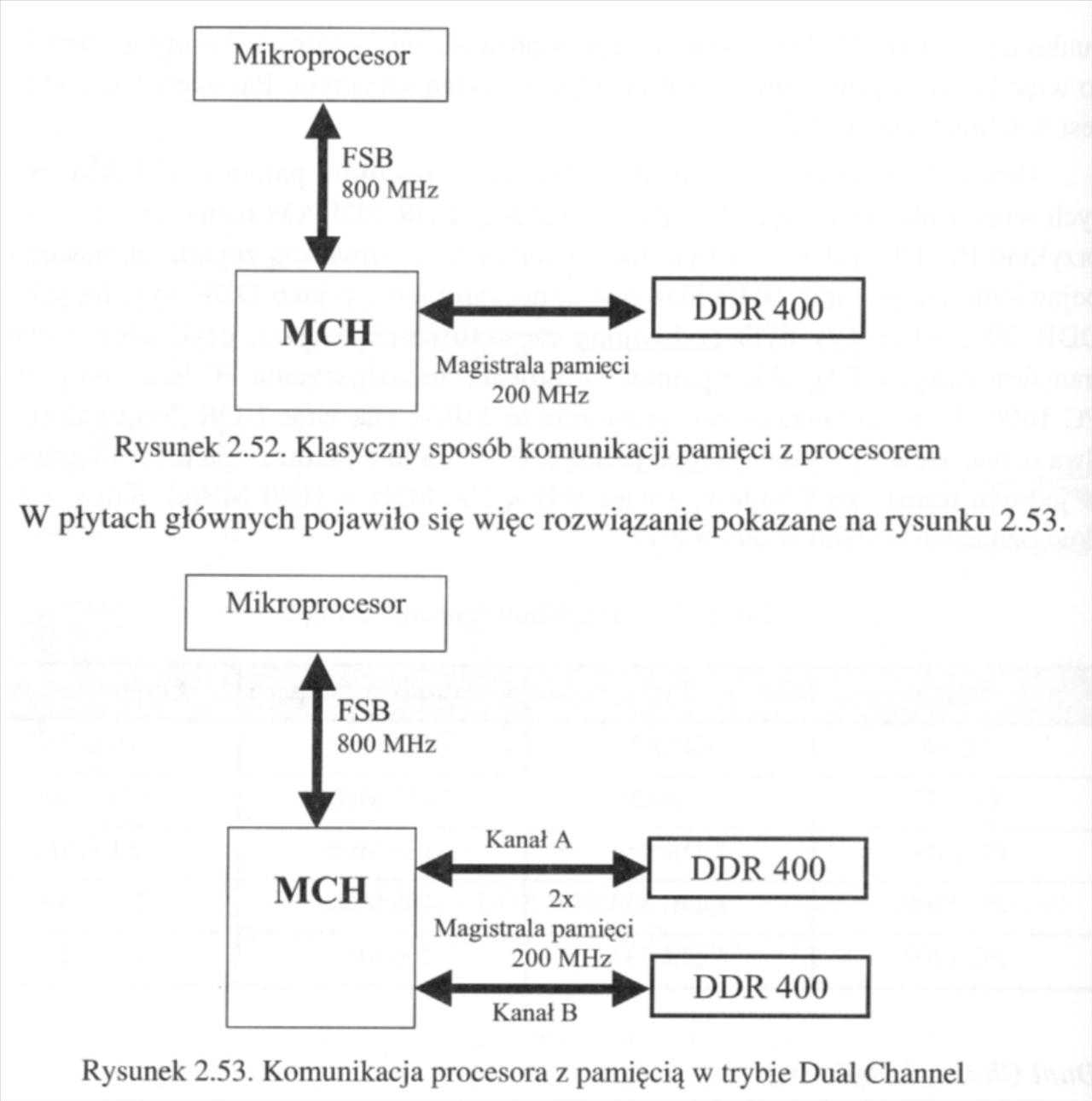

Mikroprocesor

Magistrala pamięci 200 MHz

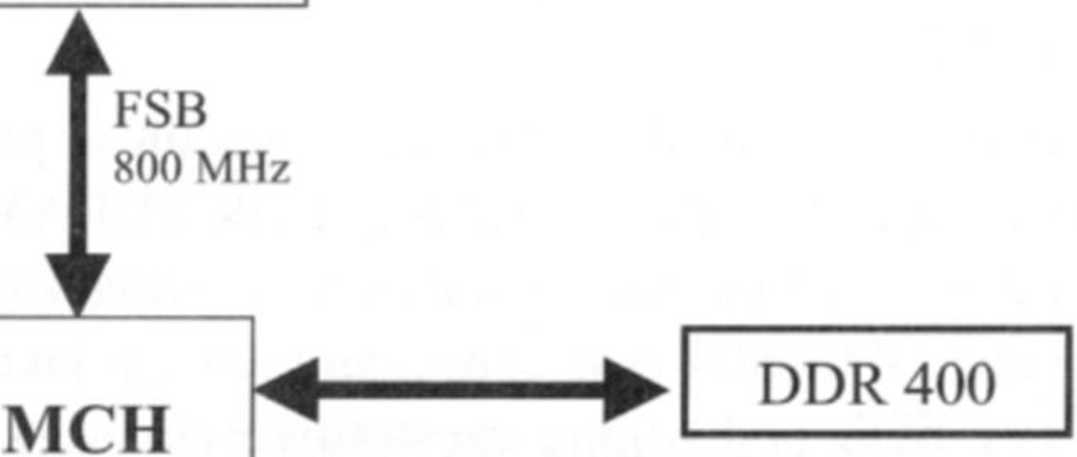

Rysunek 2.52. Klasyczny sposób komunikacji pamięci z procesorem W płytach głównych pojawiło się więc rozwiązanie pokazane na rysunku 2.53.

FSB

800 MHz

|

Kanał A | ||

|

DDR 400 | ||

|

MCH |

2x | |

|

Magistrala pamięci | ||

|

200 MHz | ||

|

DDR 400 | ||

|

Kanał B |

Rysunek 2.53. Komunikacja procesora z pamięcią w trybie Dual Channel

Wyszukiwarka

Podobne podstrony:

rys 6 1 CPU Podsystem pamięci Mikroprocesor ^ Magistrala lokalna Pamięć

fotografowanie architektury$ Rys. 49 Ry*. 50 Rys. 52 Rys. 53 światłocienia. W czasie tak zwanego zac

docu0013 46 50b 50a ^ r 50 50c Rvs. 19 52 / E Rys. 17 j K c d m c a 53

099 2 Rys. 7.52. Kształt otworów na nity Rys. 7,53. Sposób wiercenia otworów w nowych okładzinach sz

rys 6 1(1) CPU (mikroprocesor) Podsystem pamięci Układy sterujące współpracą układów na płycie

Rys 1-3 Wieloprocesor z magistralą i pamięciami podręcznymi Złagodzenie problemu - zastosowanie pami

Image173 (3) PodstawyWspółczesna technika telewizyjna także dla Ciebie Rys. 52 Rys. 53 Transport Str

Slajd11 (121) Uproszczony schemat funkcjonalnyprocesora 1 MAGISTRALA PAMIĘCI Czść sterująca

new 89 182 7. Zasady obliczeń wytrzymałościowych śrub Rys. 7.52. Złącze obciążone siłą P i momentem

082 3 ,M, Rys. 52. Krzywa środków wyporu i cwoluta metacentryczna Kolejne punkty krzywej środków wyp

- Microchip Application Maestro File Edit Tools HelpI^J ggjtleg11(ASII Clock: [200

Układ chłonny (limfatyczny) Rys. 52. Układ chłonny (limfatyczny) 1. żyła szyjna wewnętrzna; 2. węzły

więcej podobnych podstron