image101

►

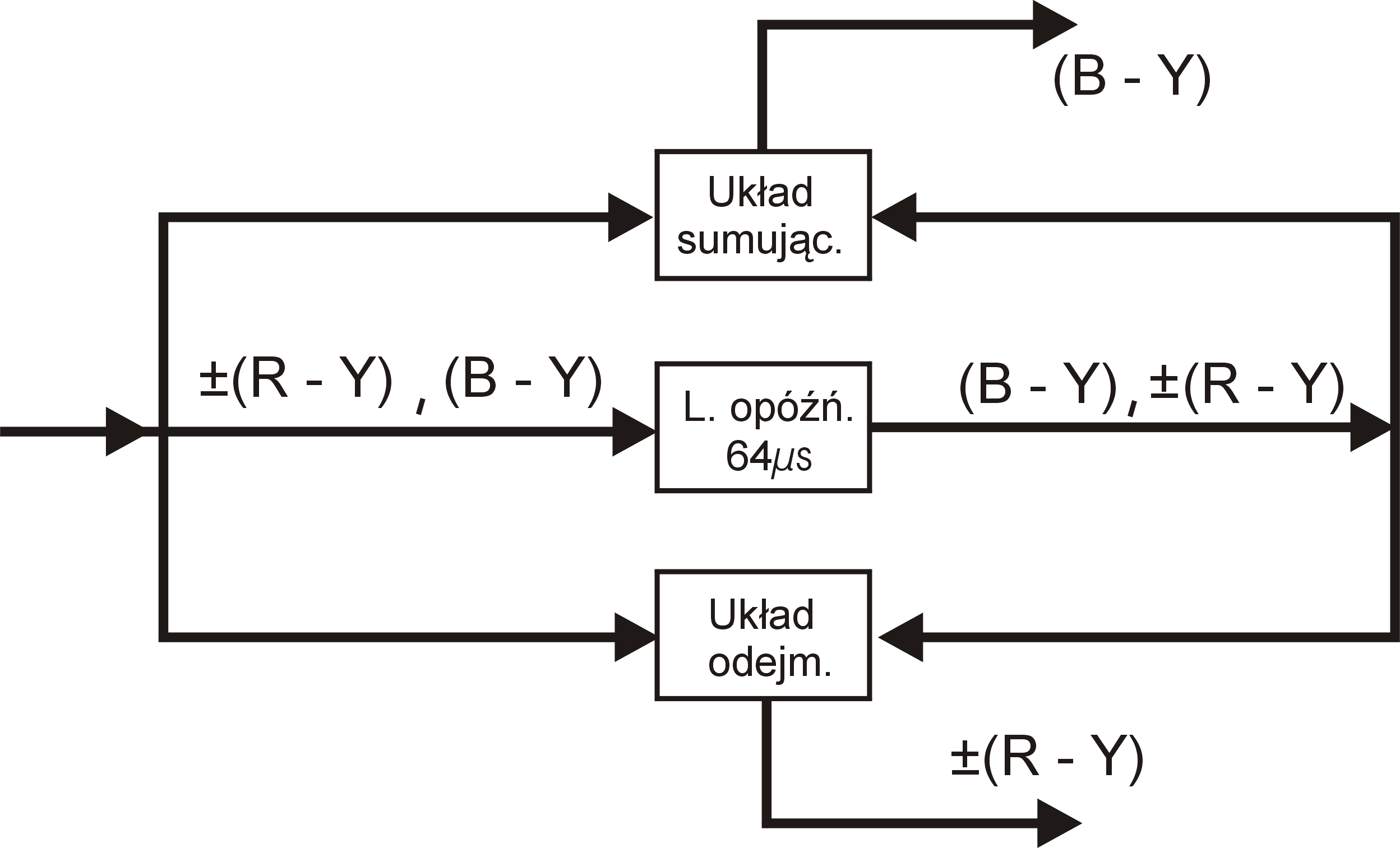

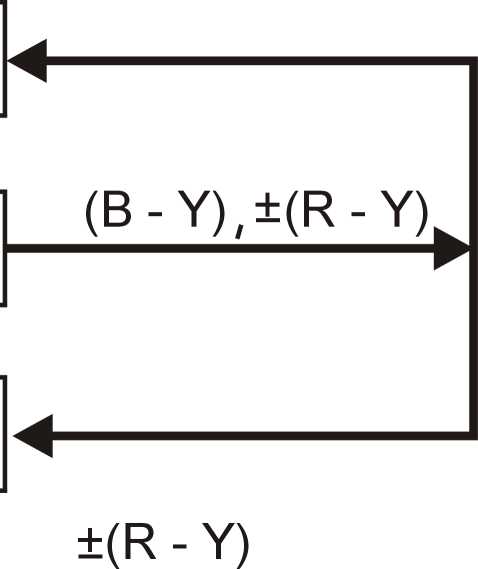

Układ

sumując.

L. opóźń.

64^/s

±(R-Y),(B-Y)

►

Układ

odejm.

►

(B-Y)

►

Wyszukiwarka

Podobne podstrony:

Image101 — układ przesuwania poziomu napięcia, — typowy dla bram

Image17 3.3. Układ mnożący 3.3. a. Wykonać układ mnożący dwie liczby dwubitowe wed

Image1252 n s-b =< a- b,a-b>= 2 (a, - bj) i=1 n ■> n r> n Ta* + Tb* -2 Tarty /=1 /=1 /=1

slide0049 image183 HCATIA V5 - [Przycisk.CATProduct] □ n Start TeamPDM File Edit View Insert lools A

Swarovski Mania (64) A— Ąr START 200o»<r>f 7*<r>«*>vk SWTAt tacoX^C:nB/•*#•■! I

image150 8 jĘj £*» ł* $°%* i*?--

Image174 (3) Podstawy 188f>ytes 1 1_ 13 a— > ł \ adapation fieid

Swarovski Mania (64) A— Ąr START 200o»<r>f 7*<r>«*>vk SWTAt tacoX^C:nB/•*#•■! I

Image133 (3) o o o * o o "*c « o0 0 tf> ®p 4. 9 o 9 ‘Yo0 a° °9 4 o 9 * (, a o* "p0 «>

Image122 a Rys. 4.62 Układ służący do równoległego wprowadzania informacji z czterech źródeł do reje

Image124 Rys. 4.66. Układ służący do równoległego wyprowadzania informacji z rejestru Q

Image134 Adres słowa Rys. 4.80. Układ wprowadzania informacji ze wspólnej szyny do rejestrów równole

Image137 Rys. 4.83 Zespół rejestrów buforowych o pojemności 8 słów 8-bitowych 2 rozdzielacza Rys. 4.

Image183 Struktura logiczna układów FPLA Schemat logiczny typowego układu FPLA przedstawiono na rys.

więcej podobnych podstron