Image40 (11)

Prezentowane urządzenie umożliwia wymianę informacji pomiędzy komputerem PC, a układami wyposażonymi w interfejs Iwire. Początkowo układ miał służyć do sterowania opisanym w poprzednim numerze „Czytnikiem RFID", jednak interfejs umożliwia również współpracę z układami firmy Dallas czy układami opisanymi na stronie http://idom. wizzanione.pl Standardowo magistrala lwirc nic umożliwia współpracy wielu masterów na jednej linii, jednak po kilku modyfika cjach niniejszy układ udostępnia taką funkcję.

Jak to działa?

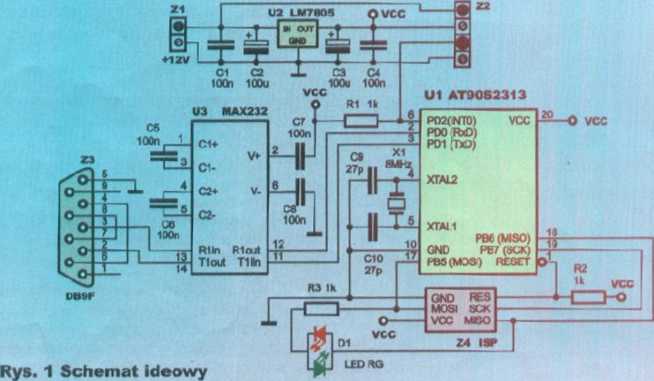

Na rysunku 1 przedstawiono schemat pre zentowanego urządzenia Układ posiada własny stabilizator napięcia 5V (U2), co umożliwia zasilanie różnych układów bezpośrednio z interfejsu. Wymaga to dołączenia zewnętrz nego napięcia zasilania 12V np. z wewnątrz komputera. Jeżeli układ miałby doprowadzone napięcie zasilania 5V, to stabilizator oraz elementy C l, C2 oraz Zł nic muszą być montowane. Sercem układu jest mikroprocesor AT90S2313. Układ ten taktowany jest z zewnętrznego oscylatora kwarcowego XI. Dopasowaniem napięć występujących na wyprowadzeniach procesora do standardu zgodnego ze specyfikacją RS232 zajmuje się dobrze znany układ MAX232 wraz z 4 kondensatorami C5-C8. Na płytce układu zamon towano dodatkowo złącze do programowania mikroprocesora w systemie oraz dwukołoro wą diodę sygnalizacyjną.

Program na mikroprocesor został napisany w języku C i skompilowany za pomocą AVR GCC w bezpłatnym środowisku AVRSide. Program można ściągnąć 2 Elportalu EdW.

Mikrokontroler po niezbędnej inicjalizacji peryferii, w pętli sprawdza dwa warunki: czy odebrano dane do wysłania oraz czy nic minął czas oczekiwania na kolejne bajty do wysłania. Drugi warunek ma na celu automatyczne odrzucenie niepoprawnych ramek

(np. za krótkich).

Dane przesyłane z komputera są odbierane i zapisywane do bufora w procedurze obsługi prze-rwania SIG_U A RT_

RECV (Listing I). Pierwszy wysyłany baji powinien zawierać

ilość bajtów, które mają zostać wysłane na magistralę Iwire, drugi - ilość bajtów, które mają zostać odebrane z tej magistrali, a trzeci - czas (w ms), który ma zostać odczekany po wysłaniu ramki i przed odebraniem danych z interfejsu lwire Dalej przekazywane są bajty do wysłania na linię lwire. Czyli gdy chcemy wysłać do jakiegoś układu następujące dane: OxCC OxED 0x02, a następnie po 32ms odczytać 2 bajty z szyny lwire, to musimy z komputera wysłać następujące dane: 0x03 0x02 0x20 0xCC OxED 0x02. Gdy wszystkie

te dane znajdą się już w buforze, ustawiana jest flaga wyk i mikroprocesor w głównej pętli zaczyna wysyłanie ramki do układów lwire (Listing 2). Zaświecona jest wówczas zielona część diody sygnalizacyjnej.

Na początku niniejszego tekstu wspomniano o możliwości współpracy wiciu układów master na jednej linii. Każda transmisja zaczyna się od wywołania funkcji resctlM). Funkcja ta przed wysłaniem właściwego sy-£ gnału RESET sprawdza, czy linia jest cały czas w stanie wysokim (Listing 3). Jeżeli tak

|

LUting 1 //procedura obsługi przerwania SIGNAT. (SIG_UART_RECV) |

od UART'u |

|

bufor[buff+t) -ODR; |

//zapisz odebrany bajt do bufora |

|

i£(buff>l| //jeżeli odebrano co najmniej jeden bajt to | |

|

i? (buff—bufor [01+3; |

//jeżeli nuner odebraneyo baj tu jee: równy ilości bajtów do wysłania t 3 to; |

|

wyk-l; |

//ustaw flagę wyk |

|

Frzeęel-O; //wyzeruj zmienną służącą do odrzucania wadliwych ranek > | |

Wrzesień 2006 Elektronika dla Wszystkie! Ele

Wyszukiwarka

Podobne podstrony:

Podstawowym warunkiem wymiany informacji pomiędzy komputerami jest sprzężenie ich łączem. Rodzaj uży

Wymiana informacji pomiędzy programami Tekla Structures i Dłubał Ciw, 18 lwł*90 2021 10.00.11:00

Wykład 3Prof. UE.dr hab. Ewa Ziemba Informatyka Trvb interakcyjny to ciągła wymiana informacji pomię

Slajd6 (103) Transmisja bezprzewodowa- IrDa Idea bezprzewodowej wymiany danych pomiędzy komputerami

komunikacyjne dla wymiany informacji bibliograficznej pomiędzy takimi instytucjami. MARC jest mocno

71254 skanuj0487 Rozdział 20.Forum Fora internetowe to niezwykle popularna forma wymiany informacji

Rozdział 11.4. Sygnały w układachautomatycznej regulacji Przekazywanie informacji pomiędzy elementam

Obieg informacji pomiędzy poziomami zarządzania kryzysowego w dniu 11/12 sierpnia 2017 r. w związku

1.6. SYSTEM WYMIANY INFORMACJI O ZAGROŻENIACH POMIĘDZY DANYMI STRUKTURAMI A POWIATOWYM CENTRUM

Egzamin Praktyczny Pisemny 11 (7) Część IZadanie 1. Wymiana gazów pomiędzy powietrzem pęcherzykowat

34 35 (11) Pielęgnacja skory dojrzałej____ •» + system informacyjny. Umożliwia on reagowanie na bodź

Kalendarium Wydarzeń WAT 2008WAŻNE FORUM WYMIANY INFORMACJI MARZEC W dniach 11-13 marca 2008 r. w na

więcej podobnych podstron