TC-S-01 |

Przerzutniki |

|

|

Grzegorz Mazurek Kilian Tomasz Mateusz Forfa |

2011/2012 |

3 EC |

|

|

AGH |

Laboratorium techniki cyfrowej. |

KANiUP |

Przerzutnik (z ang. flip-flop) jest to podstawowy element pamiętający każdego układu cyfrowego, przeznaczonego do przechowywania i ewentualnego przetwarzania informacji. Przerzutnik współtworzy najniższe piętro struktury układu i zdolny jest do zapamiętania jednego bitu informacji. Grupa czterech lub ośmiu połączonych ze sobą przerzutników tworzy następne, wyższe piętro - tzw. rejestr, zdolny już do pamiętania jednego bajtu informacji.

Schemat blokowy przerzutnika:

Przykład złożony z czterech bramek NAND, schemat blokowy:

Zamodelować wykorzystując podstawowe bramki i przebadać struktury przerzutników RS

asynchroniczny z przewagą R.

Tabela charakterystyczna

S |

R |

Qn+1 |

0 |

0 |

Qn |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

0 |

Minimalna postać funkcji Qn+1:

![]()

Tabela prawdy:

Qn |

S |

R |

Qn+1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

Realizacja funkcji Qn+1 na bramkach:

asynchroniczny z przewagą S

Tabela charakterystyczna

S |

R |

Qn+1 |

0 |

0 |

Qn |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

Minimalna postać funkcji Qn+1:

![]()

Tabela prawdy:

Qn |

S |

R |

Qn+1 |

0 |

0 |

0 |

0 |

0 |

0 |

1 |

0 |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

1 |

Qn\SR |

00 |

01 |

11 |

10 |

0 |

0 |

0 |

1 |

1 |

1 |

1 |

0 |

1 |

1 |

synchroniczny RS z przewagą S

Zwykły przerzutnik R-S zmienia swój stan po zmianie stanów wejść S i R. Często jednak pożądane jest, aby zmiana taka następowała synchronicznie z sygnałem zegarowym, czyli taktem. W ten sposób możemy w sieci logicznej uniknąć wielu zakłóceń i hazardów oraz synchronizować poszczególne jej elementy. Wejście zegarowe możemy wyobrazić sobie jako swoisty zamek. Jeśli panuje na tym wejściu stan nieaktywny, to przerzutnik jest zamknięty i zmiana stanu wejść sterujących nic nie powoduje. Dopiero po pojawieniu się stanu aktywnego na wejściu zegarowym, przerzutnik odblokowuje wejścia sterujące i zmienia się zgodnie z tablicą przejść. Zwróć uwagę, iż nie powiedzieliśmy jaką wartość przyjmuje stan aktywny - może to być stan statyczny 0 lub 1 albo stan dynamiczny w momencie zmiany poziomu logicznego z 0 na 1 lub z 1 na 0 (tzw. zbocze narastające i opadające) w zależności od wykonania przerzutnika. Wejście taktujące oznaczamy zwykle literką C (ang Clock - zegar)

wejście zegarowe statyczne; stan aktywny zegara 1;

C |

R |

S |

Qn+1 |

0 |

0 |

0 |

Qn |

0 |

0 |

1 |

Qn |

0 |

1 |

0 |

Qn |

0 |

1 |

1 |

Qn |

1 |

0 |

0 |

Qn |

1 |

0 |

1 |

0 |

1 |

1 |

0 |

1 |

1 |

1 |

1 |

--- |

Tablica charakterystyczna

Tablicy Karnaugha

CS\RQn |

00 |

01 |

11 |

10 |

00 |

0 |

1 |

1 |

1 |

01 |

0 |

1 |

1 |

1 |

11 |

1 |

1 |

1 |

1 |

10 |

0 |

1 |

0 |

0 |

C - zegar

S - wejście set (ustawiające „1”)

R - wejście reset (zerujące „0”)

![]()

Zamodelować wykorzystując podstawowe bramki i przebadać przerzutnik typu zatrzask.

Przerzutnik typu Latch (zatrzask) jest wersją przerzutnika D wyzwalanego nie zboczem, lecz poziomem. W czasie trwania na wejściu zegarowym stanu wysokiego, wyjście Q powtarza stany logiczne wejścia D. W momencie zmiany na wejściu zegarowym stanu wysokiego na niski następuje "zatrzaśnięcie" (zapamiętanie) stanu wejścia D sprzed tej zmiany. Typowym zastosowaniem przerzutnika typu Latch jest zapamiętanie chwilowego stanu szyny danych w celu np. zobrazownia na wyświetlaczu. Dowolny przerzutnik tego typu charakteryzuje się mniejszą odpornością na zakłócenia od dowolnego przerzutnika wyzwalanego zboczem.

Taela prawdy:

E |

D |

Qn+1 |

0 |

0 |

Qn |

0 |

1 |

Qn |

1 |

0 |

0 |

1 |

1 |

1 |

E - wejście sterujące

D - wejście informacyjne

![]()

Zamodelować przerzutnik typu „D” wykorzystując podstawowe bramki i przebadać.

Przerzutnik typu D powstaje w prosty sposób z synchronicznego przerzutnika R-S przez dodanie jednego invertera na wejściu R. Przerzutnik ten ma ogromne zastosowanie w tworzeniu różnych rejestrów oraz liczników. Działanie przerzutnika polega na przenoszeniu stanu z wejścia D na wyjście Q w czasie trwania stanu aktywnego na wejściu C. Gdy wejście wyzwalające przejdzie w stan nieaktywny, przerzutnik zapamiętuje ostatnio ustawiony stan.

C |

D |

Qn+1 |

0 |

0 |

Qn |

0 |

1 |

Qn |

1 |

0 |

0 |

1 |

1 |

1 |

![]()

Porównanie przerzutników typu D i „zatrzask”

Przerzutniki typu D należą do zbioru przerzutników wyzwalanych zboczem. Przepisanie stanu wejścia D (informacyjnego) na wyjście Q następuje w czasie zmiany poziomu logicznego na wejściu zegarowym z niskiego na wysoki. Przerzutnik typu Latch (zatrzask) jest wersją przerzutnika D wyzwalanego nie zboczem, lecz poziomem. (więcej informacji przy opisie przerzutnika typu Latch).

Realizacja „dwójki liczącej” - aby na przerzutniku D zrealizować tzw. dwójkę licząca należy na wejście D podać zanegowany sygnał wyjścia (zrobić sprzężenie zwrotne)

Qn |

D |

Qn+1 |

0 |

0 |

0 |

0 |

1 |

1 |

1 |

0 |

0 |

1 |

1 |

1 |

Przy takiej realizacji przerzutnika układ będzie nam zliczał kolejne takty sygnału zegara.

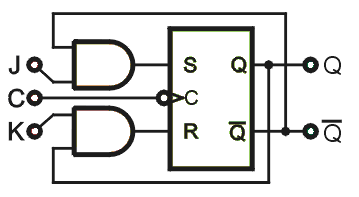

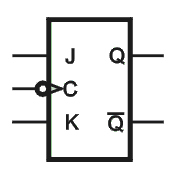

Zamodelować przerzutnik typu „JK” wykorzystując podstawowe bramki i przebadać.

Przerzutnik ten powstaje z synchronicznego przerzutnika R-S wyzwalanego zboczem opadającym po dodaniu dwóch bramek AND. W przeciwieństwie do przerzutnika R-S tutaj wszystkie stany wejść są dozwolone i wywołują dobrze zdefiniowaną zmianę stanów wyjść, co obrazuje tabelka. Wejście J można traktować jako wejście ustawiające, a K jako zerujące. Jeśli na obu wejściach J i K pojawi się stan 1, to przy opadającym zboczu sygnału zegarowego wyjście Q przyjmie stan przeciwny (zmieni się z 1 na 0 lub z 0 na 1).

Tablica charakterystyczna:

J |

K |

Qn+1 |

0 |

0 |

Qn |

0 |

1 |

0 |

1 |

0 |

1 |

1 |

1 |

!Qn |

C |

J |

K |

Qn+1 |

|||||

0 |

0 |

0 |

Qn |

|||||

0 |

0 |

1 |

Qn |

|||||

0 |

1 |

0 |

Qn |

|||||

0 |

1 |

1 |

Qn |

|||||

1 |

0 |

0 |

Qn |

|||||

1 |

0 |

1 |

0 |

|||||

1 |

1 |

0 |

1 |

|||||

1 |

1 |

1 |

!Qn |

|||||

CQn\JK |

00 |

01 |

11 |

10 |

||||

00 |

0 |

0 |

0 |

0 |

||||

01 |

1 |

1 |

1 |

1 |

||||

11 |

1 |

0 |

0 |

1 |

||||

10 |

0 |

0 |

1 |

1 |

||||

Tablicy Karnaugha

![]()

Realizacja „dwójki liczącej” - aby na przerzutniku JK zrealizować tzw. dwójkę licząca należy na wejścia J i K podać logiczną „1”.

Konwersja przerzutnika:

a) „D” za pomocą „JK”

b) „JK” za pomocą „D”

Wyszukiwarka

Podobne podstrony:

PSL-S-01 Przerzutniki

Odpowiedzi 01-14 by Kusio - 2008

TC K 01, funktory, funkcje

2016 05 01 Chciała by zajść

Destiny Blaine [Branded 01] Branded by Sunset (pdf)(1)

PC Cast Partholon 01 Divine by Mistake

Daisy Harris Gods of Hawaii 01 Lei d by the Shark

01 ZNAK (by MaxFILM)

systemy 16 01 2009 by Khazi

Evie Byrne [Faustin Brothers 01] Called by Blood (pdf)(1)

Ava March Bound 01 8/3905

więcej podobnych podstron