198 199

T)H

*1

i iT «■

c*

aj J?

*

o 9 A -P o o •H rM .CO? O 04 H 01 0) Q>

•H d

f^O M t>»

0 M Ot bO

01 qj <D r~i M O

4 -H o- d o ? N o O U «J* -P rH O

a 2 9 * a o

-P bO

o u

aj o

N

0) 01

KN*H CO -O

u"\J>

01 Ph >>o « -p

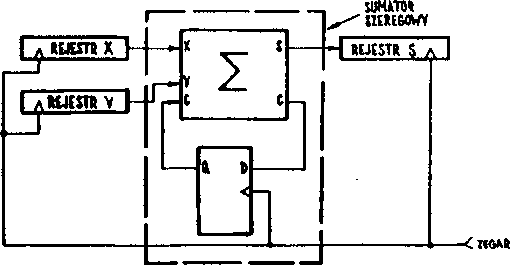

Rys. 5.84-. Sumowanie szeregowe

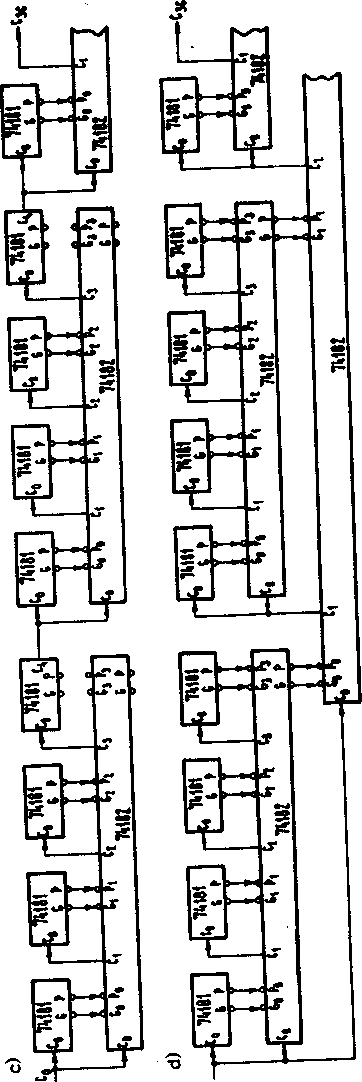

stanowią trzon 4-bltowych arytmometrów (AI0 = Arithmetlc logie Unit) 7^161 Pozostałą część arytmometru 74161 stanowi logika sterująca, umożliwiająca realizację 16 różnych operacji arytmetycznych 1 tyluż logicznych na 4-ch bitach.

Jeżeli czas sumowania liczb wlelobltowych nie jest istotny, bądź liczby te są dostępne tylko szeregowo, to sumowanie może się odbywać za pomocą sumatora sekwencyjnego o grafie podanym w przykładzie 3.1.

Realizując graf typu Uealy'ego otrzymujemy sumator szeregowy jak na rys. 5.84 składający się z sumatora jednobitowego i przerzutnika D wyzwalanego przednim zboczem. Rejestry X,Y,S służą do przechowywania operandów 1 sumy.

Na koniec poświęćmy chwilę czasu odejmowaniu.

Budowanie subtraktorów nie jest w zasadzie konieczne, gdyż - jak pamiętamy - przedstawienie liczb w kodach uzupełniających sprowadza odejmowanie do dodawania. Jednakże w przypadku gdy wynik odejmowania jest zawsze liczbą dodatnią (zawsze odejmujemy liczbę mniejszą od większej) można zbudować prosty subtraktor na bazie sumatora, jak to pokażemy niżej.

Funkcje realizowane przez Jednobitowy subtraktor można, zgodnie z tabelą odejmowania na rys. 5.80, zapisać analitycznie w postaci

(5.7)

Rn = *n © *n ® Bn Bn+1 " Vn + (Jn + VBn

Porównując wzory (5.1) 1 (5*7) lub po prostu tabele dodawania 1 odejmowania stwierdzamy, że zamiana Xg na Zg powoduje zamianę CQ+^ na Ba+1 oraz SQ na Kg. Oznacza to, że za pomocą sumatora i dwóch lnwertorów można zrealizować subtraktor, Jak to pokazano na rys. 5-85a. Zastępując in-wertory bramkami KXCLU3XVE-0R otrzymuje się układ uniwersalny - rys. 5>85b - dodający lub odejmujący zależnie od wartości sygnału sterującego U.Układ

Wyszukiwarka

Podobne podstrony:

skanuj0011 (198) I dykty, a rzeczywistość - szyta grubymi nićmi, co jest jednq z cech -^"litera

12 Spis treści 1.10. Artykuły 198-199 __ML 1.11. Artykuły 200-203

skanowanie0007 (106) 7ifejjjp ii

IMG 44 (3) ssguny WA 1 2sS» * fj ^IT 5 ■ X ____i a«e ; h®=;

NEUFERTX5 index INDEKS Siatka do tenisa stołowego 464 Siatka ^ruciana 198, 199, 204 —, napinani

198 199 1 a »t*m x ł-

198 199 200 201 202 Któro, spośród wymienionych obok zadań, należą do zakresu działania

98 Datka S. 88 Koral«8kl J. 195, 196, 197, 198, 199, 200 Obuohow

Scan044 44 AJ. Fawcett i R.I. Nicolson CO ROBI DLA NAS MÓŻDŻEK? Podnieś kubek z kawą. Wzrokowo śledz

6 (1379) Deklaracje i instrukcje 199 EVERY n udostępniane są wyniki co n-tej analizy; RUNS nl n2 ...

więcej podobnych podstron