44 (31)

88 Pamięć EPROM

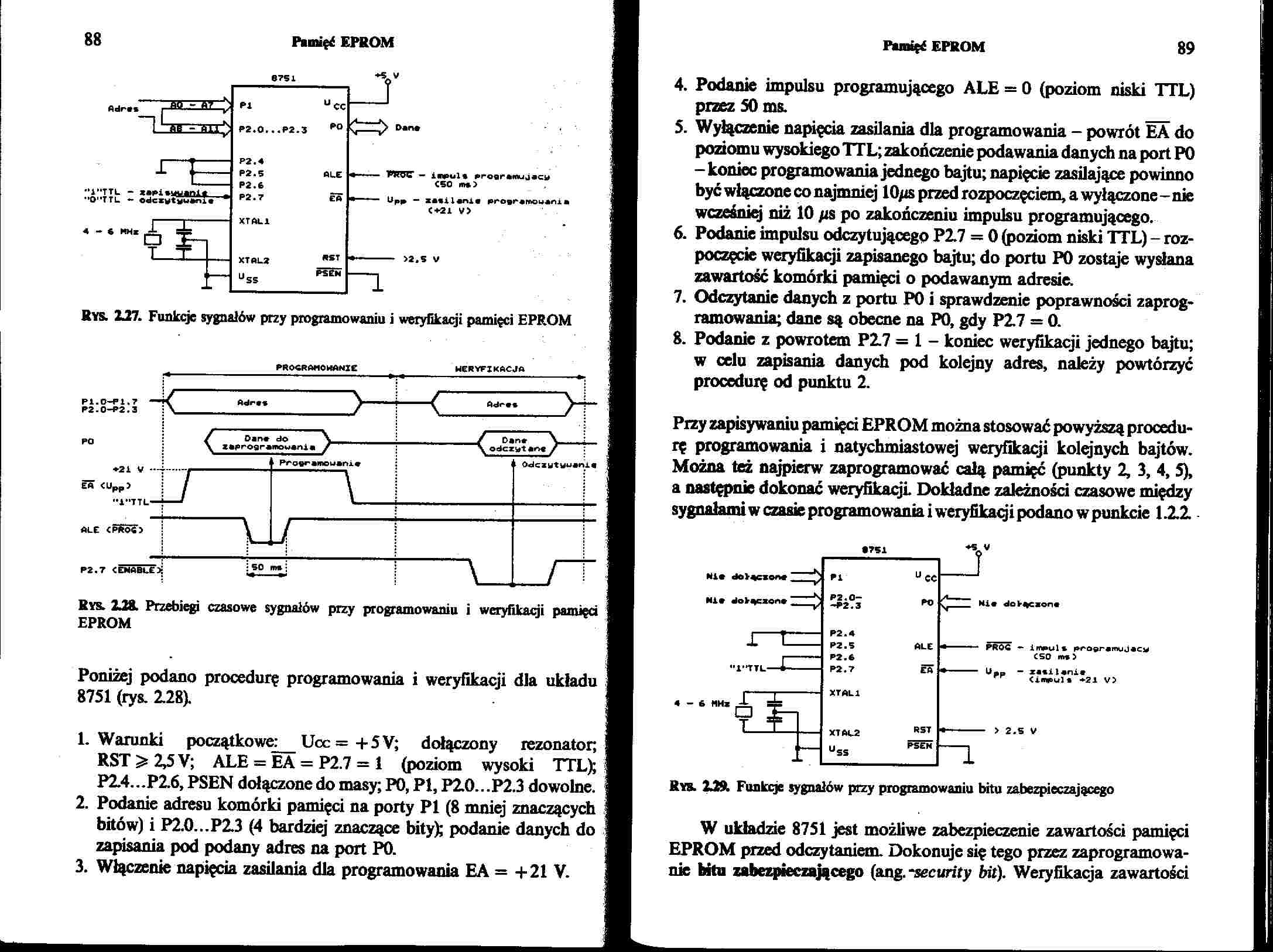

Rys. 227. Funkcje sygnałów przy programowaniu i weryfikacji pamięci EPROM

PROGRAMOWANIE

WERYFIKACJO

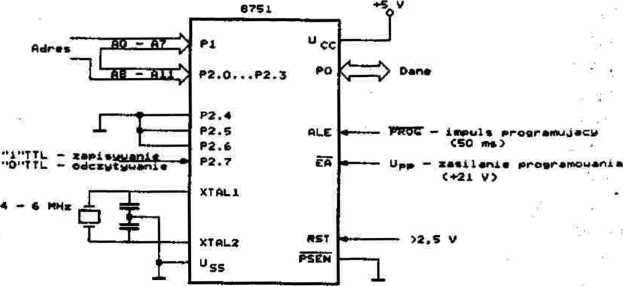

Rys. 228. Przebiegi czasowe sygnałów przy programowaniu i weryfikacji pamięci EPROM

Poniżej podano procedurę programowania i weryfikacji dla układu 8751 (rys. 228).

1. Warunki początkowe: Ucc=+5V; dołączony rezonator;

RST > 2,5 V; ALE = EA = P2.7 = 1 (poziom wysoki TTL); P24...P26, PSEN dołączone do masy; PO, PI, P20...P2.3 dowolne.

2. Podanie adresu komórki pamięci na porty PI (8 mniej znaczących bitów) i P2.0...P23 (4 bardziej znaczące bity); podanie danych do zapisania pod podany adres na port PO.

3. Włączenie napięcia zasilania dla programowania EA = +21 V.

4. Podanie impulsu programującego ALE = 0 (poziom niski TTL)

przez 50 ms. __

5. Wyłączenie napięcia zasilania dla programowania - powrót EA do poziomu wysokiego TTL; zakończenie podawania danych na port PO -koniec programowania jednego bajtu; napięcie zasilające powinno być włączone co najmniej 10/is przed rozpoczęciem, a wyłączone - nie wcześniej niż 10 ps po zakończeniu impulsu programującego.

6. Podanie impulsu odczytującego P2.7 == 0 (poziom niski TTL) - rozpoczęcie weryfikacji zapisanego bajtu; do portu PO zostaje wysłana zawartość komórki pamięci o podawanym adresie.

7. Odczytanie danych z portu PO i sprawdzenie poprawności zaprogramowania; dane są obecne na PO, gdy P2.7 = 0.

8. Podanie z powrotem P2.7 = 1 - koniec weryfikacji jednego bajtu; w celu zapisania danych pod kolejny adres, należy powtórzyć procedurę od punktu 2.

Przy zapisywaniu pamięci EPROM można stosować powyższą procedurę programowania i natychmiastowej weryfikacji kolejnych bajtów. Można też najpierw zaprogramować całą pamięć (punkty 2, 3, 4, 5), a następnie dokonać weryfikacji Dokładne zależności czasowe między sygnałami w czasie programowania i weryfikacji podano w punkcie 1.2.2.

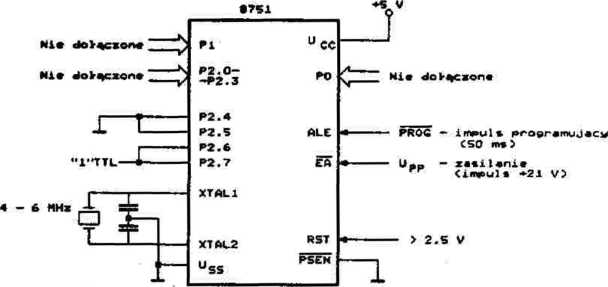

Rys. 139. Funkcje sygnałów przy programowaniu bitu zabezpieczającego

W układzie 8751 jest możliwe zabezpieczenie zawartości pamięci EPROM przed odczytaniem. Dokonuje się tego przez zaprogramowanie hitu zabezpieczającego (ang. ‘security bit). Weryfikacja zawartości

Wyszukiwarka

Podobne podstrony:

metro 31#9 b) c) 1 r—-—i Tp1 n d) Rys. 1.5 Przebiegi czasowe sygnałów

Rys. 4. Wykres funkcji 0pl (M) przy zmiennym obciążeniu ściany i stropu Fig. 4. Graph o/0pl (m) - fu

metro 31#28 Ą CYFROWE POMIARY CZASOWO-CZĘSTOTLIWOŚCIOWYCH PARAMETRÓW SYGNAŁÓW Szczegółowy program

44 (183) 88 Tony Buzan Genialna pamięćUszy Uszy są elementem twarzy, który często umyka uwadze, tymc

y _y — 2, y +y = O (rys. 227). 406. Funkcja parzysta, określona i ciągła w przedziale [—1,1]. Wykres

skanuj0078 (31) 136 B. Cieślar® i u hi Rys. 4.3.2 4.3.5. Projektowani© przekroju poprzecznego Parame

img101 101 Rys. 1.37. Tworzenie sygnału Modulacji czasu trwania impulsów PDM w oparciu o pomocniczą

img172 172 Rys. 1.65. Charakterystyki sygnału cyfrowego: a) przebieg funkcji korelacji własnej, b) p

Rys. 2. Schemat funkcjonalny kalibratora przedstawionego jako przetwornik A/C 2. Miejsce kalibratora

scan 2 (20) kolana I® 1,7-3,2 ^max a Rys. 1. Odkształcenie e w funkcji czasu pełzania f o — przy sta

12.44 31,54 5,40 20,83 5,00 13,80 5,60

31. Wstęp Celem ogólnym jest analiza funkcjonalności portali i serwisów internetowych udostępniający

więcej podobnych podstron