8 (1464)

Proces przetwarzania w przetworniku n-bitowym składa się z Kolejnych kroków. W każdym kroku przetwarzania impuls z generatora zegarowego powoduje przesunięcie w rejestrze przesuwającym stanu logicznego 1 o jedno miejsce (np. w k -tym kroku ak = 1). Stan ten jest wpisywany następnie do odpowiedniego przerzutnika rejestru wyjściowego (bk = 1), powodując przyrost napięcia kompensującego na wyjściu przetwornika C/A o wartość A Uk - UK/2k, przy czym napięcie odniesienia UR jest równe pełnemu zakresowi przetwarzania. W każdym kroku przetwarzania aktualna wartość napięcia kompensującego jest porównywana z napięciem U/ i w zależności od wyniku porównania zostaje ustalony stan przerzutnika bk w rejestrze wyjściowym. Jeśli Uk > V,, to przerzutnik bk pozostaje 1 i odpowiadająca mu składowa napięcia kompensującego UJ2k jest nadal włączona jako składnik napięcia Uk przy następnych porównaniach. Natomiast, gdy Uk < Ur to następuje skasowanie przerzutnika (bk = 0) i w ten sposób wyłączenie odpowiadającej mu składowej napięcia Uk. Stan logiczny 1 w rejestrze przesuwającym jest przesuwany o jedno miejsce (ak =0, aktl = 1) i rozpoczyna się następny krok przetwarzania, w którym napięcie Uf jest porównywane z kolejną wartością napięcia Uk, zwiększoną w stosunku do poprzednio ustalonej o AUk - UJ2iłl.

Wartość napięcia kompensującego Uk po n krokach przetwarzania można więc wyrazić wzorem

A Ur Uk = Ybk —

k U 1 2k

gdzie bk = 1, jeśli wartość napięcia Uk po &-tym kroku jest mniejsza od jeśli

U,, czyli

lub rów-

oraz bk = 0, jeśli wartość Uk po A:-tym kroku przetwarzania jest większa na Ur czyli jeśli

i=l

2‘

W ten sposób po n krokach przetwarzania, cyfrowa zawartość rejestru wyjściowego jest z dokładnością UJ2" równoważnikiem analogowej wartości napięcia Uj i może zostać przekazana do urządzeń zewnętrznych.

Zaletą metody kompensacji wagowej jest krótki czas przetwarzania. Ponieważ przetwornik n -bitowy wymaga tylko n kroków przetwarzania, więc czas ten jest równy nTc (gdzie Tc — czas trwania jednego kroku) i jest niezależny od wartości napięcia przetwarzanego. Wadą metody, mającej znaczenie w niektórych dziedzinach zastosowań, jest duża nieliniowość różniczkowa, uwarunkowana właściwościami przetwornika C/A. Niemonotoniczność charakterystyki przetwornika A/C może być przyczyną brakujących kodów (czyli tzw. dziur kodowych) w charakterystyce całego przetwornika A/C.

Metoda kompensacji ró\ Amiernej

Przetwornik z kompensacją równomierną działa podobnie jak układ z kompensacją wagową z ią różnicą, że równoważenie napięcia Ur odbywa się za pomocą równomiernych przyrostów AUk o wadze najmniej znaczącego bitu.

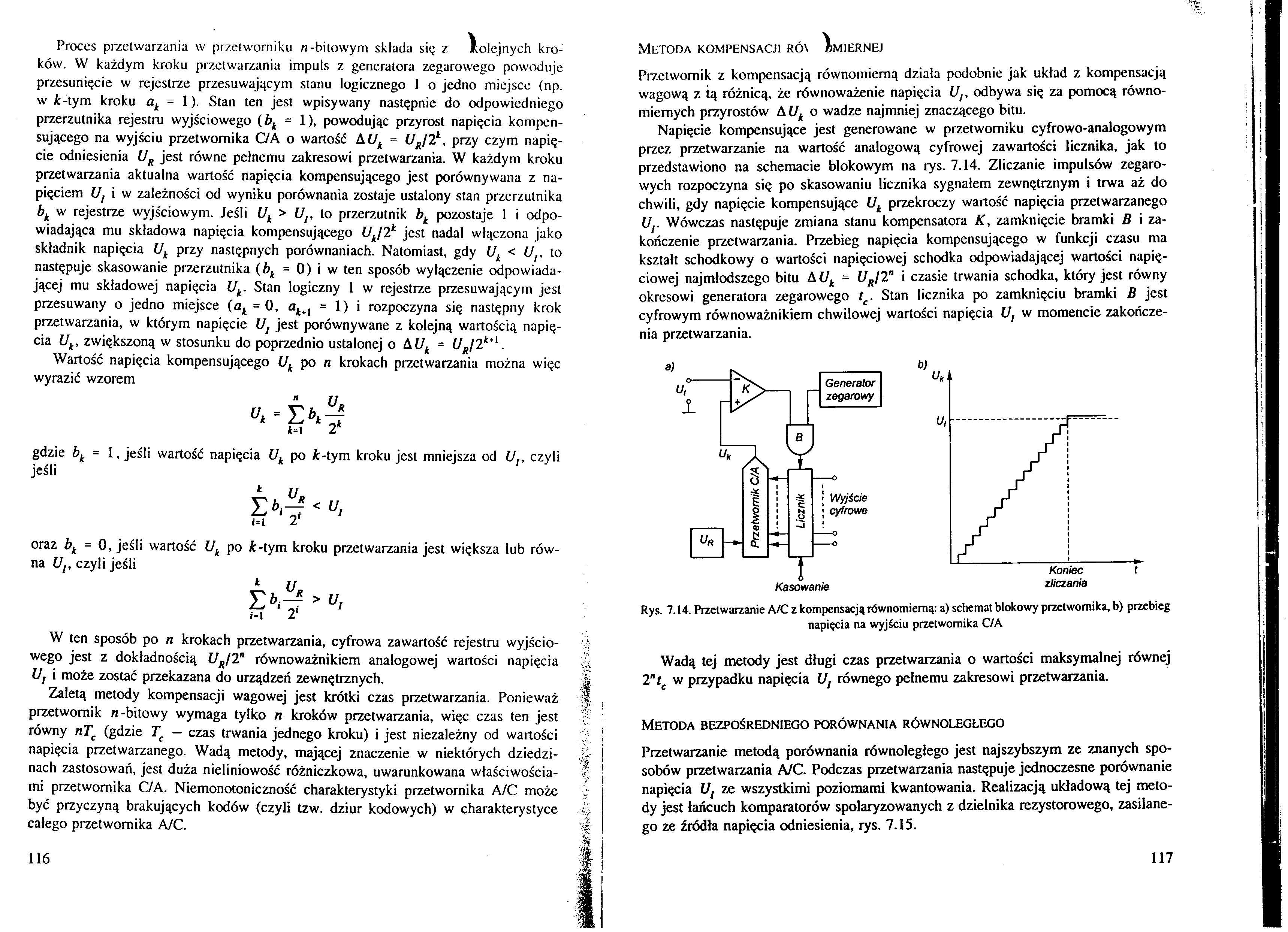

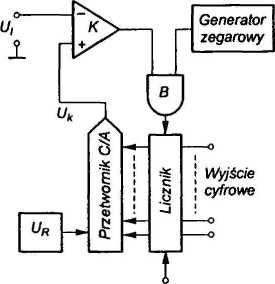

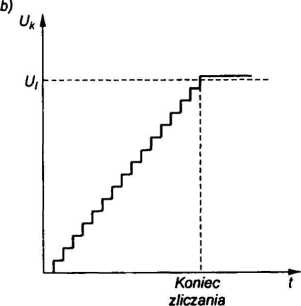

Napięcie kompensujące jest generowane w przetworniku cyfrowo-analogowym przez przetwarzanie na wartość analogową cyfrowej zawartości licznika, jak to przedstawiono na schemacie blokowym na rys. 7.14. Zliczanie impulsów zegarowych rozpoczyna się po skasowaniu licznika sygnałem zewnętrznym i trwa aż do chwili, gdy napięcie kompensujące Uk przekroczy wartość napięcia przetwarzanego Ur Wówczas następuje zmiana stanu kompensatora K, zamknięcie bramki B i zakończenie przetwarzania. Przebieg napięcia kompensującego w funkcji czasu ma kształt schodkowy o wartości napięciowej schodka odpowiadającej wartości napięciowej najmłodszego bitu AUk = UKI2" i czasie trwania schodka, który jest równy okresowi generatora zegarowego tc. Stan licznika po zamknięciu bramki B jest cyfrowym równoważnikiem chwilowej wartości napięcia U, w momencie zakończenia przetwarzania.

Rys. 7.14. Przetwarzanie A/C z kompensacją równomierną: a) schemat blokowy przetwornika, b) przebieg napięcia na wyjściu przetwornika C/A

Wadą tej metody jest długi czas przetwarzania o wartości maksymalnej równej 2"te w przypadku napięcia U, równego pełnemu zakresowi przetwarzania.

Metoda bezpośredniego porównania równoległego

Przetwarzanie metodą porównania równoległego jest najszybszym ze znanych sposobów przetwarzania A/C. Podczas przetwarzania następuje jednoczesne porównanie napięcia l/y ze wszystkimi poziomami kwantowania. Realizacją układową tej metody jest łańcuch komparatorów spolaryzowanych z dzielnika rezystorowego, zasilanego ze źródła napięcia odniesienia, rys. 7.15.

117

Wyszukiwarka

Podobne podstrony:

196 ARTYKUŁY rozumiany jako proces, na który składają się kolejno: gromadzenie, opracowywanie,

Slajd10 (123) Jak działa procesor - podstawy Cały cykl procesora składa się z następujących kroków P

195 Wpływ motywowania pracowników na... Standardowy proces budowy systemu motywacyjnego składa się z

10517384?2391313491606F51361771323497689 o 1.2 Metodologia Proces Analizy Drzewa Niezdatności składa

91 (126) PRZEMYSŁ SŁODOWNICZY - SUSZENIE SŁÓD Na proces suszenia słodu mokrego składają się trzy faz

Budowa oka Układ wzrokowy Widzenie jest złożonym procesem fizyczno-psychicznym, który składa się z

Prawo materialne i formalne (procesowe) • na prawo materialne składają się normy

DSC02633 2 Zjawiska i procesy finansowe zachodzące w przedsiębiorstwie składają się na

RUP ■ Proces budowy systemu informatycznego składa się z dyscyplin, z których

PB100055 Na proces uzyskiwania bloku z calizny składają się etapy: 1. odspojenie d

Proces zarządzania finansami firmy Proces zarządzania finansami firmy składa się z dwóch zasadniczyc

granitów i gnejsów, oraz ze trzeciorzędu. 1/jZacjTodzi tu gwałtowna Składają się z kolejnych,

CIMG1748 «rroces sterowania przepływem produkcji Proces sterowania przepływem produkcji składa się z

więcej podobnych podstron