CCF090613�029

16.2.9. Pętla PLL

Pętla PLL (ang. Phase Locked Loop) jest to układ elektroniczny o schemacie funkcjonalnym przedstawionym na rys. 16.8. W jego skład wchodzą:

• detektor fazy,

e filtr dolnoprzepustowy (FDP),

• wzmacniacz,

• generator przestrajany napięciem (VCO).

Pętla stanowi układ ze sprzężeniem zwrotnym. Jej zadaniem jest wytworzenie w generatorze VCO przebiegu, którego częstotliwość będzie równa częstotliwości sygnału wejściowego, ale jego faza będzie przesunięta o kąt nil.

Rys. f 6.8. Pętla PLL

Detektor fazy porównuje fazy obu tych sygnałów. W uproszczeniu można przyjąć, że jest to kluczowany przełącznik analogowy załączany zewnętrznym przebiegiem sterującym. Przekazuje on sygnał wejściowy na swoje wyjście — gdy sterujący go przebieg z generatora VCO ma wartość dodatnią, natomiast odcina wejście od wyjścia — gdy sygnał sterujący przyjmuje niski poziom.

0 UA

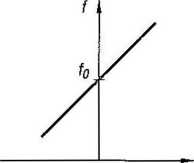

Filtr dolnoprzepustowy FDP pełni w pętli PLL funkcje układu całkującego. Napięcie uzyskane na wyjściu tego filtru, po wzmocnieniu we wzmacniaczu, steruje częstotliwością generatora VCO. Na rysunku 16.9 przedstawiono przykładową charakterystykę generatora sterowanego napięciem. Jest ona tak dobierana, aby zwiększaniu napięcia wejściowego towarzyszyło zwiększanie częstotliwości sygnału wyjściowego (zwiększanie fazy), a zmniejszaniu napięcia wejściowego — zmniejszanie częstotliwości sygnału wyjściowego (zmniejszanie fazy). (W tym miejscu należy przypomnieć, że zmiana częstotliwości generowanego przebiegu pociąga za sobą zawsze zmianę jego fazy.) Jeżeli na wejście generatora VCO podamy napięcie równe zeru, to generuje on sygnał o częstotliwości drgań swobodnych f0. Przebieg wyjściowy z generatora jest zwykle prostokątny. Regulację generowanych częstotliwości uzyskuje się przez zmianę wydajności źródeł prądowych (regulowaną za pomocą wejściowego napię-

Rys. 16.9. Przykładowa charakterystyka generatora VCO

369

24 — Podstawy elektroniki, cz. II

Wyszukiwarka

Podobne podstrony:

Układy z fazową pętlą sprzężenia zwrotnego, często nazywane pętlami fazowymi PLL fang. phase - locke

Slajd23 (16) DROSOPHILA MELANOGASTER Droso phi la melanogaster - (ang. fruitfiy), muszka owocówka. J

System operacyjny DOS DOS (ang. Disc Operating System) jest to 16-bitowy jednozadaniowy system

Image397 Generator funkcji większości Układ generujący funkcję większości (ang. Majority-Vote Circui

1 (533) (ang Direct Numencal Contro!), jest to system sterowań szeregiem obrabiarek sterowanych nume

DSC00066 138 kulturowej (ang. gender}. Innymi słowy, jest to okre podmiotowość projektowana w ten sp

7 (537) Rastrowe formaty plików PNG - *.png (ang. Portablc NetWork Graphics) - jest to oficjalny nas

ŚWIAT PRZEDSZKOLAKA CZYLI CO PRZEDSZKOLAK WIEDZIEĆ POWINIEN (16) Europ* pokojowa I bez granic ■ dl*

CMS - co to jest i po co... System zarządzania treścią (ang. ContentManagement System, CMS) jest to

1tom197 7. ELEKTRONIKA396 Phase-Locked Loop). Miarą stabilności częstotliwości jest wartość względna

DSC00058 (4) Równania (3.4.16) i (3.4.37) można upisai

<6.Informatyka + Jeśli używana jest pętla lokalna analogowa, a nie cyfrowa, potrzebny jest modem.

więcej podobnych podstron