DSCN5251 (4)

|

MIPS |

1 |

Op" |

Rsf |

| Rtf1 |

i . i 1 | |

|

31 |

28 27 |

20 10 |

16 15 12 11 | |||

|

ARM |

l |

Opn* | |

Op* |

■ * |

' | Rd‘ | CM* | |

|

31 |

26 |

25 |

21 20 |

16 15 | ||

|

MIPS |

Qp” |

Rsl5 |

Rd5 |

Const1* |

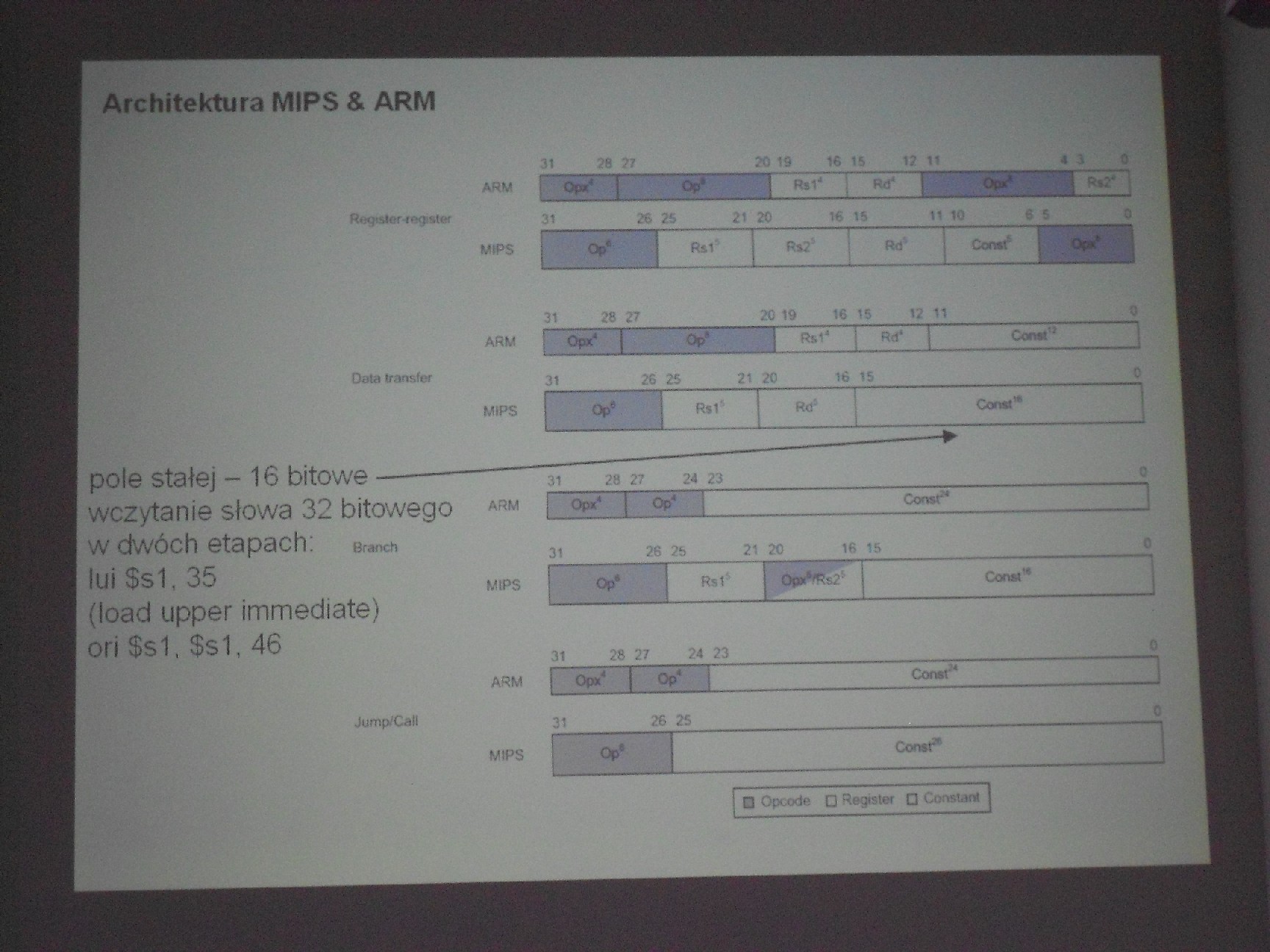

pole stałej - 16 bitowe ■ wczytanie słowa 32 bitowego w dwóch etapach: Branch

lui $s1, 35

(load upper immediate) ori $s1, $s1, 46

Jump/Call

31 28 27 24 23

26 25 21 20 16 15

Op*

Cm”

Op*

j □ Opcode Q Register □ Constant I

Wyszukiwarka

Podobne podstrony:

DSCN5252 (3) Architektura MIPS ładowanie z pamięci do rejestru Iw StO. offset! $t2)

DSCN5253 (3) Architektura MIPS - Ładowanie z pamięci do rejestru Iw $t0. offset($t2)

DSCN5254 (5) Architektura MIPS - operacja na rejestrach add $t0. St1. St2 t0=t1 +t2

DSCN5255 (3) Architektura MIPS - operacja na rejestrach add $t0. $t1. $t2 t0=t1 +t2 1. &

DSCN5257 (3) Architektura MIPS - skok bezwarunkowy l. Pobranie instrukcji z pamięci i PC=PC+4 inswua

DSCN5247 (4) Stos i wywoływanie funkcji w arch. RISC - MIPSW oryginalnej architekturze MIPS brak ins

DSCN5256 (5) w słowach 32b) Architektura MIPS skok warunkowy beq $t0. $t1. adres-przesuniecie ««* MI

DSCN5317 (4) Miary wydajności: MIPS - million instructions per secondInstmction _ count Execution _

b bQ UA5C OUs, 0J1J1, vnus a.op m AU UM3CT 31 Pul , Vd , LU 5 PU t>>ej ? * ouu. ,

CCF20080702�010 42KOŚĆ KRZYŻOWA(Os sacrum seu os sacrale) Powstaje ze zrośnięcia 5 kręgów krzyżowych

s22 252525252B23 o o oS+erwe. iw-> mit plaslischcr Mittc MOT!VOUA<H-MESSl A <A 10 cm MATERI

Ryszard Kopittke Architektura i urbanistyka Biskupiej Góry w Gdańsku WMG VIDEO Gdańsk 31.01.2018 + -

»n 20 11 16 Ul 11 i0 % (o 2 0 Podyplomowe Studium Architektury

10 , u • 16 • 1<i • U 10 % ■■ - Z - /c Podyplomowe Studium Architektury

10 mieszkalny architektura Przekroj? Foto DdfOQf?epu«galna mm.lOOO(Vm2/24h y/ęłna frioy^v%a • 20 cm

Zdjęcie067(2) 50 % wag. 60 i Hj •to P 30{ / /7"-rtCaO i S Fe2 Os i f 20 i 9 # / i & * * «

Oś gwintu H=0,86603P Rys. IV-31. Zarys podstawowy gwintu metrycznego ISO wg normy PN-60/M-02013 Rys.

więcej podobnych podstron