DSCN5255 (3)

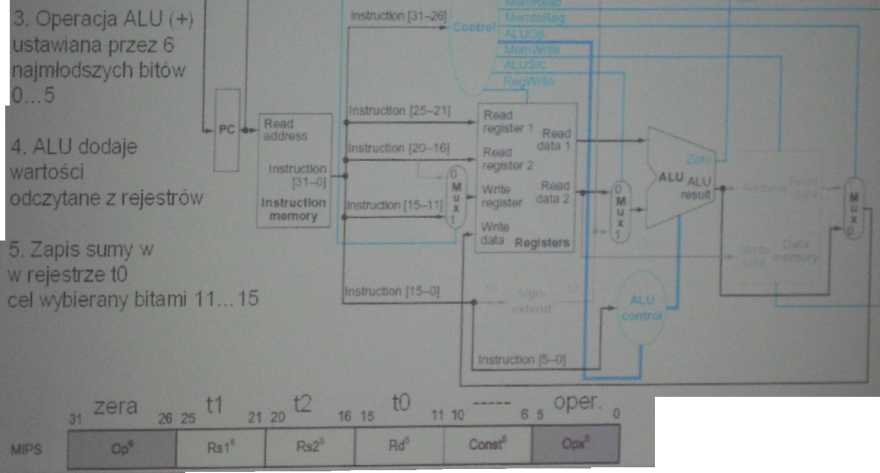

Architektura MIPS - operacja na rejestrach add $t0. $t1. $t2 t0=t1 +t2

1. Pobranie instrukcji z pamięci i POPC+4

2. Odczyt rejestrów t1it2

Wyszukiwarka

Podobne podstrony:

DSCN5254 (5) Architektura MIPS - operacja na rejestrach add $t0. St1. St2 t0=t1 +t2

DSCN5253 (3) Architektura MIPS - Ładowanie z pamięci do rejestru Iw $t0. offset($t2)

DSCN5252 (3) Architektura MIPS ładowanie z pamięci do rejestru Iw StO. offset! $t2)

64 mostka wykonawcza Operacje na rejestrze A (r = c2 Aq7 Ap At -> 4-wejściowa bramka AND): M •

27.05.2010 jest zabroniona. W ogóle najlepiej unikać jakichkolwiek operacji na rejestrach segmentowy

DSCN5251 (4) Architektura MIPS & ARMARM ÓS* MIPS 1 Op" Rsf

DSCN5257 (3) Architektura MIPS - skok bezwarunkowy l. Pobranie instrukcji z pamięci i PC=PC+4 inswua

DSCN5256 (5) w słowach 32b) Architektura MIPS skok warunkowy beq $t0. $t1. adres-przesuniecie ««* MI

Architektura procesora (2) ALU- lista operacji zestaw rejestrów -

Budowa i działanie potoku MIPS R3000 Na końcu każdeg

Pamięć operacyj na (M) Licznik rozkazów (PC) Rejestr rozkazów (IR) Blok sterowania Sygnały

powertools □ ju 16 PowerTools Pomoc Opcje rejestru Operacje na plikach Pliki tymczasowe Obsługa LAN

22 (374) ^^o^ei^c^n^^^oisklej2tra^cj^To^r^e^ews^smi^n^ T0„n,e >Vlk° architektura skarbnica wartoś

DSCN5247 (4) Stos i wywoływanie funkcji w arch. RISC - MIPSW oryginalnej architekturze MIPS brak ins

więcej podobnych podstron