DSCN5257 (3)

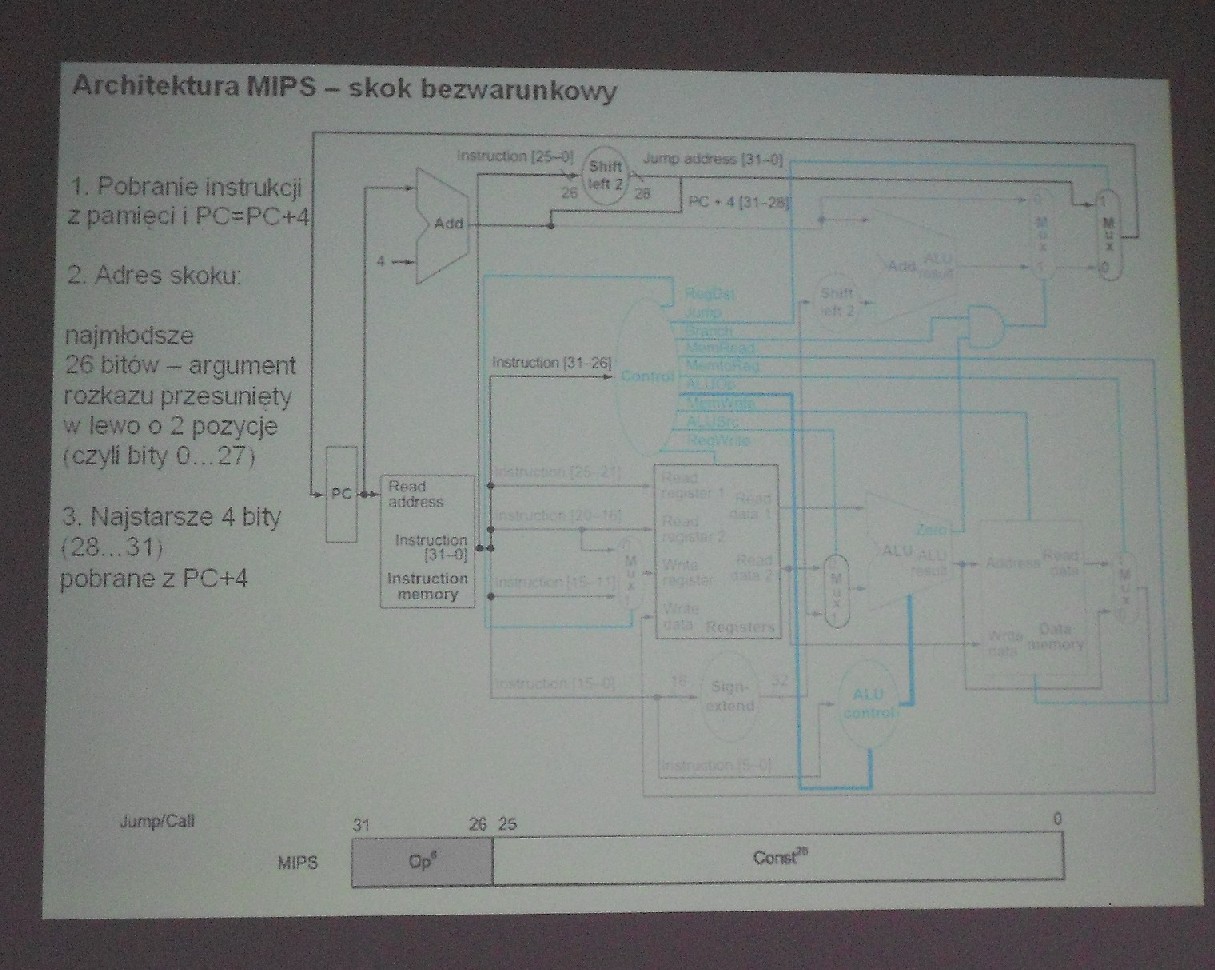

Architektura MIPS - skok bezwarunkowy

l. Pobranie instrukcji z pamięci i PC=PC+4

inswualon |2$-0j

—H XI X ' **12,

)A<ldM— .1

2. Adres skoku:

najmłodsze 26 bitów - argument rozkazu przesunięty w lewo o 2 pozycje (czyli bity 0...27)

3. Najstarsze 4 bity (28... 31) pobrane z PC+4

Resd

address

irtStruclion|3i 26]

Instroction (31-0] j*

Insiruction j mc mory ; •

Jump/Cai

31 26 25

MIPS

Jurnp address t3ł-0j p-

Wyszukiwarka

Podobne podstrony:

DSCN5252 (3) Architektura MIPS ładowanie z pamięci do rejestru Iw StO. offset! $t2)

DSCN5253 (3) Architektura MIPS - Ładowanie z pamięci do rejestru Iw $t0. offset($t2)

DSCN5255 (3) Architektura MIPS - operacja na rejestrach add $t0. $t1. $t2 t0=t1 +t2 1. &

DSCN5256 (5) w słowach 32b) Architektura MIPS skok warunkowy beq $t0. $t1. adres-przesuniecie ««* MI

DSCN5251 (4) Architektura MIPS & ARMARM ÓS* MIPS 1 Op" Rsf

DSCN5254 (5) Architektura MIPS - operacja na rejestrach add $t0. St1. St2 t0=t1 +t2

DSCN5247 (4) Stos i wywoływanie funkcji w arch. RISC - MIPSW oryginalnej architekturze MIPS brak ins

DSCN5250 (4) Fazy cyklu rozkazowego procesora IIF - instruction fetch - pobranie rozkazu z pamięci (

25360 p1030067 (2) Przekazywanie sterowania Adres pamięci Operacja Skok bezwarunkowy 200 201 202 203

Image605 rania instrukcji z pamięci i wykonania, w połączeniu z szybkim przeniesieniem, redukują cza

Architektura Systemów Komputerowych • ••• •Bezpośredni dostęp do pamięci •Realizacja

REALIZACJA ROZKAZÓW SI) FETCH 3T (pobranie rozkazu z pamięci programu)(PC, MEM, MAGISTRALA).. S2) DE

ARCHITEKTURA I URBANISTYKA GDAŃSKEGZAMINY DO POBRANIA

DSCN5298 (3) Branch mtspredct penalty=13 cydes Instruction fetch,— LAGU nP0OTL{l2-«n&y 1 tib n 1

Wygląd wielkość naturalna na monitorze 17" (1024x768)Obudowa PamięćUżycieRok PC, XT,

więcej podobnych podstron