DSCN5322 (2)

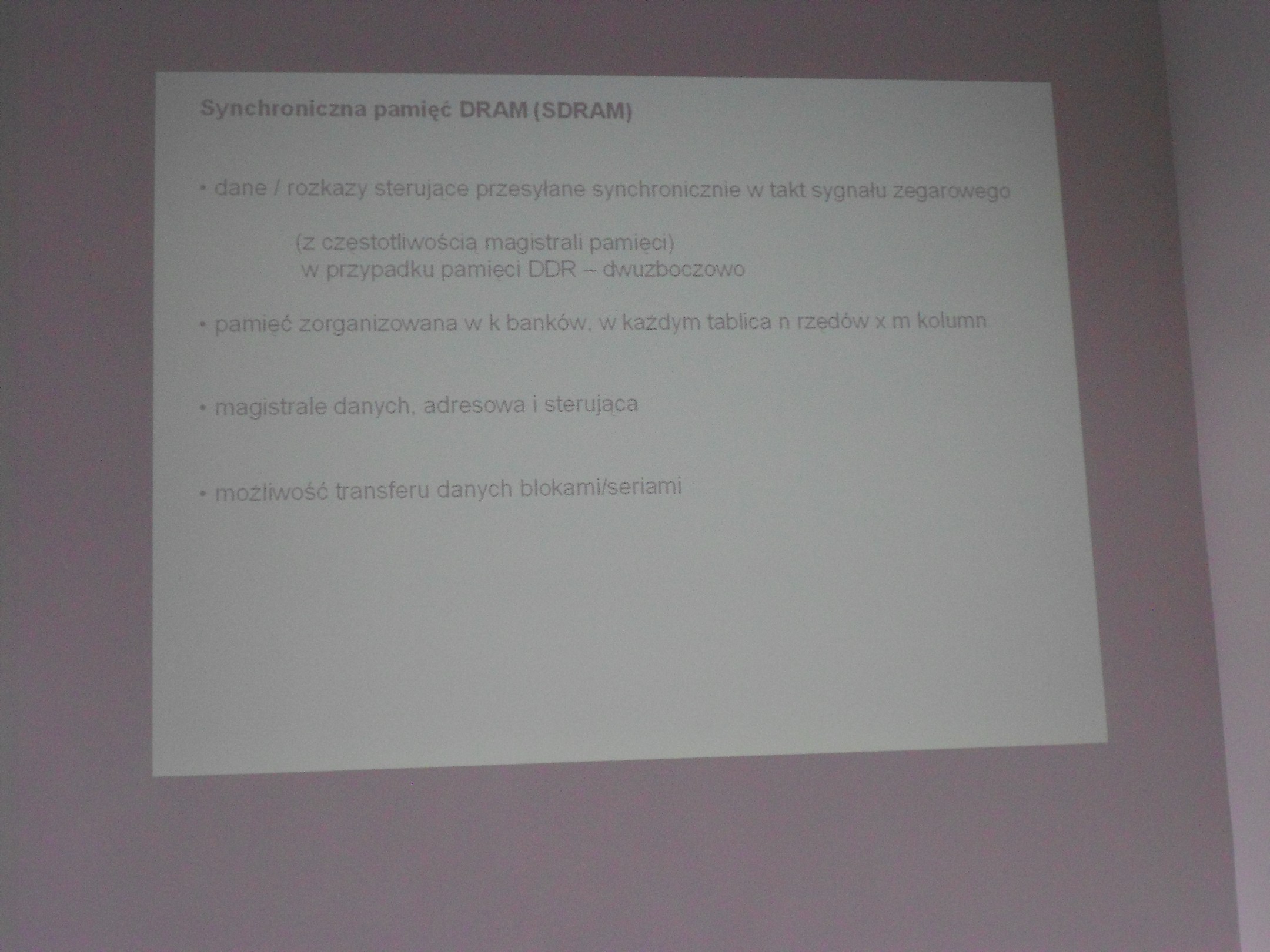

Synchroniczna pamięć DRAM (SDRAM)

* dane / rozkazy sterujące przesyłane synchronicznie w takt sygnału zegarowego

(z częstotliwością magistrali pamięci) w przypadku pamięci DDR - dwuzboczowo

* pamięć zorganizowana w k banków, w każdym tablica n rzędów x m kolumn •

* magistrale danych, adresowa i sterująca * możliwość transferu danych blokami/seriami

Wyszukiwarka

Podobne podstrony:

DSCN5323 (2) Synchroniczna pamięć DRAM (SDRAM) • dane / rozkazy sterujące przesyła

DSCN5325 (2) Synchroniczna pamięć DRAM (SDRAM) Podstawcie cykle pracy transfer danych

DSCN5327 (2) Synchroniczna pamięć DRAM (SDRAM) Podstawowe cykle pracy:

DSCN5328 (2) Synchroniczna pamięć DRAM (SDRAM)* praca w trybie potokowym / z przeplotem (pipelined /

I. Pamięć RAMBudowa matrycy pamięci DRAM -CE -WE -RAS -CAS Q) T3 Dane <

p1030014 Architektura von Neumanna • Dane i rozkazy są przechowywane w tej samej&n

p1030014 Architektura von Neumanna • Dane i rozkazy są przechowywane w tej samej&n

DSCN5321 (2) Dynamiczna pamięć RAM (DRAM) * elementarna komórka (1 bit) zbudowana z tranzystora i ko

Slajd13 (119) Znaczniki rozkazów sterujących T (Trap) - jest znacznikiem pracy krokowej procesora, g

Slajd33 (107) Rozkazy sterujące procesorem Sterowanie znacznikami 1. STC - ustaw z

I. Pamięć RAMOdświeżanie pamięci DRAM Definicja: Czas, jaki upływa od momentu podania prawidłowego

odczytDRAM rys. 3.3. Cykl odczytu pamięci DRAM

PORÓWNANIE SZYBKOŚCI TRANSMISJI?NYCH?R SDRAM I RDRAM Moduł pamięci DDR-SDRAM 64-bitowa (8-bajtowa) s

więcej podobnych podstron