DSCN5328 (2)

Synchroniczna pamięć DRAM (SDRAM)

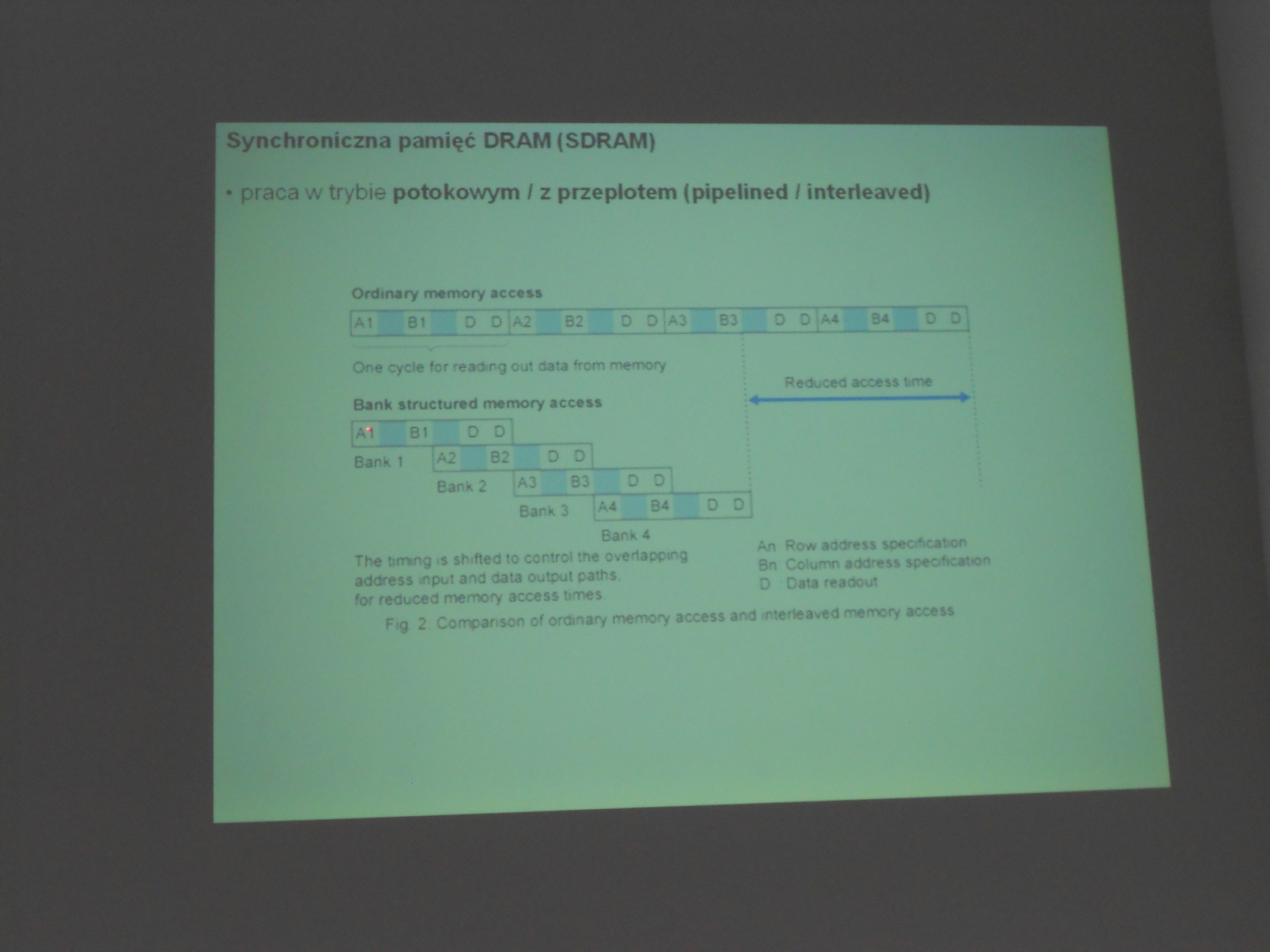

* praca w trybie potokowym / z przeplotem (pipelined / interleaved)

Ord mar/ memory icctu

lAlfcBl ”0 o|A2l|B2™ D 0|a31|b3^| 0 OlAal^BaW 0 0]

One cycie for readmg out data from memory

Reduced access time

Bank ttructured memory access O 1 1 ■■ 0 •

Ullt B1- D Dl

Bank 1 |A2 62 ^| D O

Bank 2 |A3 ^

Bank 3 |A4 B4

Bank 4

The timing «s shifted to contro* tfte overtappng

address «put and data output paths. 8n ***"" waftcaoon

for raduced memory access tirnes

Fig 2 Companson of ortknary memory access and interleaved memory access

Wyszukiwarka

Podobne podstrony:

DSCN5322 (2) Synchroniczna pamięć DRAM (SDRAM) * dane / rozkazy sterujące przesyła

DSCN5323 (2) Synchroniczna pamięć DRAM (SDRAM) • dane / rozkazy sterujące przesyła

DSCN5325 (2) Synchroniczna pamięć DRAM (SDRAM) Podstawcie cykle pracy transfer danych

DSCN5327 (2) Synchroniczna pamięć DRAM (SDRAM) Podstawowe cykle pracy:

rys 3 10a Rysunek 3.10a. Praca pamięci DRAM w trybie stronicowania

DSCN5321 (2) Dynamiczna pamięć RAM (DRAM) * elementarna komórka (1 bit) zbudowana z tranzystora i ko

zx instrukcja47 Włączenie blokady kodowanej * Praca w trybie warsztatowym (ciąg dalszy). W momencie

page0075 67Scaliger — Scarlatti zytności, które zbadał przy pomocy wybornej pamięci i prawie własną

SILNIKI 4 2 suwowe PRACA W TRYBIE CZTEROSUWOWYM SILNIK O NAZWIE 2/4SIGHT może pracować w normalnym t

skanowanie0021 2 DAIKIN - VRVIII Inwerter w wersji „tylko chłodzenie”: • praca w t

I. Pamięć RAMBudowa matrycy pamięci DRAM -CE -WE -RAS -CAS Q) T3 Dane <

I. Pamięć RAMOdświeżanie pamięci DRAM Definicja: Czas, jaki upływa od momentu podania prawidłowego

IV - Wprowadzenie do Systemów Operacyjnych UNIX i LINUX Praca w trybie tekstowym, preferowana przez

11 (250) 4. Zegar ( synchronizacja ) 5. Pamięć 6. &n

odczytDRAM rys. 3.3. Cykl odczytu pamięci DRAM

przydzielone im odrębne ciągi pseudoprzypadkowe. Praca w trybie TDD pozwala na bardziej efektywne

PORÓWNANIE SZYBKOŚCI TRANSMISJI?NYCH?R SDRAM I RDRAM Moduł pamięci DDR-SDRAM 64-bitowa (8-bajtowa) s

tab 2 16 Tabela 2.16. Operacje pamięci DDR SDRAM (dzięki uprzejmości firmy Crucial Technology,a divi

045 m Włączenie blokady kodowanej * Praca w trybie warsztatowym (ciąg dalszy). W momencie przekazani

więcej podobnych podstron