OdczytSRAM

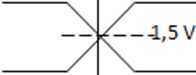

rys. 1.1. Cykl odczytu (asynchroniczny SRAM)

CE = L WE = H

tRC

Adres

Dane

wyjściowe

Dane ustalone

Wyszukiwarka

Podobne podstrony:

odczytDRAM rys. 3.3. Cykl odczytu pamięci DRAM

bb047c72f81301ccf5f0341189083be2 media 720x540 Politechnika WrocławskaCykl odczytu ROM / SRAM © Au

I. Pamięć RAMBudowa matrycy pamięci DRAM -CE -WE -RAS -CAS Q) T3 Dane <

Przykład: Rys.l. Cykl redukcji ryzyka zawodowego [1] albo: Rys.l. Cykl redukcji ryzyka zawodowego lu

- 75 - 1 2 3 1 W o 0 1 Zapis do PO Odczyt z PO 2 STACK 1 Na szynie adresowej adres

293 (33) - 293Praca nieliniowa dynamiczna Rys. 5.46 Proces przełączania tranzystora w układzie WE: a

Rys. 2. Cykl programowy sterownika PLC Wykonanie programu Komunikacja, ignostyka Język drabinkowy L

Rys. 10.28. Asynchroniczny licznik dwójkowy CLK (ans. clock) — zegar RCO (ang. rlpple carry output)

więcej podobnych podstron