4917953759

ii

IEEE Solid-State Circuits Society Poland Chapter

together with Department of Measurement and Electronics

invites for

ADVANCED SHORT COURSE

|

' | |

|

1 |

AGH

The past several years has seen proliferation of all-digital phase-locked loops (ADPLL) for RF and high-performance frequency synthesis due to their elear benefits of flexibility, reconfigurability, transfer function precision, settling speed, frequency modulation capability, and amenability to integration with digital basebanc and application processors. When implemented in nanoscale CMOS, the ADPLL also exhibits advantages of better performance, lower power consumption, lower area and cost over the traditional analog-intensive charge-pump PLL. In a typical ADPLL, a traditional VCO got directly replaced by a digitally controlled oscillator (DCO) for generating an output variable clock, a traditional phase/frequency detector and a charge pump got replaced by a time-to-digital converter (TDC) for detecting phase departures of the variable clock versus the frequency reference (FREF) clock, and an analog loop RC filter got replaced with a digital loop filter. The conversion gains of the DCO and TDC circuits are readily estimated and compensated using ”free" but powerful digital logie.

Day 1: All-Digital Phase-Locked Loop (ADPLL)

This lecture presents a system level view of the ADPLL.

1. Principles of phase-domain frequency synthesis

2. ADPLL dosed-loop behavior

3. Direct frequency modulation of ADPLL

4. Alternative TX architectures using ADPLL and PA regulator

5. Survey of published ADPLL architectures; TDC-less ADPLL; cell-based ADPLL design

Digitally-controlled oscillator (DCO)

A digitally controlled oscillator (DCO) lies at the heart of an all-digital phase-locked loop (ADPLL). It is based on an LC-tank with a negative resistance to perpetuate the oscillation—just like the traditional VCO, but with a significant difference in one of the components: instead of continuously tuned varactor (variable capacitor). the DCO now uses a large number of binary-controlled varactors. Each varactor can be placed in either high or Iow capacitative State. The composite varactor performs digital-to-capacitance conversion. This lecture presents a circuiLand system level views of DCO. v /

Lecture 1:

8:00 - 9:30 Lecture 2: 10:00-11:30 Lecture 3:

12:00-13:30

Day 2:

Lecture 1:

8:00 - 9:30 Lecture 2: 10:00-11:30

Day 2: Time-fo-digital converter (TpC)

Lecture 3:

12:00-13:30

A time-to-digitalvconverter (TDC) is used in the ADPLL to perform the phase detection. It generates a digital variable phase or timestamps of tnbsFREF edges in the units of the DCO c|dck period. The variable phase is a fixed-point digital word in which the fractional parLiś measured with a resolujion of an inverter delay (about 10 ps in 40-nm CMOS). This lecture presents a system level view of TDC asVell as its circuit-level implementation^sues. sohe^stato circuits sodoty

Are welcome

REE OF CHARGE

Biography of the invited speaker

Robert Bogdan Staszewski

Fuli Prcfcssor, IEEE Fcllow -Sfihool of Efectrical & Electronic Engineenng Universlty College Dublin, Ireland

..■> 1

f/

,.Ieted Technikum Elektryczne in Białystok. He rcccivod his B.Sc. >. degrees, in Electrical Engineering, from the University of Texas at

HH__. W— >1. 1992 and 2002, respectwely. From 1991 to 1995, he was with Alcatel

Tfctwork Systems In Rtchardson, Tcxos. USA, worWng on SONET crossconnect Systems for flbcr optics WfłmuhjsiotHirię. Me joined Texas Instruments, Dallas, TX, USA, In 1995 where he was ekreted -Oetmguishcd Membcr of Technieal Staff (limited to 2% of tcchnical Łtaff). Between 1995 and 1999, he was -ngaged in advanced CMOS read channel development for hard disk drives. In 1999, he co-started a Digital RF Processor (DRP) group withln Texas Instruments with a misston to lnvent new digitally mcensive approaches to traditional RF functions for integrated radios m dccpiy-scalcd CMOS processes. He was appointed o CTO of the DRP groop between 2007 and 2009. In July 2009, he jomed Delft university of Technology, Delft, ’he Netherlands, where lie is cuhently a part-tlme Fuli Professor. Since Sept. 2014, he has been a Professcr with University College Dublin (UCD), Dublin, Ireland. He has authored and co-authored three books, five book chapters, 2lO]ournaland conference pubiicatlons, and holds 160issued US patents. He Isan IEEE Feilow and a rccipicnt of IEEE Circuits and Systems Industrial Pioneer Award.

Robert Bogdan

cum laude), M

——

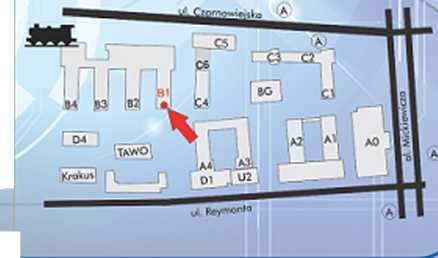

Meeting venue

AGH University of Science and Technology Av. Mickiewicza 30, Kraków, Poland Building B-l, 121 lecture hall, 2nd floor

Wyszukiwarka

Podobne podstrony:

IEEE Solid-State Circuits Society Poland Chapter together with Department of Measurement and

IEEE Solid-State Circuits Society Poland Chapter together with Department of Measurement and

r❖i ^ UJ AGH IEEE Solid-State Circuits Society Poland Chapter invites for Lectu re by Prof. Edoardo

1 ”1 1/J IEEE Solid-State Circuits Society Poland Chapter invites for AGHLecture / Keynote talkby

A♦IEEEInvited Lectures by Prof. Willy Sansen organized by the IEEE Solid-State Circuits Society Pola

Uf AGH IEEE Solid-State Circuits Society Chapter Poland together with Department of

DL Willy Sansen Yisits SSCS Poland Chapter The IEEE Solid-State Circuits Soci-ety (SSCS) Poland Chap

An introduction to the graph theory A graph is a set of points, together with a set of arcs that con

Summary These equations, together with the definitions 4.15 and 4.20, are regarded as the basie laws

essent?rving?53 CHAPTER 4CARVEDMOULDINGS The carving of architectural and frame mouldings, while res

gonsoi.es Collins IC Console Series The Collins IC-10 and IC-6 all solid State consoles offer the br

Moseley PCL-303 Transmitter The all solid State PCL-303 STL Transmitter uses the direct FM system. F

Creative Doughcraft�3 © CHAPTER 1 • TOOLS AND MATERIALSBasic equipment It is worth gotting together

P5280928 (2) Alina Grochowska Problcins of Bibliographic Standardization In Poland AB8TRACT Together

CFA Society Poland JAKIE SĄ POTRZEBY I ZWYCZAJE INWESTYCYJNE MILLENIALSÓW? ■

-. 1996. The State Against Society. Political Crises and their Aftermath in East Central Europę, Pri

Snhmitted: 2014-12-12 Reeised: 2015-04-22 Accepted: 2015-04-22 Online: 2015-08-28 Solid State

Solid State Phenomena Submitted2016-02-19 Accepted: 2016-02-03 Online: 2016-07-20 ISSN: 1662-97

4IEEE { lilii V.V AGHInvited Lectures by Prof. Bogdan Staszewski organized by the IEEE Solid-State

więcej podobnych podstron