32175

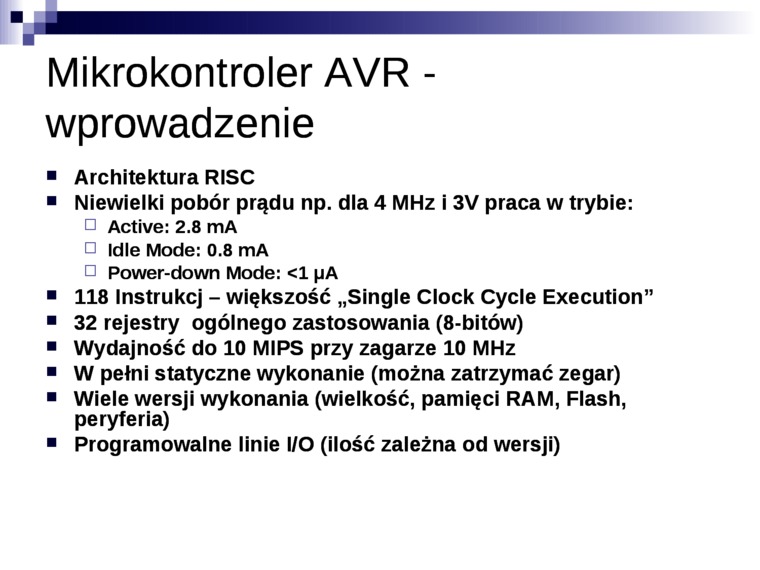

Mikrokontroler AVR -wprowadzenie

■ Architektura RISC

■ Niewielki pobór prądu np. dla 4 MHz i 3V praca w trybie:

□ Active: 2.8 mA

□ Idle Modę: 0.8 mA

□ Power-down Modę: <1 pA

■ 118 Instrukcj - większość „Single Clock Cycle Execution”

■ 32 rejestry ogólnego zastosowania (8-bitów)

■ Wydajność do 10 MIPS przy zagarze 10 MHz

■ W pełni statyczne wykonanie (można zatrzymać zegar)

■ Wiele wersji wykonania (wielkość, pamięci RAM, Flash, peryferia)

■ Programowalne linie l/O (ilość zależna od wersji)

Wyszukiwarka

Podobne podstrony:

62 (96) Mikrokontrolery Atmcl, wprowadzając na rynek w pierwszej połowie lat 90. mikrokontrolery AVR

skanuj0064 (30) Uczenie się wspomagane mikrokomputeremRyszard Dobrowolski Wprowadzenie Pisząc współc

Architektura procesora RISC Cechy architektury RISC (Reduced Instruction Set Computer): *

Kościół�2 WPROWADZENIE Architektura współczesnych kościołów katolickich zachowuje podobieństwa i odm

e9bd0b0843caabd9f60f6d79d518183f Przyjmij i zatrudnij kota... w roli programisty mikrokontrolerów AV

IMGf06 Budowa i działanie mikrokontrolerów AVR zliczania. Na skutek przepełnienia Timera/LicznikaO m

63 (92) MikrokontroleryKamPROG AVR + AVR Studio/ KamPROG AVR + Bascom Fot. 7. Programator KamPROG AV

Architektura procesora RISC Cechy architektury RISC (Reduced Instruction Set Computer): ■k Zredukowa

41.Wyniicń rodziny mikrokontrolerów AVR i podaj i główne cechy. Procesory AVR dzielą się na dwie rod

78249 IMGf10 (3) 66 Budowa i działanie mikrokontrolerów AVr Tab. 5.3. Konfiguracja modulatora

Mikrokontrolery AVR w praktyce (J Doliński) Jarosław Doliński projektowych dla AVR. w tym AVR-GCC i

bascom Programowanie mikrokontrolerów AVR w języku

więcej podobnych podstron