Funkcjê emulatora pe³ni

niezale¿ny uk³ad

sterowany w³asnym

mikrokontrolerem; do

wprowadzania

i wizualizacji danych

u¿yto komputera,

wykorzystano dane

systemowe czas, datê,

dzieñ tygodnia oraz czas

letni lub zimowy,

a pozosyta³e informacje

mo¿na wprowadzaæ

z klawiatury; ich aktualny

stan jest przedstawiany

na ekranie monitora.

C

oraz czêciej w uk³adach wyko-

rzystuj¹cych mikrokontrolery jest

potrzebna informacja o aktual-

nym czasie. Istnieje kilka spo-

sobów odmierzania bie¿¹cego czasu. Mo¿-

na u¿yæ do tego celu specjalizowanych uk³a-

dów zwanych zegarami czasu rzeczywiste-

go (RTC), zasilanych z w³asnej baterii. Do-

k³adnoæ odmierzania czasu zale¿y od jako-

ci rezonatora kwarcowego. Dlatego u¿yt-

kownik musi okresowo kontrolowaæ wskazy-

wany czas, szczególnie w chwilach zmian

miêdzy czasem letnim i zimowym. Innym

rozwi¹zaniem jest wykorzystanie czasu

transmitowanego przez systemy GPS lub

DCF 77. Zalet¹ zegara DCF 77 jest prosty,

³atwy do wykonania i tani odbiornik. Nadawa-

ny czas jest czasem rodkowo-europejskim

z uwzglêdnieniem czasu letniego i zimowe-

go co zwalnia u¿ytkownika z jakiejkolwiek

obs³ugi podczas eksploatacji.

Zegar DCF 77

Nadajnik DCF 77 jest zlokalizowany w Ma-

inflingen (50:01N, 09:00E), oko³o 25 km na

po³udniowy wschód od Frankfurtu nad Me-

nem. Czêstotliwoæ nona fali emitowanej

przez nadajnik wynosi 77,5 kHz, a jej moc

50 kW. Antena ma charakterystykê doo-

kóln¹ i wysokoæ 150 m (antena zapasowa

ma wysokoæ 200 m). Fala nona jest mo-

dulowana amplitudowo. Co sekundê (z wy-

j¹tkiem 59. sekundy ka¿dej minuty) ampli-

tuda fali nonej jest redukowana do pozio-

mu 25% wartoci maksymalnej na 0,1 albo

EMULATOR ZEGARA DCF 77

(1)

Radioelektronik Audio-HiFi-Video 10/2002

0,2 s zale¿nie od stanu aktualnie transmi-

towanego bitu. Bit 0 jest kodowany za po-

moc¹ impulsu krótkiego 100 ms, bit o war-

toci logicznej 1 za pomoc¹ d³ugiego im-

pulsu 200 ms.

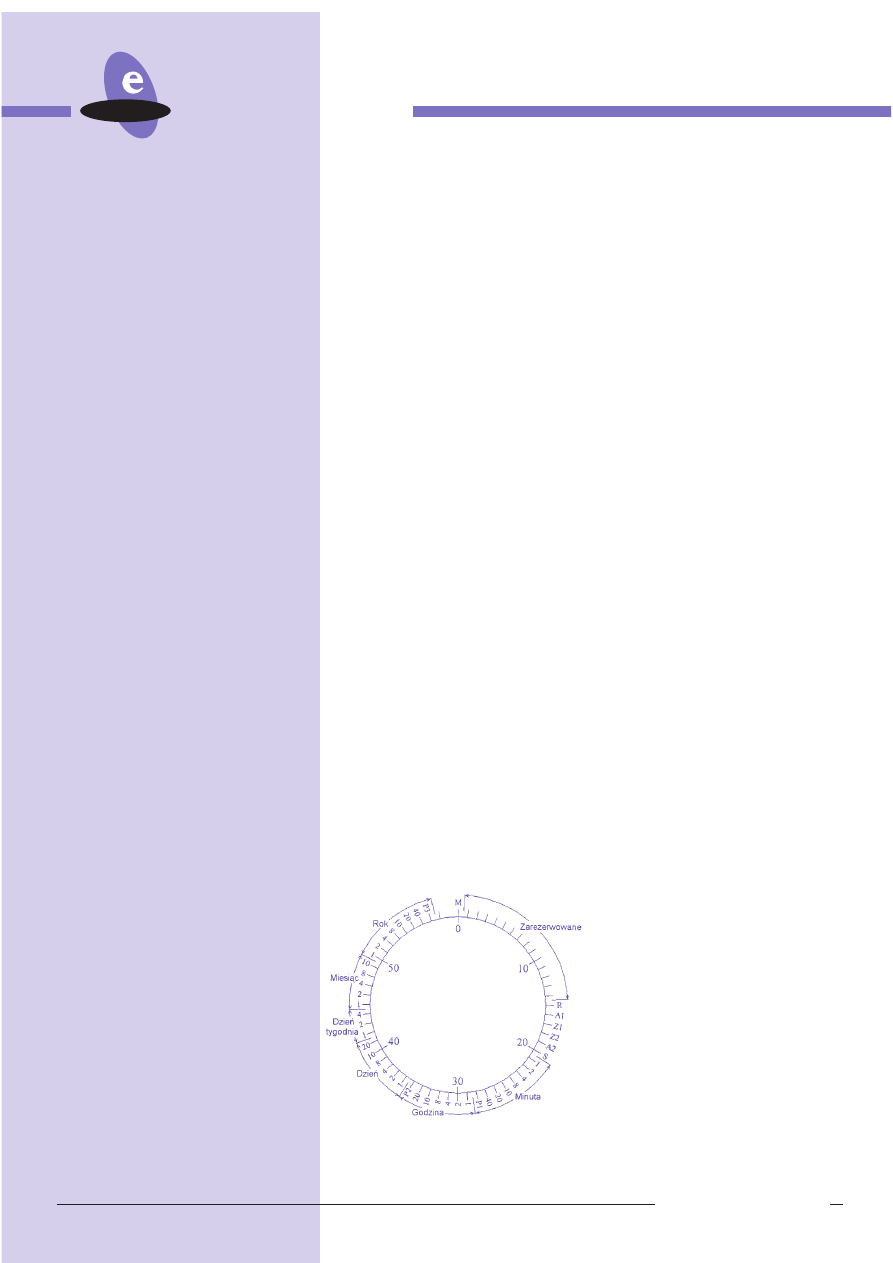

Na rys. 1 przedstawiono sposób kodowania

danych transmitowanych przez nadajnik

DCF 77. Kolejne pola struktury zawieraj¹

nastêpuj¹ce dane:

M

Pocz¹tek minuty; zawsze = 0,

1-14 Przerwa, bez znaczenia _ wszystkie zera,

R

0 _ antena normalna; 1 _ antena pomocnicza,

A1 0 normalnie, 1 _ zapowied zmiany czasu

z godzinnym wyprzedzeniem,

Z2-Z1 10 _ czas zimowy, 01 _ czas letni,

A2 0 normalnie, 1 _ zapowied dodatkowej

sekundy,

S

Start danych. Zawsze = 1,

24-21 Jednoci minut w kodzie BCD (24 MSB,

21 LSB),

27-25 Dziesi¹tki minut w BCD,

28 Bit parzystoci dla bitów minut (21 _ 27),

32-29 Jednoci godzin w BCD,

34-33 Dziesi¹tki godzin w BCD,

35 Bit parzystoci dla bitów godzin (29-34),

39-36 Jednoci dni miesi¹ca w BCD,

41-40 Dziesi¹tki dni miesi¹ca w BCD,

44-42 Dni tygodnia w BCD (1 poniedzia³ek, itd.),

48-45 Jednoci miesi¹ca w BCD,

49 Dziesi¹tki miesi¹ca w BCD,

53-50 Jednoci lat w BCD,

57-54 Dziesi¹tki lat w BCD,

58 Bit parzystoci dla bitów 36 57,

59 Brak impulsu synchronizacja odbiornika.

Zasiêg nadajnika DCF jest bardzo rozle-

g³y, pokrywa znaczn¹ czêæ Europy, obej-

muj¹c miêdzy innymi obszar ca³ej Polski.

Wskutek na³o¿enia siê fali powierzchnio-

wej i pojawiaj¹cej siê w pewnych porach do-

by fali jonosferycznej mo¿e wyst¹piæ w pew-

nych rejonach chwilowe os³abienie lub na-

wet ca³kowity zanik sygna³u. Niekorzystny

wp³yw na pracê odbiornika mog¹ mieæ inne

urz¹dzenia wytwarzaj¹ce zak³ócenia elek-

tromagnetyczne. Opisane zjawiska mog¹

utrudniaæ testowanie oprogramowania syste-

mu mikroprocesorowego korzystaj¹cego

z odbiornika danych zegara DCF. Ponadto

pewne dane s¹ nadawane bardzo rzadko,

st¹d na przyk³ad testowanie oprogramowa-

nia podczas zmian czasu letnizimowy mo¿-

na by przeprowadzaæ tylko dwa razy do ro-

ku, w doæ niekorzystnej porze doby. Dlate-

go do testów lepiej u¿yæ emulatora, który za-

pewni stabilny sygna³ i umo¿liwi dowolnie

modyfikowaæ transmitowane dane.

Emulacja zegara DCF 77

Funkcjê emulatora mo¿e pe³niæ niezale¿ny

uk³ad sterowany w³asnym mikrokontrole-

rem. Do wprowadzania i wizualizacji da-

nych jest potrzebna klawiatura oraz wy-

wietlacz znakowy. To zwiêksza koszt urz¹-

dzenia, a wprowadzanie po ka¿dym w³¹cze-

niu emulatora kompletu danych za pomoc¹

klawiatury wymaga du¿ego samozaparcia

i benedyktyñskiej cierpliwoci. Dobrym po-

mys³em wydaje siê u¿ycie do tego celu

komputera. Mo¿na wykorzystaæ dane syste-

mowe _ czas, datê, dzieñ tygodnia oraz

czas letni lub zimowy. To zwalnia u¿ytkow-

nika od wprowadzania znacz¹cej czêci

danych. Pozosta³e informacje mo¿na ³atwo

wprowadzaæ z klawiatury, a ich aktualny

stan przedstawiaæ na ekranie monitora.

Ci¹g informacji symuluj¹cych zegar DCF

mo¿e byæ generowany na przyk³ad na jed-

nej z linii portu równoleg³ego. Niestety, na

tym koñcz¹ siê zalety tego rozwi¹zania.

Do generowania danych s¹ potrzebne infor-

macje o odcinkach czasu trwaj¹cych 100

ms. Tymczasem w komputerach czas syste-

mowy jest uaktualniany w doæ archaiczny

sposób. Wykorzystuje siê do tego celu prze-

rwania generowane z czêstotliwoci¹ nieco

wiêksz¹ ni¿ 18 Hz. Ka¿de przerwanie in-

krementuje zmienn¹ systemow¹, która dzie-

lona przez odpowiednie sta³e daje aktualn¹

liczbê sekund, minut, godzin, dni i tak dalej.

Poniewa¿ liczba przerwañ generowanych

w ci¹gu jednej sekundy nie jest liczb¹ ca³-

kowit¹, wygenerowanie odcinków czasu

trwaj¹cych 100 i 200 ms nie wydaje siê

mo¿liwe. Odcinki o czasie trwania 1 s bê-

d¹ obarczone b³êdem dochodz¹cym do ±

55 ms. W celu dok³adniejszego wyznacza-

nia wspomnianych odcinków czasu mo¿-

na u¿yæ kalibrowanych pêtli programowych.

W tym przypadku, na pocz¹tku programu

Rys. 1. Struktura danych nadawanych przez

zegar DCF 77

21

nale¿y umieciæ procedurê, która wyzna-

czy liczbê inkrementacji zmiennej steruj¹cej

pêtli miêdzy dwoma kolejnymi przerwania-

mi zg³aszanymi przez uk³ad czasowy. Na tej

podstawie mo¿na obliczyæ liczbê inkremen-

tacji zmiennej steruj¹cej pêtli koniecznych do

wygenerowania potrzebnych odcinków cza-

su, czyli dostosowaæ program do szybkoci

danego komputera. To powoduje znaczn¹

rozbudowê programu i nie zawsze daje

oczekiwane rezultaty. Dlatego najlepszym

rozwi¹zaniem jest do³¹czenie prostego uk³a-

du generuj¹cego impulsy synchronizuj¹ce

poza komputerem i doprowadzenie ich do

niego na przyk³ad przez linie wejciowe po-

rtu równoleg³ego.

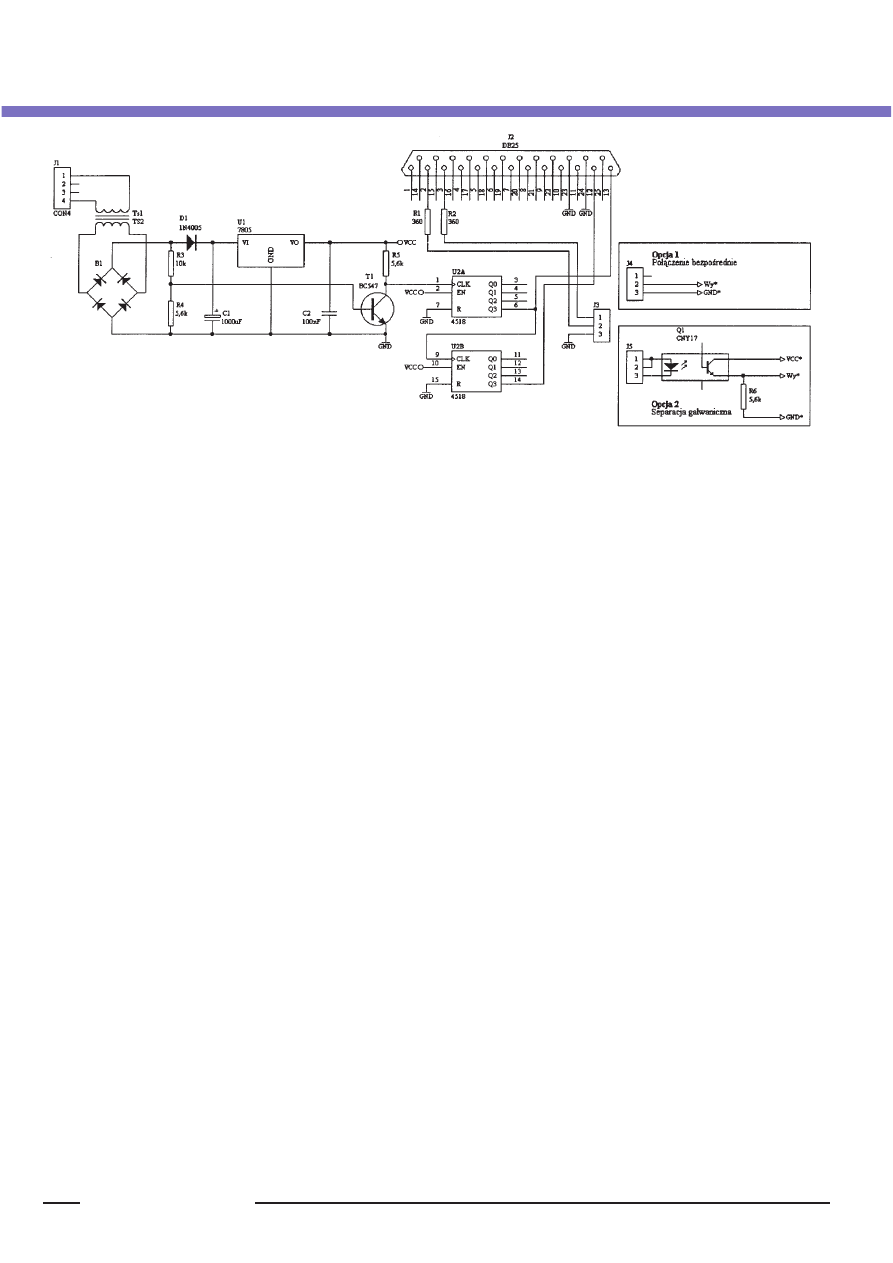

Konstrukcja emulatora

Na rys. 2 jest przedstawiony schemat emu-

latora. Sk³ada siê z zasilacza (B1, C1, U1)

z transformatorem sieciowym Ts1, uk³adu

synchronizacji (T1, D1, R3, R4, R5), dwóch

dzielników (U2A, U2B) oraz uk³adu wyjcio-

wego z mo¿liwoci¹ separacji galwanicznej

miêdzy komputerem a testowanym odbior-

nikiem danych DCF.

W uk³adzie mo¿na u¿yæ dowolnego trans-

formatora sieciowego o mocy 2 VA i napiêciu

wtórnym 8

÷

15 V. Transformator musi zapew-

niaæ dobr¹ separacjê galwaniczn¹ miêdzy

uzwojeniami. Najlepsz¹ izolacjê zapewniaj¹

transformatory, w których oba uzwojenia s¹

nawiniête na oddzielnych czêciach korpusu.

Zasilacz sk³ada siê z mostka prostownicze-

go B1, kondensatora filtruj¹cego C1 i stabi-

lizatora U1 o napiêciu +5 V. Miêdzy most-

kiem prostowniczym a kondensatorem filtru-

j¹cym jest umieszczona dioda D1. Dziêki te-

mu na jej anodzie dwa razy w ci¹gu okresu

sieci zasilaj¹cej napiêcie jest równe zero.

W takiej chwili przez bazê tranzystora T1 nie

p³ynie pr¹d. Tranzystor jest wy³¹czony, a na

terach port równoleg³y jest sterowany przez

specjalizowany uk³ad, zintegrowany z p³yt¹

g³ówn¹. To powoduje, ¿e uszkodzenie portu

spowodowane nieostro¿n¹ obs³ug¹ skut-

kuje wymian¹ kosztownej p³yty.

Drugi sposób (Opcja 2) dziêki transoptoro-

rowi Q1 zapewnia separacjê galwaniczn¹

miêdzy emulatorem i odbiornikiem. Nato-

miast emulator w obu przypadkach jest

bezporednio po³¹czony z portem kompu-

tera. Równie¿ w tym przypadku nie nale¿y

zapominaæ o ostro¿noci.

Z powy¿szego opisu wynika, ¿e uk³ad jest

synchronizowany czêstotliwoci¹ sieci ener-

getycznej. Na szczêcie minê³y czasy, kie-

dy czêstotliwoæ sieci ró¿ni³a siê o kilka

herców od wartoci znamionowej. Obecnie

jej sta³oæ jest wystarczaj¹ca do prawid³o-

wej pracy emulatora, który przecie¿ nie ma

zastêpowaæ zegara DCF pod wzglêdem

dok³adnoci odmierzania czasu, a jedynie

umo¿liwiaæ ³atwe modyfikowanie nadawa-

nych informacji. Przyjêcie ma³ej czêstotliwo-

ci synchronizacji zmniejsza liczbê dzielni-

ków. To powoduje, ¿e uk³ad jest prosty, ³a-

twy do wykonania i uruchomienia. Przy ta-

kim rozwi¹zaniu nie ma potrzeby wykony-

wania p³ytki drukowanej. Uk³ad mo¿na

zmontowaæ na p³ytce uniwersalnej, co skró-

ci czas wykonania i dodatkowo obni¿y ko-

szty. Bezb³êdnie zmontowany uk³ad dzia³a

od razu poprawnie i nie wymaga ¿adnych

czynnoci uruchomieniowych.

n

Adam Mazurkiewicz

L I T E R A T U R A

[1] Gajewski P., Turczyñski J.: Cyfrowe uk³ady scalone

CMOS. Warszawa, WK£ 1990

[2] Bielecki J.: Encyklopedia jêzyka C dla IBM PC.

Warszawa, WK£ 1989

jego kolektorze wystêpuje napiêcie +5 V.

Przez pozosta³¹ czêæ okresu napiêcie jest

ró¿ne od zera i tranzystor jest aktywny. To

powoduje, ¿e na kolektorze tranzystora T1

otrzymujemy ci¹g impulsów o czêstotliwoci

100 Hz. Dalej impulsy s¹ doprowadzone

do wejcia uk³adu scalonego U2A (4518).

Sk³ada siê on z dwóch liczników (dzielników)

zliczaj¹cych modulo 10 [1]. Na wyjciu

pierwszego licznika U2A otrzymujemy ci¹g

impulsów o okresie równym 100 ms. S¹

one doprowadzane do wejcia drugiego

licznika U2B i do linii wejciowej (ON/OF) po-

rtu równoleg³ego komputera. Na wyjciu

drugiego licznika otrzymujemy przebieg pro-

stok¹tny o czasie trwania 200 ms i okresie

1 s. Wyjcie drugiego licznika jest po³¹-

czone z kolejn¹ lini¹ wejciow¹ (PAP) portu

równoleg³ego.

Komputer generuje przebieg emuluj¹cy ze-

gar DCF na dwóch liniach wyjciowych (D0

i D1) portu równoleg³ego. Takie rozwi¹zanie

umo¿liwia zwiêkszenie obci¹¿alnoci pr¹-

dowej portu. Emulator mo¿na do³¹czyæ do te-

stowanego odbiornika sygna³u DCF na dwa

sposoby. Pierwszy sposób (Opcja 1) polega

na bezporednim po³¹czeniu emulatora

z odbiornikiem. W tym przypadku podczas

pracy obu urz¹dzeñ nale¿y zachowaæ szcze-

góln¹ ostro¿noæ. Masa komputera jest po-

³¹czona z bolcem uziemiaj¹cym w gniazdku

sieci energetycznej. Potencja³ bolca uzie-

miaj¹cego niemal zawsze ró¿ni siê od poten-

cja³u ziemi. Znacznie wiêksze niebezpie-

czeñstwo wystêpuje wtedy, gdy komputer

jest do³¹czony do gniazda bez bolca uzie-

miaj¹cego. Wówczas pozbawiony uziemie-

nia filtr przeciwzak³óceniowy pracuje jako

dzielnik napiêcia sieciowego, a na masie

komputera wystêpuje napiêcie oko³o 110 V.

Jest to du¿e zagro¿enie nie tylko dla sprzê-

tu, ale przede wszystkim dla obs³uguj¹cych

go osób. W obecnie produkowanych kompu-

Radioelektronik Audio-HiFi-Video 10/2002

Rys. 2. Schemat emulatora zegara DCF 77

Wyszukiwarka

Podobne podstrony:

2002 10 12 pra

eis 2002 10 adaptacja akustyczna domowego studia

ZŁOTE MYŚLI 10-20

2002 10 12 prawdopodobie stwo i statystykaid 21648

Encyklopedia Prawa - wyklad 10 [20.11.2001], INNE KIERUNKI, prawo, ENCYKLOPEDIA PRAWA

2002 10 01

Siatkówka- wystawa 2002.10.22, Konspekty, Siatkówka

Prawo cywilne ćw.1 2010-10-20, Prawo Cywilne

Koszykówka- rzut pozycyjny jednorącz 2002.10.02, Uczelnia

10 (20)

2002 10 03

La-atletyka terenowa 2002.09.20, lekkoatletyka

2002 10 30

RF Wyklad 2010 10 20

sciaga z fizyki, 10-20, Interferencja fal-zjawisko nakładania się dwóch lub więcej fal spójnych,czyl

sciaga z fizyki, 10-20, Interferencja fal-zjawisko nakładania się dwóch lub więcej fal spójnych,czyl

2002 10 07

2002 10 24

więcej podobnych podstron