1.

Zastosowanie pól bitowych języka C w operacjach bitowych, podad przykład.

Pola bitowe to specjalny typ składnika klasy polegający na tym, że informacja jest

przechowywana na określonej liczbie bitów. Długośd pola bitowego określa ilośd bitów wchodzących w

skład pola. Pola bitowe są używane w celu oszczędzania pamięci lub do operacji niskiego poziomu

wymagających zmian pojedynczych bitów. Dostęp do pola bitowego w zakresie pewnego typu

danych/struktur danych jest realizowany za pomocą '.' (kropka) albo '->' - w zależności od kontekstu w

jakich używamy tegoż pola.

Przykład:

#include <stdio.h>

typedef struct {

unsigned char szyberdach : 1;

unsigned char abs : 1;

unsigned char ilosc_miejsc : 4;

} SAMOCHOD;

void main(void)

{

SAMOCHOD ford;

ford.szyberdach = 1;

ford.abs = 1;

ford.ilosc_miejsc = 2;

}

2.

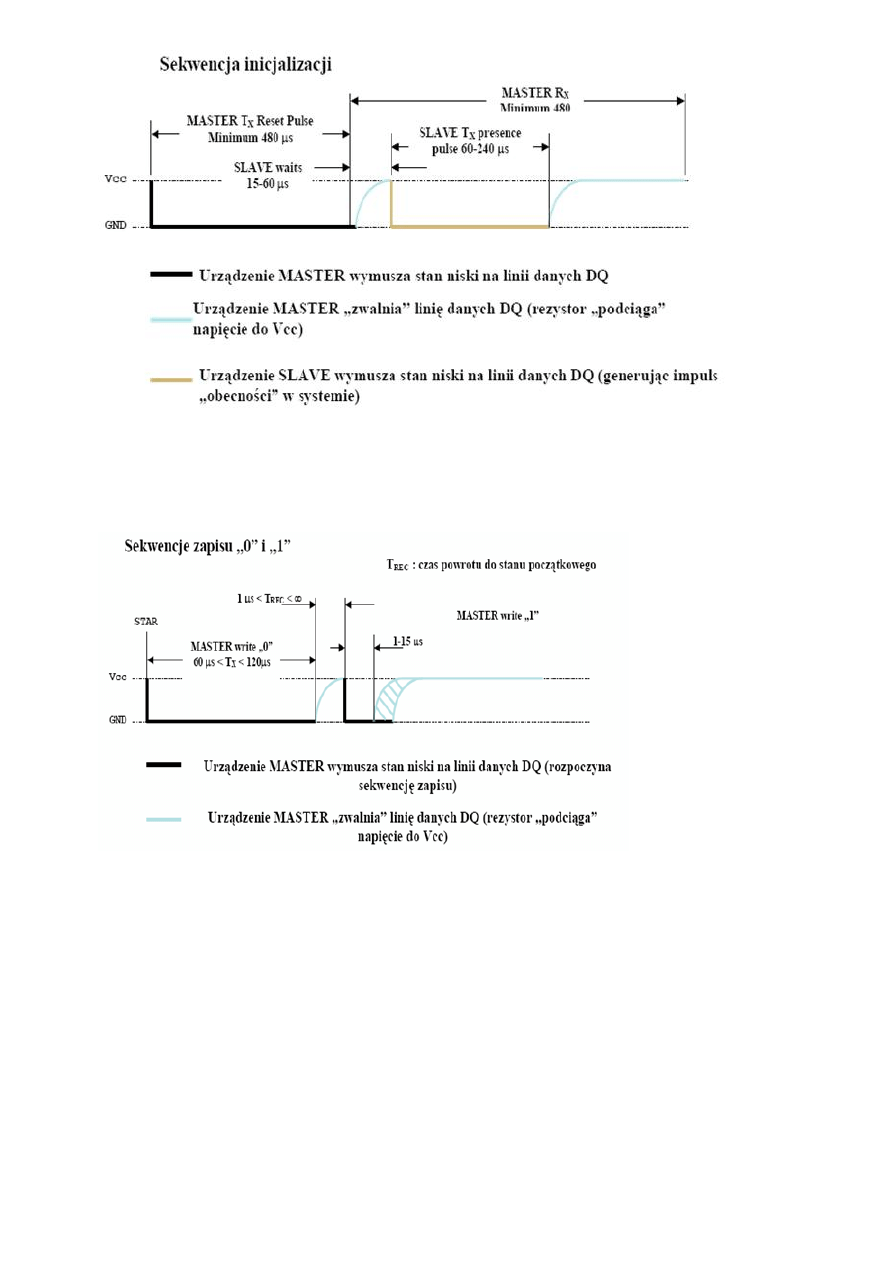

Interfejs 1-Wire. Podad przebiegi czasowe dla sekwencji resetu, zapisu/odczytu, zera/jedynki. Na

każdym z wykresów zamieścid informację o nadawcy (dla każdego z fragmentów przebiegu)

Nazwa interfejsu 1-Wire wywodzi się stąd, że do całkowitej komunikacji używana jest tylko jedna

linia danych (i jedna linia masy). Dodatkowo, odbiornik może byd zasilany bezpośrednio z linii danych,

wykorzystując zasilanie pasożytnicze, co jest ogromną zaletą tego interfejsu.

Właściwości magistrali 1-Wire:

Wykorzystuje jedną linię do dwustronnej komunikacji.

Wymaga rezystora podciągającego na linii danych (ang. pull-up resistor) najczęściej o wartości 4.7–5

kΩ.

System z magistralą 1-Wire wymaga jednego urządzenia typu Master i jednego lub więcej urządzeo

typu Slave.

Każde urządzenie podłączone jest do magistrali przez koocówkę typu „open drain” lub 3-state port.

Wszystkie dane oraz rozkazy przesyłane są przez magistralę począwszy od najmłodszego bitu (ang.

LSB).

Każda wymiana danych zawiera 3 etapy :

1. Inicjalizacja: Zawiera etap zerowania układu Slave oraz etap potwierdzenia przez Slave’a obecności

na magistrali.

2. Przesyłanie komendy typu ROM:. Każdy układ Slave posiada unikalny 64-bitowy kod. Komendy typu

ROM umożliwiają zaadresowanie konkretnego układu, identyfikację układu, wyszukanie alarmu lub

pominięcie sprawdzania 64-bitowego kodu.

3. Przesłanie funkcji sterującej układu:. Sekwencja tego typu umożliwia realizację wszystkich

dostępnych operacji na wybranym układzie.

Urządzenie typu master rozpoczyna transmisję sekwencji bitów poprzez wystawienie impulsu reset,

czyli zwarciu linii danych na 480 μs do masy. Powoduje to zresetowanie wszystkich podłączonych

odbiorników (urządzeo typu slave). Następnie każde urządzenie slave potwierdza swoją obecnośd

wystawiając na linię danych impuls obecności - zwierając linię danych do masy na 60 μs.

Przesłanie logicznej jedynki na magistralę oznacza wystawienie przez mastera krótkiego (od 1 do 15μs)

impulsu niskiego (zwarcie linii) oraz następnie wysokiego o długości 60 μs. Logiczne zero odpowiada

niskiemu impulsowi o długości od 60 do 120μs.

Przed odbiorem każdego bitu danych master wysyła niski impuls startu (od 1 μs do 15 μs), po czym

wraca do stanu wysokiego na linii danych. Jeśli slave chce wysład logiczną jedynką - nie robi nic,

pozostawiając linię w stanie wysokim. Jeśli slave chce wysład zero, wówczas zwiera linię danych do

masy na 60 μs. Po przesłaniu 8 bitów następuje wysłanie komendy (rozkazu) (również ośmiobitowej).

Ewentualne błędy w transmisji mogą byd wykryte za pomocą wbudowanego CRC (również

ośmiobitowego).

Inicjalizacja rozpoczyna się wysłaniem na magistrale przez układ Master impulsu zerującego następnie

układ Slave wysyła impuls obecności. Inicjalizacja pozwala układowi Master wykrycie podłączonych do

niej układów Slave.

Sekwencja zapisu ‘0’ i ‘1’

Nadanie logicznego 0 polega na wygenerowaniu impulsu o czasie trwania 60-120 µs a następnie na

zwolnieniu magistrali i oczekiwaniu minimum 1µs przed nadaniem następnego bita.

Dla logicznej 1 generowany impuls trwa 1-15µs natomiast wymagany czas bezczynności 60µs

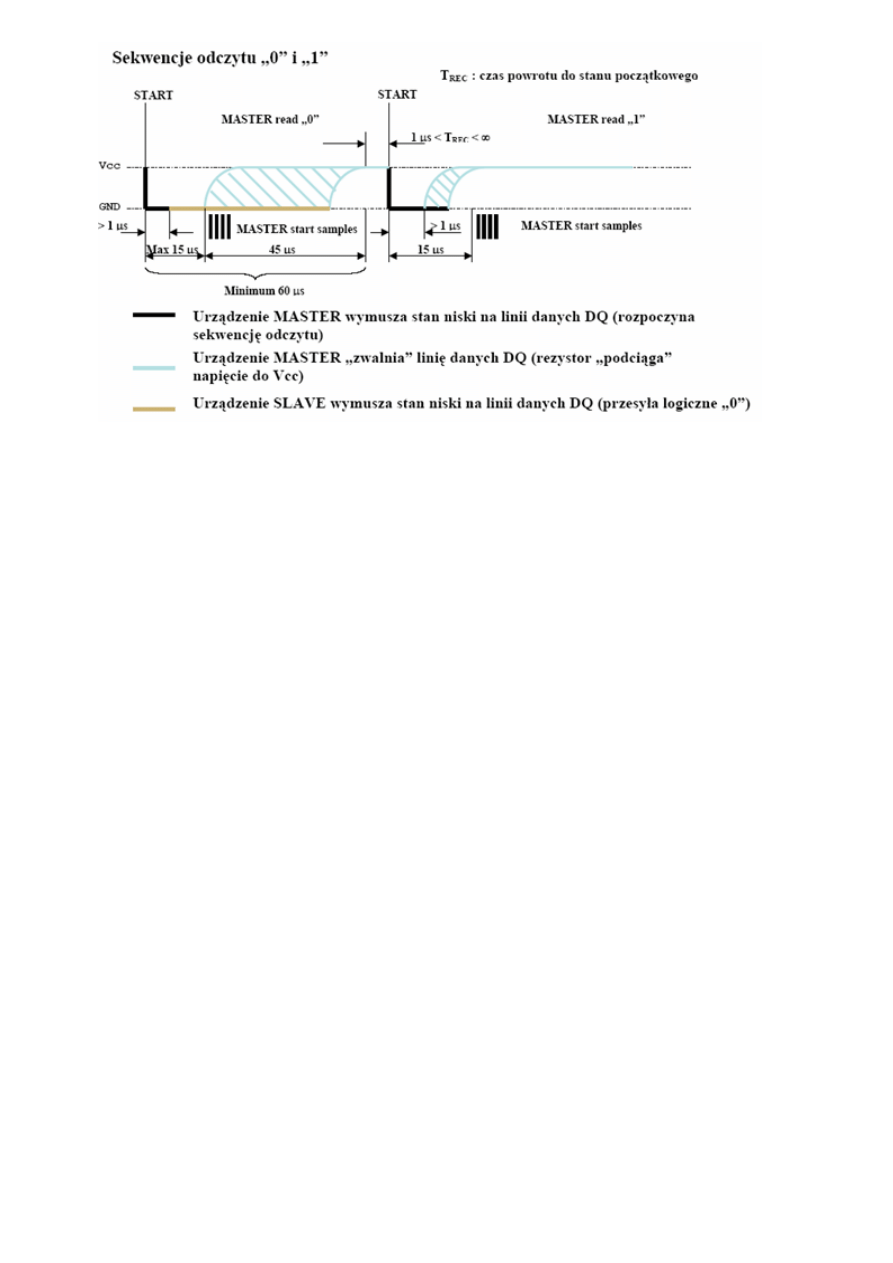

Sekwencja odczytu ‘0’ i ‘1’

Układ Master generuje impuls o czasie trwania min 1µs a następnie zwalnia linię DQ. Jeżeli Slave chce

wysład logiczną jedynkę - nie robi nic pozostawiając linię w stanie wysokim. Jeżeli Slave chce wysład 0

wówczas zwiera linię danych do masy. Po przesłaniu 8bitów nastepuje wysłanie komendy rozkazu

3.

Co to jest stan wysokiej impedancji i jakie ma on znaczenie w systemie mikroprocesorowym.

Stan wysokiej impedancji jest to stan, w którym bramka na wyjściu nie posiada ani stanu wysokiego,

ani niskiego. Jej wyjście jest praktycznie odizolowane od wejśd. Dzięki temu możliwe jest proste

zrealizowanie portów dwukierunkowych bez ryzyka uszkodzenia bramek (w wyniku połączenia z sobą

dwóch wyjśd), dwukierunkowych magistral danych. Stan wysokiej impedancji jest aktywowany

poprzez ustawienie stanu wysokiego na określonym wejściu bramki trójstanowej.

4.

Podad sposób wyznaczania adresu podprogramu obsługi przerwania sprzętowego w procesorze

x86 podczas pracy w trybie rzeczywistym i chronionym.

5.

Podad (w postaci dwójkowej) dwie przykładowe czterobitowe liczby, które po zsumowaniu w

czterobitowym sumatorze powodują ustawienie znacznika N (wartośd ujemna) i jednoczesne

wyzerowanie znacznika S (znacznik znaku – U2)

6.

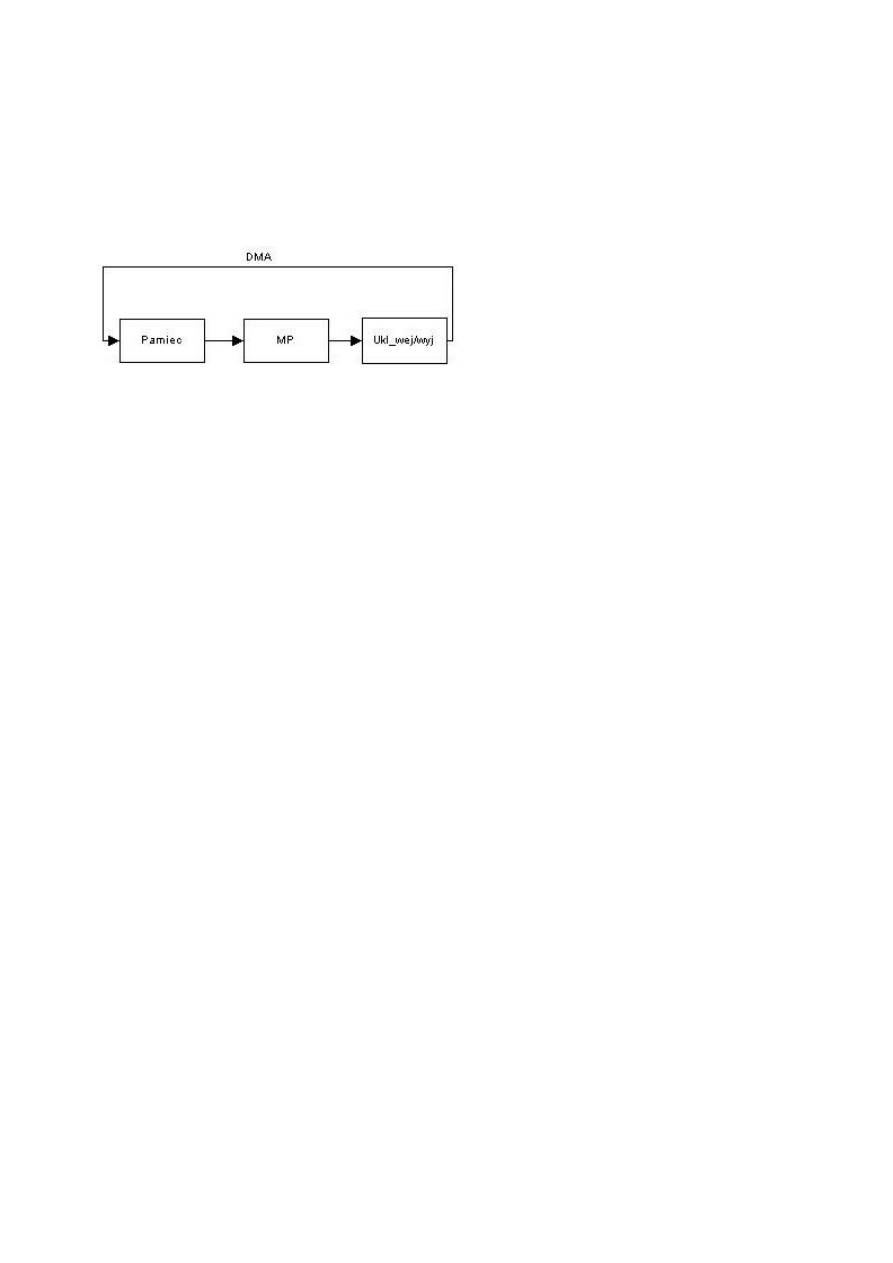

Krótko opisad mechanizm bezpośredniego dostępu do pamięci.

Tryb DMA jest trybem, w którym transmisja danych pomiędzy urządzeniami (np. we/wy) a

pamięcią odbywa się z pominięciem samego mikroprocesora. Może to byd realizowane przez sam

mikroprocesor lub przez specjalny układ zwany kontrolerem DMA. Wymaga on wcześniejszego

skonfigurowania. Tryb transferu DMA pozwala odciążyd procesor od przesłao danych między jednymi

urządzeniami a innymi. W tym czasie CPU może kontynuowad wykonywanie programu. Przykładem

kontrolera DMA jest układ 8237. Możliwe jest kaskadowe połączenie układów 8237, aby zwiększyd

ilośd urządzeo mogących pracowad w trybie DMA.

Jest to przesyłanie danych bezpośrednio z

pamięci do układu we/wy z pominięciem

mikroprocesora. Realizacja transmisji DMA

wymaga zastosowania specjalnego układu

tzw. sterownika DMA. Układ ten inicjuje

transmisję przez zablokowanie

mikroprocesora w trakcie transmisji adresuje

komórki pamięci, dlatego wymaga zewnętrznego sygnału zegarowego. Przed rozpoczęciem transmisji

musi byd odpowiednio zaprogramowany. Sama transmisja może byd wykonywana po zablokowaniu

pracy mikroprocesora lub w cyklach zegarowych, podczas których przetwarza on dane.

Układ we/wy wykorzystujący transmisję DMA musi byd wyposażony w dwa dodatkowe sygnały

sterujące(wyjściowy DRQ i wejściowy DACK). Sygnałem DRQ zgłasza się żądanie obsługi do sterownika

DMA. DACK oznacza zgodę na rozpoczęcie transmisji i jest wystawiany przez sterownik DMA

Zaletą transmisji DMA jet szybkośd przesyłania dużych ilości informacji (tzw. Bloków), wadą jest

skomplikowanie układów w postaci układu DMA i dodatkowych sygnałów sterujących.

7.

Podad w postaci dwójkowej dwie ośmiobitowe liczby, które po zsumowaniu powodują

ustawienie znacznika CY (przeniesienie) i jednoczesne wyzerowanie znacznika OV (nadmiar)

8.

Co to jest stos? Podad i opisad przykładowe operacje na stosie.

Stos (ang. LIFO, Last In, First Out; ostatni na wejściu, pierwszy na wyjściu) – liniowa struktura

danych, w której dane dokładane są na wierzch stosu i z wierzchołka stosu są pobierane. Ideę stosu

danych można zilustrowad jako stos położonych jedna na drugiej książek – nowy egzemplarz kładzie

się na wierzch stosu i z wierzchu stosu zdejmuje się kolejne egzemplarze. Elementy stosu poniżej

wierzchołka stosu można wyłącznie obejrzed, aby je ściągnąd, trzeba najpierw po kolei ściągnąd to, co

jest nad nimi.

Przykładowe instrukcje:

Push – odłożenie obiektu na stos

Pop – ściągnięcie obiektu ze stosu i zwrócenie jego wartości

Call – odłożenie adresu następnej instrukcji na stos

Ret – ściągnięcie adresu ze stosu; powrót z podprogramu

Pamięd SRAM w układach AVR powierzono dodatkową i istotną rolę. Poza miejscem przechowywania

danych, pamięd ta stanowi jednocześnie stos mikrokontrolera. Pamięd stosu wykorzystana może byd

do tymczasowego przetrzymywania zmiennych lokalnych oraz zapamiętywania adresów powrotu

przy wywoływaniu podprogramów.

Dokładanie danych na stos (push) powoduje dekrementację wskaźnika stosu, a ich ściąganie (po)

jego inkrementacje. Konsekwentnie wywołanie podprogramu (call, wystąpienie przerwania)

zmniejsza wartośd tego wskaźnika (przesyła na stos adres powrotu), powrót( Ret, reti) jego

zwiększenie. W przypadku skoków na stos odkładany jest licznik programu o długości 2 bajtów.

9.

Porównad technologię MMX i SSE.

MMX jest dodatkowym zestawem instrukcji wprowadzonym w procesorach Pentium MMX.

MMX pozwala za pomocą jednej instrukcji wykonywad operacje na zbiorze kilku danych (SIMD –

single instruction, multiple data). Instrukcje te służą do operowania liczbami całkowitymi (z i bez

znaku). Instrukcje MMX pozwalają również na przeprowadzanie obliczeo z tzw. nasycaniem. Dzięki

temu dodanie dwóch liczb, które przepełniłyby rejestr spowoduje ustawienie w nim najwyższej

możliwej wartości. Zestaw instrukcji SSE (Streaming SIMD Extensions) został wprowadzony do

procesorów Pentium III. Pozwala na wykonywanie instrukcji SIMD na liczbach

zmiennoprzecinkowych.

10.

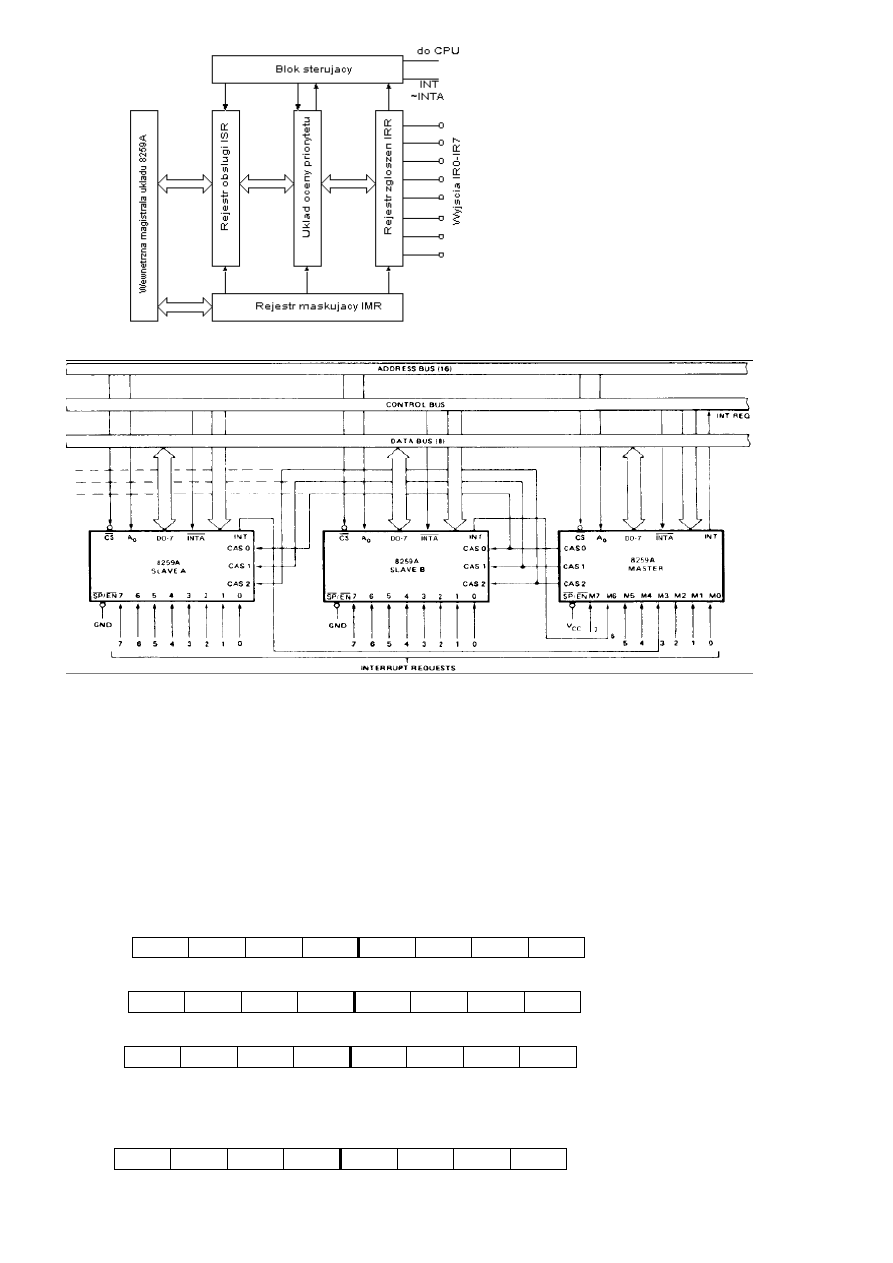

Kaskadowe łączenie kontrolerów przerwao i kontrolerów bezpośredniego dostępu do pamięci.

Podad różnice i podobieostwa.

Kontroler przerwao jest urządzeniem pozwalającym na zgłaszanie przerwao przez wiele urządzeo

przy wykorzystaniu jednej linii przerwao mikroprocesora. Układ umożliwia także ustawianie

priorytetów przerwao. Pojedynczy 8259 umożliwia obsługę 8 przerwao. Możliwe jest jednak

podłączenie kaskadowe kontrolerów, co pozwala obsłużyd ich większą ilośd. Połączenie takie jest

realizowane jak na rysunku. Jedno z urządzeo pracuje w trybie master, z kolei pozostałe kontrolery

działają jako układ slave. Wyprowadzenia CAS0:2 wszystkich urządzeo łączy się ze sobą równolegle.

Linie kontrolera master przesyłają sygnały do układów slave. Z kolei wyjścia INT układów slave są

podłączane do wejśd M7:0 układu master (każdy slave do jednego wejścia Mx). Wyjście INT układu

master jest podłączone z wejściem IRQ mikroprocesora. Układy wymagają skonfigurowania do

pracy w trybie kaskadowym.

Układy połączone są ze sobą trzema liniami adresowymi CAS0:2. Każdy z kontrolerów

rozpoznaje swoją rolę (Master lub Slave) badając poziom sygnału SP/EN. Zero logiczne konfiguruje

układ jako SLAVE. Do każdego kaskado połączonego kontrolera doprowadzony jest z procesora

sygnał INTA. lecz tylko układ Mastter jest połączony ze swojego wyjścia INT z wejściem procesora

INTREQ.

Obsługa przerwao od układu MASTER:

Urządzenie połączone z wejściem o numerze n zgłasza przerwanie wymuszając wysoki poziom

logiczny na linii IRn

Jeżeli bit n w rejestrze maskującym IMR jest ustawiony to powoduje ignorowanie wszelkich

przerwao nadchodzących tą linią, jeżeli nie to powoduje ustawienie n-tego bitu w rejestrze zgłoszeo

IRR

Następnie układ oceny priorytetu wybiera w przypadku większej liczby zgłoszeo to o najwyższym

priorytecie i wysyła go do rejestru obsługi ISR

w ISR obsługiwane jest przerwanie , procesor wysyła sygnał INTA a kontroler odpowiada do niego

wystawieniem na szynę danych D0:7 wektora przerwao

następnie rejestr ISR jest zerowany co objawia się gotowością do obsługi kolejnego przerwania

Obsługa przerwao od układu SLAVE:

zgłoszenie ustawia n bit w rejestrze zgłoszeo IRR układu SLAVE i po opracowaniu priorytetów,

wysyła sygnał INT do układu Master

układ master otrzymuje zgłoszenie na linii IR2, co powoduje ustawienie bitu 2 w rejestrze IRR

układ master opracowawszy priorytet własnych zgłoszeo, wysyła sygnał INT do procesora

procesor odpowiada pierwszym sygnałem INTA, następnie układ Master adresuje liniami CAS0:2

układ Slave odpowiadający za obsługę zgłoszonego przerwania

w obu układach następuje przesunięcie bitu odpowiadającego obsługiwanemu kanałowi z IRR do

ISR

drugi impuls INTA Z CPU nakazuje układowi Slave wystawienie na szynę danych (D7:0) wektora

przerwao

zerowane są rejestry ISR układu Master i Slave

11.

Sumowanie dwucyfrowych liczb w kodzie BCD. (znacznik przeniesienia połówkowego, zasada

stosowania poprawki BCD)

BCD – Binary Coded Decimal – kod dwójkowo-dziesiętny, który przyporządkowuje cyfrom

dziesiętnym od 0 do 9 wektory informacji cyfrowej zwane z tego powodu kęsami BCD.

Najważniejszą zaletą kodów BCD jest prostota konwersji liczb pomiędzy postaciami: dziesiętną i

binarną. Typowe zastosowania to: wyświetlacze liczb w postaci dziesiętnej np. kalkulatory.

Przykład liczbie 1937 w kodzie BCD odpowiada: 0001 1001 0011 0111

Poprawka BCD:

0

0

1

0

0

1

1

1

+

0

1

0

0

1

0

0

1

=

0

1

1

1

0

0

0

0

Należy zastosowad poprawkę BCD, ponieważ w wyniku dodawania nastąpiło przeniesienie pomiędzy

segmentami. Poprawka ta polega na dodaniu 6. Ostateczny wynik po poprawce wygląda następująco:

0

1

1

1

0

1

1

0

W powyższym przykładzie wszystko jest OK, nastąpiło przeniesienie -> dodano 6. Natomiast jeśli

dodamy inne liczby np. 0111 i 1000 czyli 7 i 8 wówczas jako wynik otrzymamy 1111. Z punktu widzenia

kodu BCD wynik ten jest nieprawidłowy, ponieważ w tym kodzie największą wartością na danych 4

bitach może byd 1001. W tym przypadku należy sprawdzad czy otrzymana w wyniku dodawania liczba

w danym segmencie nie jest większa od 9, jeśli tak wówczas trzeba dodad 6. Podsumowując, jeśli

mamy liczbę składającą się z dwóch kęsów BCD, tak jak na powyższych schematach, wówczas:

Jeżeli cztery mniej znaczące bity wyniku zawierają liczbę większą od 9 (tzn. od 1001) lub dodatkowe

przeniesienie ma wartośd 1, to do wartości wyniku należy dodad liczbę 6 (0110);

Jeżeli cztery bardziej znaczące bity wyniku zawierają liczbę większą niż 9 lub przeniesienie (z

najbardziej znaczącej pozycji) ma wartośd 1, to do wartości wyniku należy dodad liczbę 60 (01100000);

12.

Co to są drgania styków? Opisad sposób eliminacji wpływu drgao styków.

Drgania styków jest to efekt niepożądany jaki występuje w momencie wciskania i zwalniania

przycisku. Objawia się on występowaniem na zmianę losowych przełączeo między stanami wysokimi i

niskimi. Efekt ten utrzymuje się przez kilkanaście milisekund. Dobrym sposobem eliminacji drgao jest

zastosowanie pętli czasowej wykonywanej po wykryciu wciśnięcia przycisku tak długo, aby stan wejścia

był już stabilny.

13.

Porównad operację przesunięcia logicznego w prawo z operacją przesunięcia arytmetycznego w

prawo. Podad przykłady ilustrujące zastosowanie obu operacji do wykonywania operacji

dzielenia liczb bez znaku i ze znakiem.

Przesunięcie bitowe - operacja na liczbach dwójkowych polegająca na przesunięciu wszystkich cyfr

binarnych o n pozycji w lewo lub prawo. Najczęściej przesunięcie wykorzystuje się do szybkiego

mnożenia(lewo)/dzielenia(prawo) przez liczbę 2 i jej potęgi oraz do sekwencyjnego testowania

wartości poszczególnych bitów.

a) przesunięcie logiczne w lewo

Wszystkie wartości w liczbie przesuwane są o 1 pozycję w lewo. Na najmłodszą pozycję (LSB)

dopisywany jest bit o wartości zero, natomiast najstarszy bit (MSB) jest tracony. Wartośd liczby w

naturalnym kodzie binarnym jest 2 razy większa. Większe przesunięcia są równoważne

przemnożeniu przez potęgę dwójki.

b) przesunięcie logiczne w prawo

Wszystkie wartości w liczbie przesuwane są o 1 pozycję w prawo. Na najstarszą pozycję(MSB)

dopisywany jest bit o wartości zero, natomiast najmłodszy bit jest tracony(LSB). Wartośd liczby w

naturalnym kodzie binarnym jest 2 razy mniejsza (dzielenie całkowitoliczbowe).

c) Przesunięcie arytmetyczne w prawo

Wszystkie wartości liczby są przesuwane o 1 pozycję w prawo. Bit z najstarszej pozycji(MSB) jest

powielany, natomiast najmłodszy bit jest tracony(LSB).

Przykład:

(MSB)10010101 -> 11001010

14.

Opisad interfejs I2C. Podad sekwencję startu, powtórzonego startu, stopu, transmisji

pojedynczego bitu oraz sekwencję pełnej transmisji. Wyjaśnid zastosowanie sekwencji

powtórzonego startu.

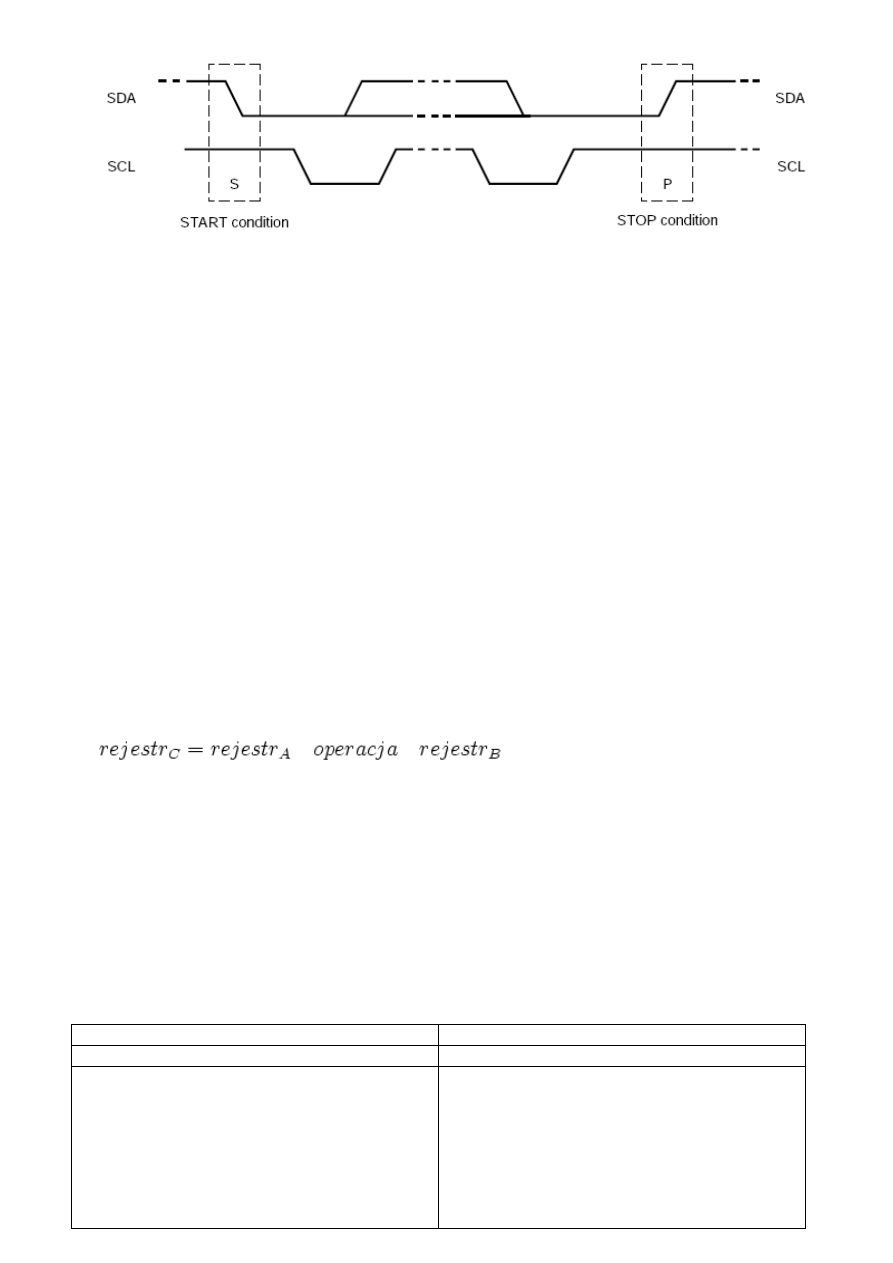

Gdy na linii SDA stan logiczny zmienia się z '1' na '0', a na linii SCL jest stan '1', to sytuacja taka nazywa

się START. Natomiast gdy na linii SDA stan logiczny zmienia się z '0' na '1', podczas wysokiego poziomu

na linii SCL, to sytuacja taka nazywa się STOP. Przedstawione to zostało na poniższych wykresach:

W protokole I

2

C transmisja danych odbywa się szeregowo, w dwóch kierunkach przy użyciu dwóch linii.

Jedna z nich SCL(serial clock Line) przesyła impulsy zegarowe synchronizujące transmisję, natomiast

druga SDA(serial data Line) przesyła dane w dwóch kierunkach.

Stan linii danych może byd zmieniany, gdy linia zegarowa SCL znajduje się w stanie niskim.

15.

Podad zasady ustawiania znaczników: przeniesienia C, wartości ujemnej N, nadmiaru U2 V, oraz

znaku S. Podad przykłady (operator i wartośd operandów), które w arytmometrze 8bitowym

dokonują ustawienia bądź wyzerowania wymienionych znaczników.

16.

Dokonad podziału mikroprocesorów pod kątem mapy pamięci oraz listy instrukcji.

Ze względu na typ listy instrukcji mikroprocesory można podzielid na:

RISC (ang. Reduced Instruction Set Computer)

Jako przykłady można wymienid: Atmel AVR, ARM, Ralpha, MIPS, SPARC, Intel 80860

CISC (ang. Complex Instruction Set Computer)

Jako przykłady można wymienid: AMD, x86

Podstawowe cechy architektury RISC w porównaniu z CISC:

Zredukowana liczba rozkazów do niezbędnego minimum. Ich liczba wynosi kilkadziesiąt, podczas gdy w

procesorach CISC sięga setek. Upraszcza to znacznie dekoder rozkazów.

Redukcja trybów adresowania, dzięki czemu kody rozkazów są prostsze, bardziej zunifikowane, co

dodatkowo upraszcza wspomniany wcześniej dekoder rozkazów. Ponadto wprowadzono tryb

adresowania, który ogranicza ilośd przesłao - większośd operacji wykonuje się wg schematu:

Ograniczenie komunikacji pomiędzy pamięcią, a procesorem. Przede wszystkim do przesyłania danych

pomiędzy pamięcią, a rejestrami służą dedykowane instrukcje, które zwykle nazywają się load (załaduj

z pamięci), oraz store (zapisz do pamięci); pozostałe instrukcje mogą operowad wyłącznie na

rejestrach. Schemat działania na liczbach znajdujących się w pamięci jest następujący: załaduj daną z

pamięci do rejestru, na zawartości rejestru wykonaj działanie, przepisz wynik z rejestru do pamięci.

Zwiększenie liczby rejestrów (np. 32, 192, 256, podczas gdy np. w architekturze x86 jest zaledwie 8

rejestrów), co również ma wpływ na zmniejszenie liczby odwołao do pamięci.

Dzięki przetwarzaniu potokowemu (ang. pipelining) wszystkie rozkazy wykonują się w jednym cyklu

maszynowym, co pozwala na znaczne uproszczenie bloku wykonawczego, a zastosowanie

superskalarności także na zrównoleglenie wykonywania rozkazów. Dodatkowo czas reakcji na

przerwania jest krótszy.

W skrócie:

RISC

CISC

Zbiór instrukcji jest ortogonalny

Rozbudowana liczba instrukcji

Mała liczba instrukcji

Zredukowana liczba rozkazów, upraszcza to

znacznie dekoder rozkazów

Redukcja trybu adresowania => prostsze kody

rozkazów

Ograniczenie komunikacji między pamięcią a

procesorem. Do przesyłanie danych między

pamięcią a rejestrami służa dedykowane instrukcje

Wysoka specjalizacja instrukcji

Duża liczba rozkazów

Niektóre rozkazy potrzebują dużej liczby cykli

procesora do wykonania

Wystąpienie złożonych ,specjalistycznych rozkazów

Duża liczba trybów adresowania

Do pamięci może odwoływad się duża liczba

rozkazów

(load, store)

Zwiększenie liczby rejestrów(np.32,192,256)

Dzięki przetwarzaniu potokowemu (pip eling)

wszystkie rozkazy wykonują się w jednym cyklu

maszynowym

Mniejsza od układów RISC częstotliwośd taktowania

procesora

Powolne działanie dekodera rozkazów

17.

Wyjaśnid działanie instrukcji wywołania podprogramu i powrotu z podprogramu. Dokonad

porównania z mechanizmem wywołania podprogramu obsługi przerwania oraz z instrukcją

powrotu z podprogramu obsługi przerwania.

18.

Zaprojektowad dekoder adresów który wystawia sygnał CS niski dla adresów w zakresie *0x20,

0x2F+ oraz CS wysoki dla pozostałych adresów w przypadku 16 bitowej magistrali adresowej.

Wyszukiwarka

Podobne podstrony:

Historia wojen 01 Opracowanie pytan id 204401

Nasze opracowanie pytań 1 40

Opracowanie pytań z anatomii

opracowanie pytań z optyki

Maszyny Elektryczne Opracowanie Pytań Na Egzamin

opracowanie pytan id 338374 Nieznany

opracowanie pytan karafiata

Opracowanie pytań 2 kolokwium

cw 3 broma opracowanie pytan 810

Nhip opracowanie pytan id 31802 Nieznany

filozofia opracowanie pytań

opracowanie pytan Automatyka

pytania egz ekonimak II, OPRACOWANIE PYTAŃ NA EGZAMIN

Zestaw 88 Kasia Goszczyńska, materiały farmacja, Materiały 3 rok, Od Ani, biochemia, biochemia, opra

opracowane zestawy, OPRACOWANIE PYTAŃ NA EGZAMIN

Opracowanie pytań MAMET METALE

więcej podobnych podstron