Programowalne uk ady logiczne

Termin logiczne uk ady programowalne PLD (Programmable Logic Devices) odnosi si do

ka dego cyfrowego uk adu scalonego, którego w a ciwo ci funkcjonalne mog

by

zdefiniowane (ustalane) przez ko cowego u ytkownika, który mo e zaimplementowa w jego

strukturze opracowany przez siebie projekt jakiego wyspecjalizowanego uk adu cyfrowego.

Najwa niejsz cech tych uk adów jest wi c ich konfigurowalno

przez u ytkownika w jego

w asnym laboratorium.

Wspó czesne uk ady programowalne klasyfikuje si najcz ciej w trzech grupach, przy czym

kryterium klasyfikacji s g ównie cechy ich architektury. Najcz ciej przyjmuje si , e uk ady

PLD dzieli si na:

•

SPLD (Simple Programmable Logic Device) – proste uk ady programowalne,

•

CPLD (Complex Programmable Logic Devices) – z o one uk ady programowalne,

•

FPGA (Field Programmable Gate Array) – programowalne matryce bramkowe.

Do uk adów SPLD zalicza si uk ady programowalne o architekturach PLA (Programmable

Logic Array), PAL (Programmable Array Logic) i GAL (Generic Array Logic). S to uk ady o

najskromniejszych mo liwo ciach logicznych, a wi c i najta sze ze wszystkich uk adów

programowalnych. Niemniej jednak ich zasoby logiczne s spore, zawieraj bowiem typowo od

4 do 22 makrokomórek logicznych o dwupoziomowej strukturze logicznej i mog

zwykle

zast pi kilka standardowych uk adów scalonych rodziny 74xx. Ka da z komórek jest zwykle w

pe ni po czona z innymi komórkami w danym uk adzie scalonym. Do okre lenia funkcji

realizowanych przez makrokomórki (ich skonfigurowania) stosowane s

czniki (klucze),

którymi s w wi kszo ci przypadków przepalane fragmenty cie ek ( czniki rozwarciowe – dla

uk adów PLA i PAL) lub tranzystory MOS (dla uk adów GAL).

Uk ady CPLD s koncepcyjnie podobne do uk adów SPLD, lecz s bardziej z o one: maj

wi ksze zasoby logiczne i mo liwo ci funkcjonalne. Ich architektura ma struktur hierarchiczn

opart

na makrokomórkach logicznych, których zawieraj

od kilkudziesi ciu do kilkuset.

Typowo od czterech do szesnastu makrokomórek jest po czonych w wi kszy blok

funkcjonalny. Jedn

z wa niejszych cech architektury uk adów CPLD jest liczba termów

przypadaj cych na pojedyncz makrokomórk oraz mo liwo

po yczki termów z s siednich

makrokomórek. Je li uk ad zawiera wiele bloków funkcjonalnych, s one czone mi dzy sob

za pomoc

matrycy po czeniowej kluczy, której zdolno

czeniowa jest wa n

cech

uk adów CPLD. Ta liczba po cze

wewn trz matrycy okre la bowiem, jak atwo jest

„wpasowa ” jaki projekt w dany uk ad programowalny.

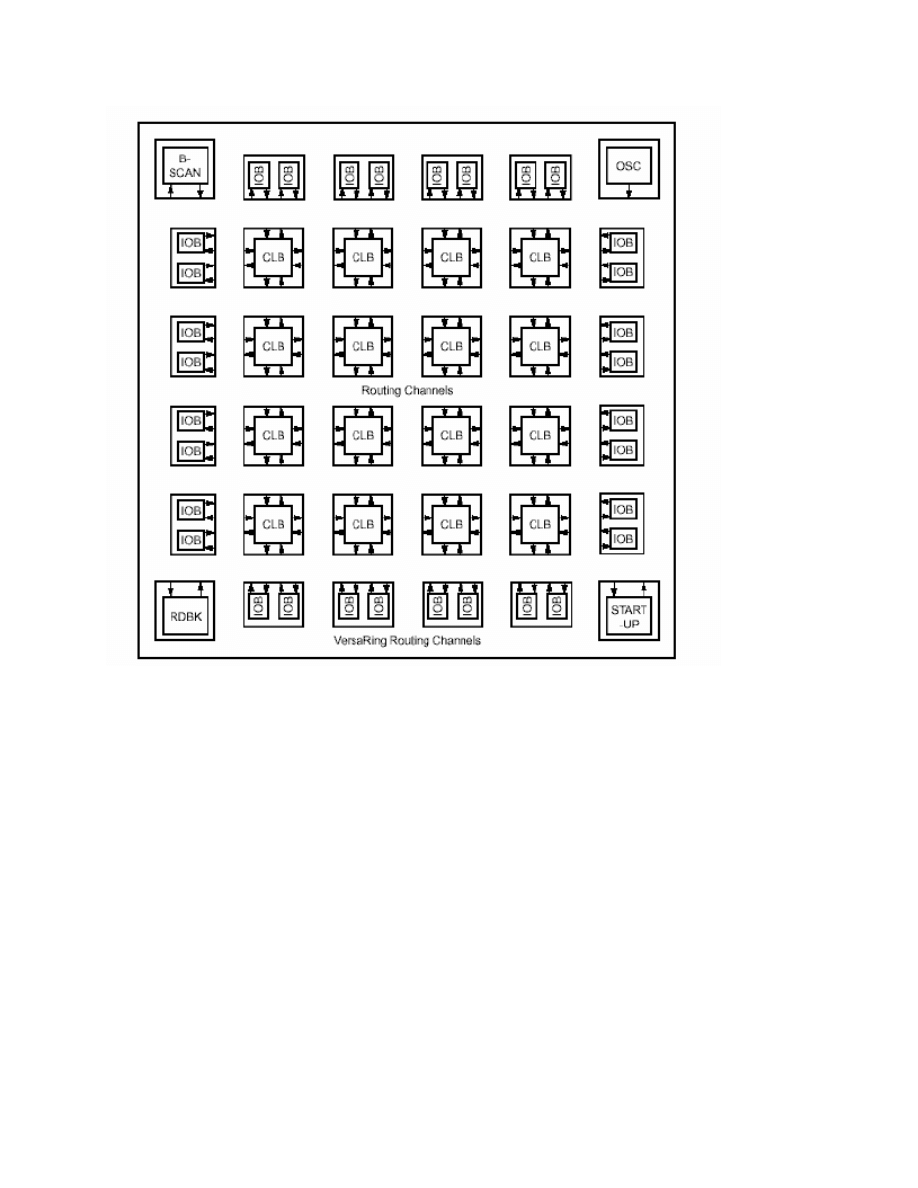

Architektura uk adów FPGA ró ni si od architektury uk adów CPLD. Na ogó uk ady FPGA

zawieraj

rozmieszczone matrycowo boki logiczne CLB (rys. 4.1). Poszczególne bloki s

czone ze sob

za po rednictwem linii traktów po czeniowych (Routing Channels) oraz

programowalnych matryc kluczy po czeniowych umieszczonych w miejscu krzy owania si

traktów poziomych i pionowych. Na obrze ach matrycy bloków logicznych znajduj

si

programowalne bloki IOB (wej ciowo-wyj ciowe). Struktury FPGA zawieraj

od 64 do

dziesi tków tysi cy bloków logicznych o bardzo zró nicowanej budowie. Bloki logiczne mog

by bardzo z o one, jest ich wówczas mniej w uk adzie, lub wzgl dnie proste i jest ich wówczas

wi cej. Zazwyczaj z o one bloki logiczne zawieraj

dwie lub wi cej pami ci RAM

umo liwiaj cych tworzenie tablic warto ci funkcji LUT (Look-up Table) i dwa lub wi cej

przerzutników. W wi kszo ci uk adów s

to tablice czterowej ciowe (pami RAM o

pojemno ci 16 bitów). W uk adach o prostszej budowie, bloki logiczne zawieraj

zwykle

dwuwej ciowe uk ady generacji funkcji kombinacyjnych lub multipleksery czterowej ciowe i

ewentualnie przerzutniki.

Schemat blokowy uk adu FPGA

Do grupy najwi kszych producentów uk adów programowalnych i narz dzi komputerowych do

ich syntezy nale nast puj ce firmy: Altera (

www.altera.com

), Lattice (

www.latticesemi.com

),

Xilinx (

www.xilinx.com

), Cypress (

www.cypress.com

), Atmel (

www.atmel.com

) i QuickLogic

(

www.quicklogic.com

).

Uk ady logiczne SPLD na przyk adzie uk adu GAL16V8

Obecnie najpopularniejsz grup uk adów SPLD s uk ady GAL, w których wykorzystano

architektur

PAL wzbogacon

o konfigurowalne makrokomórki wyj ciowe zawieraj ce

przerzutniki typu D. Przerzutniki te spe niaj

rol

wyj ciowych elementów pami ciowych

umo liwiaj cych budowanie uk adów synchronicznych.

Uk ady programowalne GAL zostan przedstawione na przyk adzie uk adu GAL16V8 firmy

Lattice. Jest on wykonany w technologii CMOS i zawiera elektrycznie reprogramowalne

komórki pami ci typu E

2

CMOS. Uk ad ten charakteryzuje si nast puj cymi cechami:

•

Wysoko wydajna technologia E

2

CMOS (3,5ns maksymalny czas propagacji, F

max

=

•

250MHz, 3ns od wej cia zegara do wyj cia danych).

•

Rezystory podwieszone na ka dej ko cówce (active pull-up).

•

Technologia E

2

CELL (rekonfigurowalna logika, reprogramowalne komórki, bardzo

•

szybkie elektrycznie kasowanie (poni ej 100ms), czas podtrzymywania danych 20 lat).

•

Osiem wyj ciowych makrokomórek (programowalna polaryzacja wyj , emulacja 20-

pinowych uk adów PAL).

•

Wst pny zapis (preload) i reset po w czeniu zasilania (power-on reset) wszystkich

rejestrów .

Identyfikacyjny „elektroniczny podpis” zawarty w uk adzie.

Uk ad sk ada si z nast puj cych bloków:

•

z 9 buforów wej ciowych,

•

matrycy po cze logicznych PROGRAMMABLE AND-ARRAY,

•

z 8 programowalnych logicznych wyj ciowych makrokomórek OLMC (Output Logic

•

MacroCell),

•

8 trójstanowych buforów wyj ciowych konfigurowanych przez u ytkownika,

•

uk adu ochrony danych przed odczytem.

Bufory wej ciowe uk adu GAL16V8 s

kompatybilne ze standartowymi poziomami TTL.

Bufory te charakteryzuj si wysoka impedancj i reprezentuj o wiele mniejsze obci eniedla

steruj cej logiki ni bipolarne uk ady TTL. Wej cia uk adu maja wbudowane aktywne rezystory

podwieszaj ce (Active Pull-Up), wi c niepo czone b d w stanie „wysokim” (logiczna „1”).

Producent zaleca aby wszystkie nieu ywane wej cia uk adu i trzystanowe piny I/O by y

pod czone do zasilania uk adu lub masy. Zwi ksza to odporno

na zak ócenia i redukuje pr d

pobierany przez uk ad.

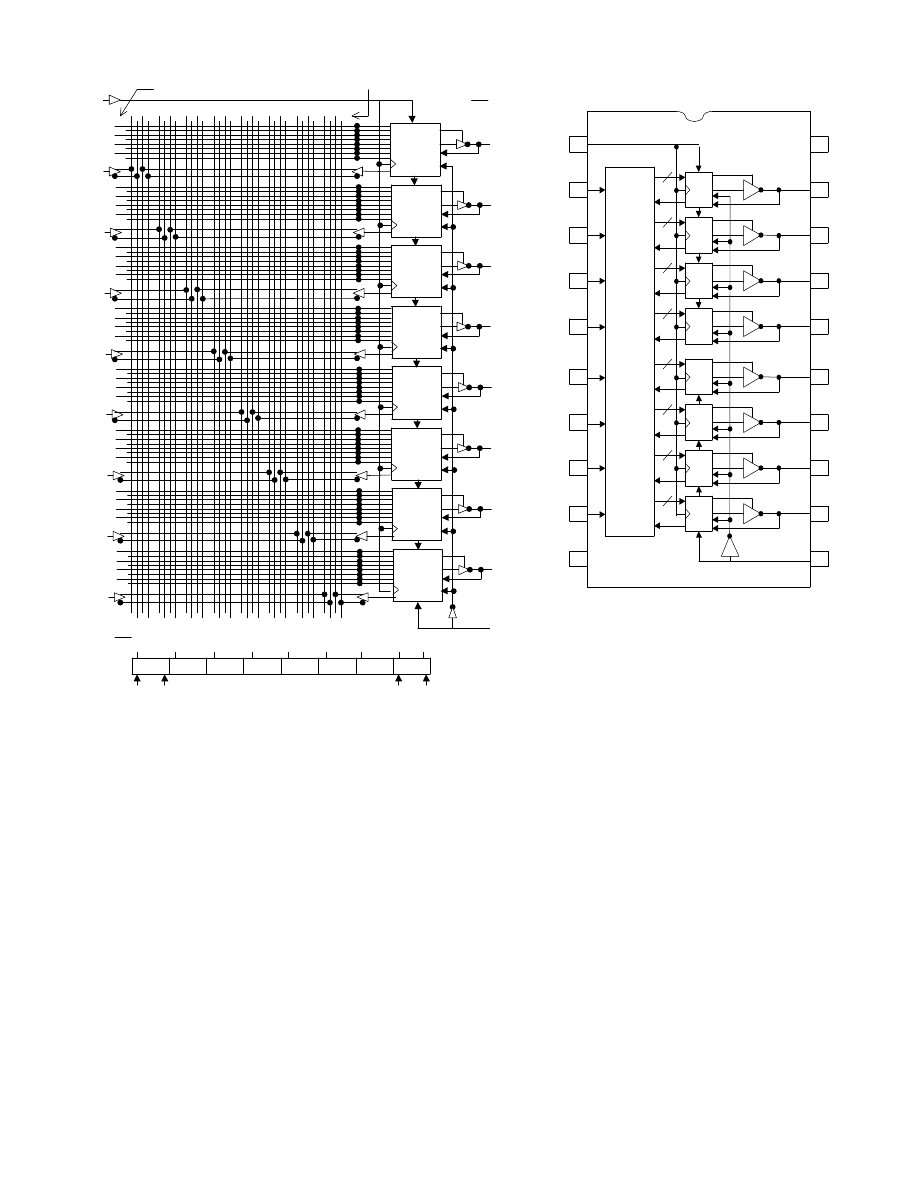

Matryca po cze

logicznych sk ada si

z programowalnej macierzy typu AND array z

ustalonymi po czeniami do bramek typu OR. Pole logicznych po cze jest zorganizowane jako

16 komplementarnych linii wej ciowych (z sygna ami i ich negacjami) krzy uj cych si z 64

liniami typu „product term”. Na ka dym skrzy owaniu linii znajduje si

komórka typu

OLMC

XOR=2048

AC1=2120

PTD=2128

-2135

19

2

OLMC

XOR=2049

AC1=2121

PTD=2136

-2143

18

3

OLMC

XOR=2050

AC1=2122

PTD=2144

-2151

17

4

OLMC

XOR=2051

AC1=2123

PTD=2152

-2159

16

5

OLMC

XOR=2052

AC1=2124

PTD=2160

-2167

15

6

OLMC

XOR=2053

AC1=2125

PTD=2168

-2175

14

7

OLMC

XOR=2054

AC1=2126

PTD=2176

-2183

13

8

OLMC

XOR=2055

AC1=2127

PTD=2184

-2191

12

9

0

2

4

6

8

10 12 14 16 18 20 22 24 26 28 30

1

3

5

7

9

11 13 15 17 19 21 23 25 27 29 31

0

2

4

6

8

10 12 14 16 18 20 22 24 26 28 30

1

3

5

7

9

11 13 15 17 19 21 23 25 27 29 31

1

11

00

64

128

192

32

96

160

224

256

320

384

448

288

352

416

480

512

576

640

704

544

608

672

736

768

832

896

960

800

864

928

992

1024

1088

1152

1216

1056

1120

1184

1248

1280

1344

1408

1472

1312

1376

1440

1504

1536

1600

1664

1728

1568

1632

1696

1760

1792

1856

1920

1984

1824

1888

1952

2016

Input Line Numbers

Product Line First Number

20

Vcc

10

GND

BYTE 0 BYTE 1

BYTE 2

BYTE 3

BYTE 4

BYTE 5 BYTE 6

BYTE 7

2056

2064

2072

2080

2088

2096

2104

2112 2119

MSB

LSB

LSB

MSB

User Electronic Signature Word

GAL 16V8 Logic Diagram

JEDEC Logic Array Cell Number = Product Line First Cell Number + Input Line Number

C, I 1

I

2

20 Vcc

19 I/O

GND 10

8

8

8

8

8

8

8

8

OLMC

OLMC

OLMC

OLMC

OLMC

OLMC

OLMC

OLMC

I

3

I

4

I

5

I

6

I

7

I

8

I

9

18 I/O

17 I/O

16 I/O

15 I/O

14 I/O

13 I/O

12 I/O

11 /G, I

AND

ARRAY

GAL 16V8 Block Diagram - DIP Connections

E

2

PROM, która w zale no ci od zaprogramowania zwiera lub rozwiera lini

poziom

od

pionowej.

cznie w matrycy znajduje si 2048 komórek

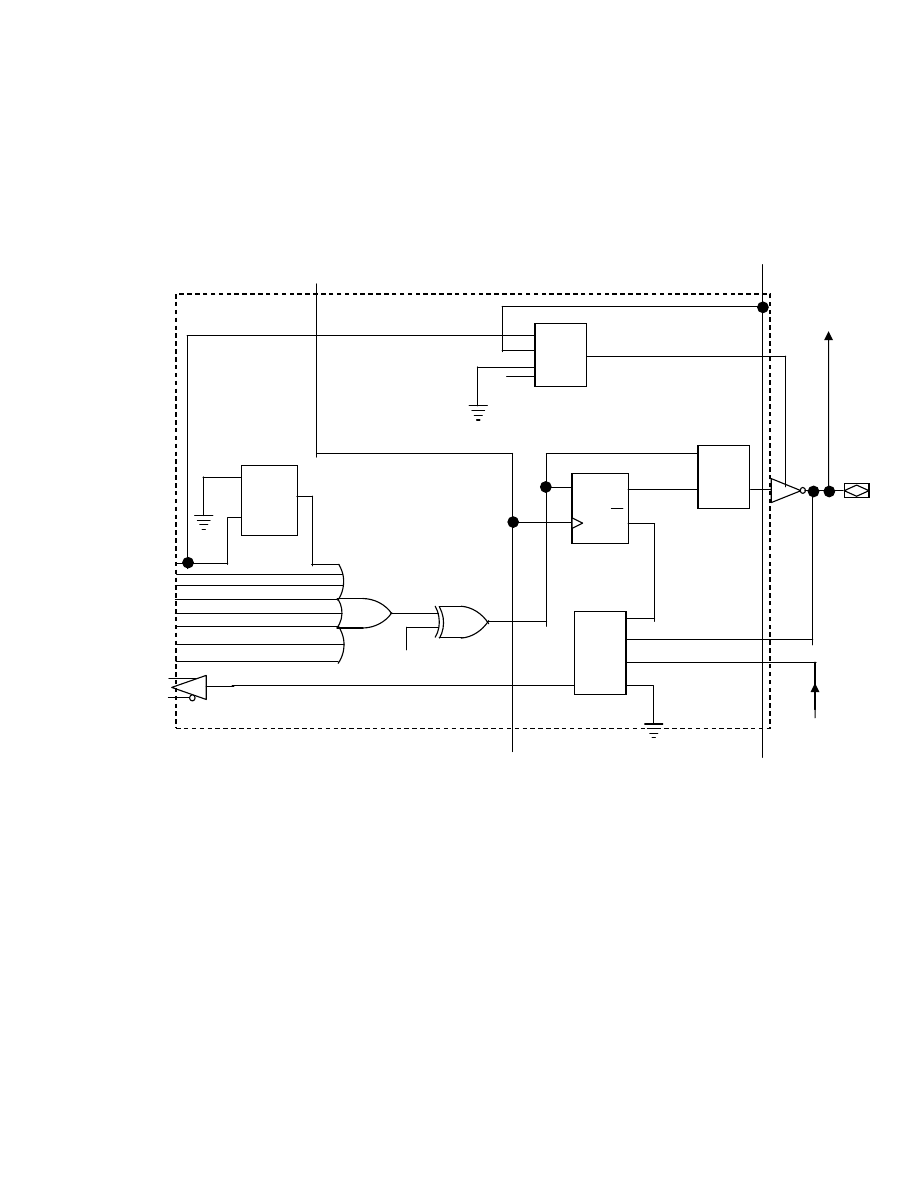

STRUKTURA GAL

BUDOWA MAKROKOMÓRKI

Schemat logiczny makrokomórki OLMC

Konfiguracja komórki OLMC jest ustawiana przez programatory i oprogramowanie

narz dziowe oraz jest ca kowicie niewidoczna (przezroczysta) dla u ytkownika. Komórk

OLMC mo na ustawi w trzech trybach:

•

prostym (simple),

•

z o onym (complex),

•

rejestrowym (registered).

O konfiguracji wszystkich makrokomórek OLMC decyduj dwa globalne bity SYN i AC0.

PT

MUX

TS

MUX

O

MUX

F

MUX

D

Q

Q

XOR

(n)

clk

OE

TO

ADJACENT

STAGE

I/O (n)

FROM

ADJACENT

STAGE

OUTPUT (m)

OE

clk

FROM

AND

ARRAY

FEED

BACK

V

cc

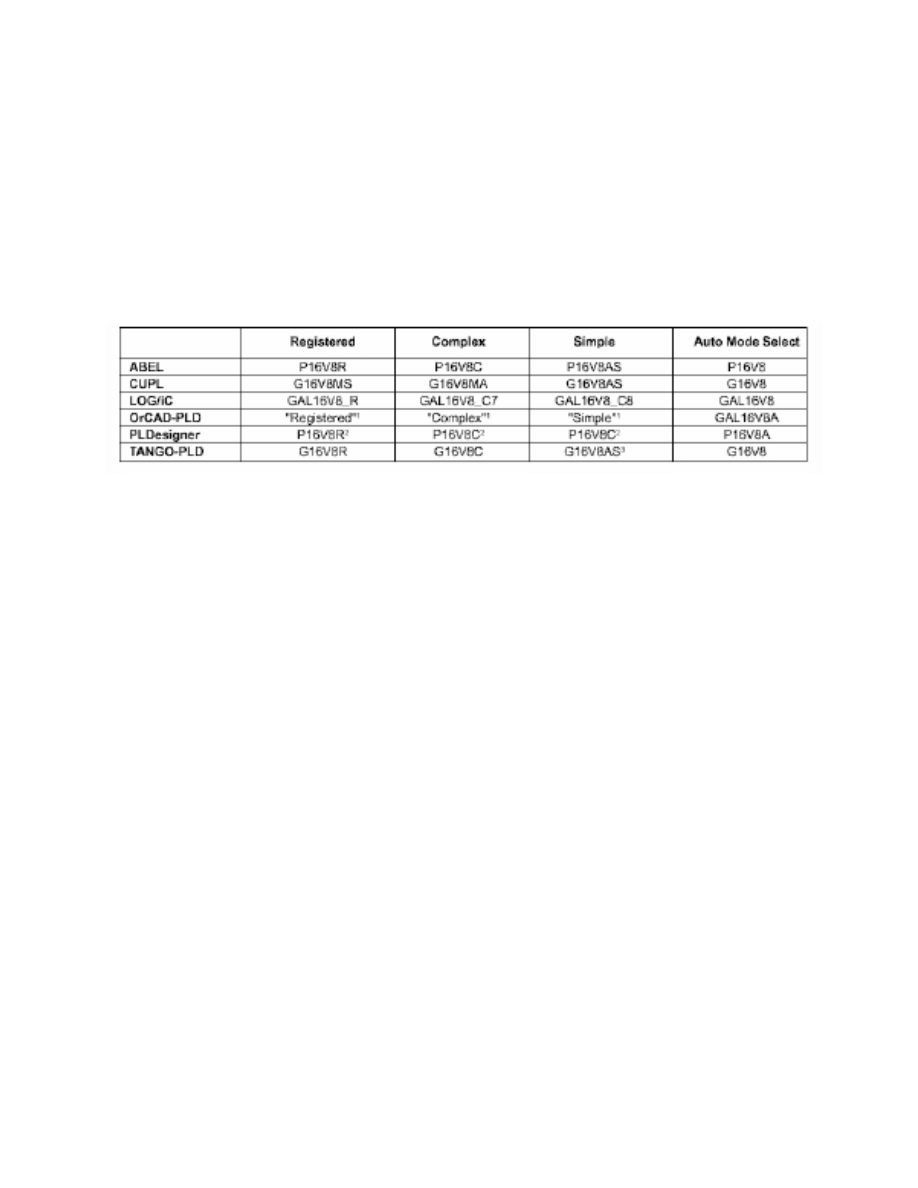

Bit XOR ka dej komórki ustawia polaryzacj wyj cia w ka dym z trzech trybów, natomiast bit

AC1 ustala kierunek (wej cie lub wyj cie). Dwa globalne i 16 indywidualnych bitów definiuje

wszystkie mo liwe konfiguracje uk adu GAL16V8. Kompilatory ustawi te bity automatycznie

tak, i u ytkownik nie musi ich samodzielnie ustawia . Ni ej podana jest w tabeli poniMej lista

deklaracji uk adu GAL dla poszczególnych kompilatorów, za pomoc których mo na wybra

tryb pracy uk adu GAL (typ wyj cia komórki OLMC). W pierwszej kolumnie tabeli zawarto list

dost pnych kompilatorów.

Uk ady logiczne CPLD na przyk adzie rodziny uk adów XC9500 firmy

Xilinx

Uk ady logiczne CPLD zostan przedstawione na przyk adzie rodziny uk adów XC9500 firmy

Xilinx. S one programowalne i testowalne w docelowym mse. Rodzina ta charakteryzuje si

nast puj cymi w a ciwo ciami:

•

du a szybko

dzia ania (5ns opó nienia pomi dzy pinami, f

CNT

do 125 MHz),

•

du a g sto upakowania (od 36 do 288 makrokomórek z 800 do 6,400 u ytecznymi

bramkami),

•

uk ady programowalne w systemie o napi ciu zasilania 5V (mo liwo wykonania

10000 cykli programowania/kasowania),

•

uk ady sk adaj si z „elastycznych” bloków funkcyjnych (odpowiadaj cych uk adom

•

GAL typu 36V18), 90 linii product terms steruj cych pojedynczymi lub wszystkimi 18

makrokomórkami wewn trz bloku funkcyjnego,

•

posiadaj interfejs standardu IEEE 1149.1 (JTAG),

•

zapewniaj programowalny tryb redukcji mocy dla ka dej komórki,

•

wyj cia uk adów przewodz pr d do 24mA,

•

piny wej ciowo-wyj ciowe mog by ustawione na standard 3,3V lub 5V.

•

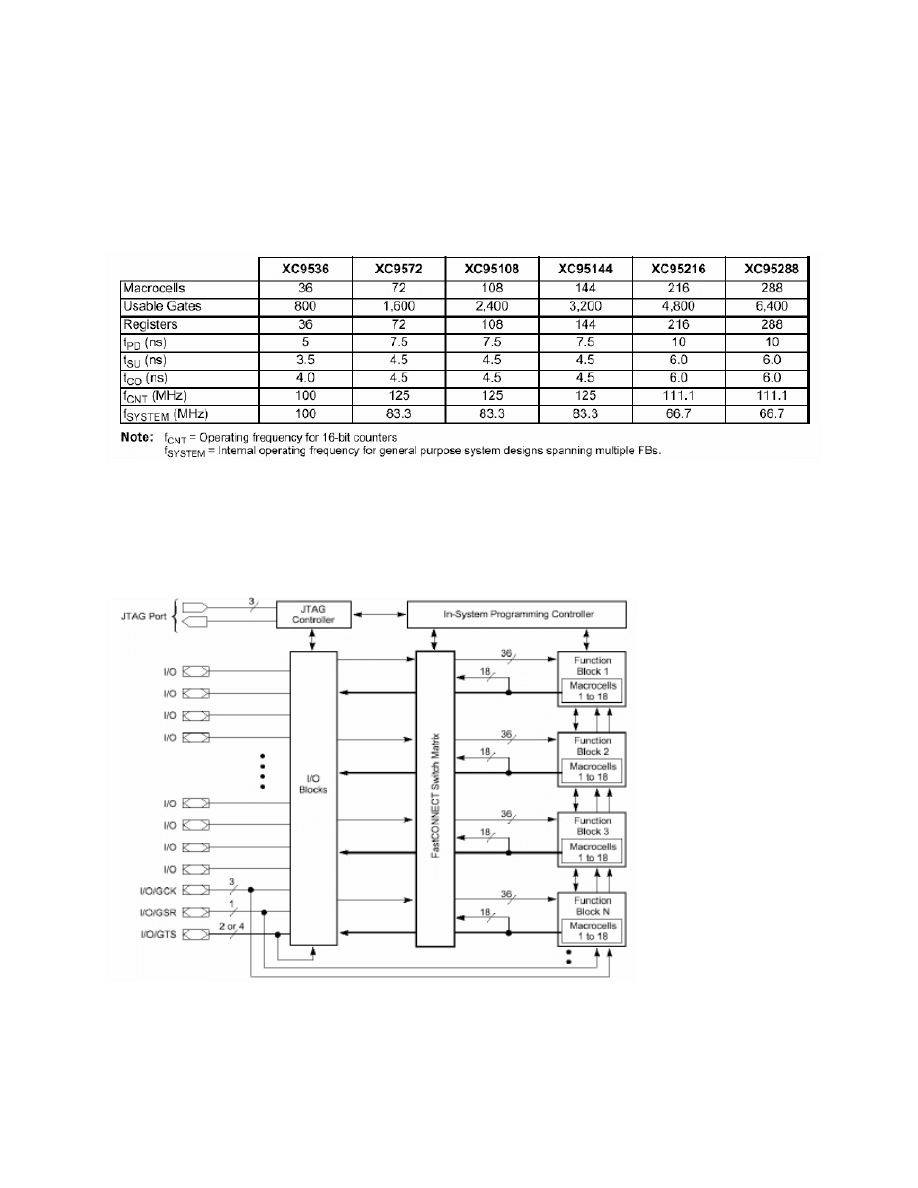

W tabeli poniMej zestawiono uk ady rodziny XC9500. Jak wida g sto

upakowania

u ywanych bramek logicznych mie ci si

w przedziale od 800 do ponad 6400, a

rejestrów od 36 do 288.

Rodzina uk adów XC9500

Na potrzeby programowania i testowania uk adów w systemie rozszerzono list

instrukcji

steruj cych interfejsem JTAG. Zatem interfejs ten pozwala nie tylko na testowanie zgodnie ze

standardem IEEE 1149.1, ale równie

i programowanie uk adów zamontowanych ju

w

systemie.

Architektura uk adów rodziny XC9500

Mo liwo

przeprowadzania wielokrotnej liczby cykli programowania/kasowania zapewnia

du swobod w zmienianiu wewn trznej konfiguracji uk adów, czy uaktualnianiu zawartych w

nich projektów. Dodatkowo zapewniono kontrol szybko ci narastania napi wyj ciowych

oraz umo liwiono programowe uziemienie pinów w celu lepszej redukcji szumów. Urz dzenia

wej cia/wyj cia mog by konfigurowane dla napi 3,3V oraz 5V.

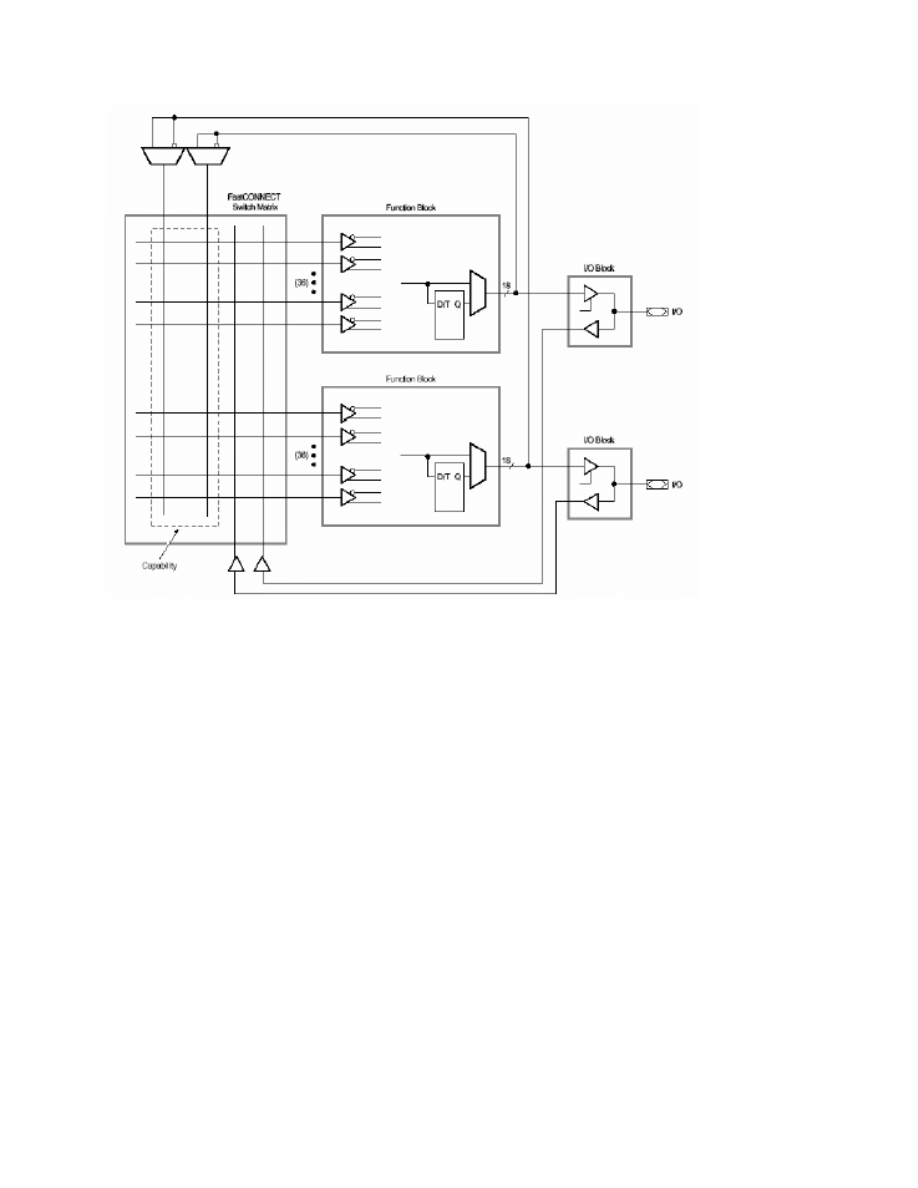

Wszystkie wyj cia przewodz

pr d do 24mA. Ka dy uk ad XC9500 jest podsystemem

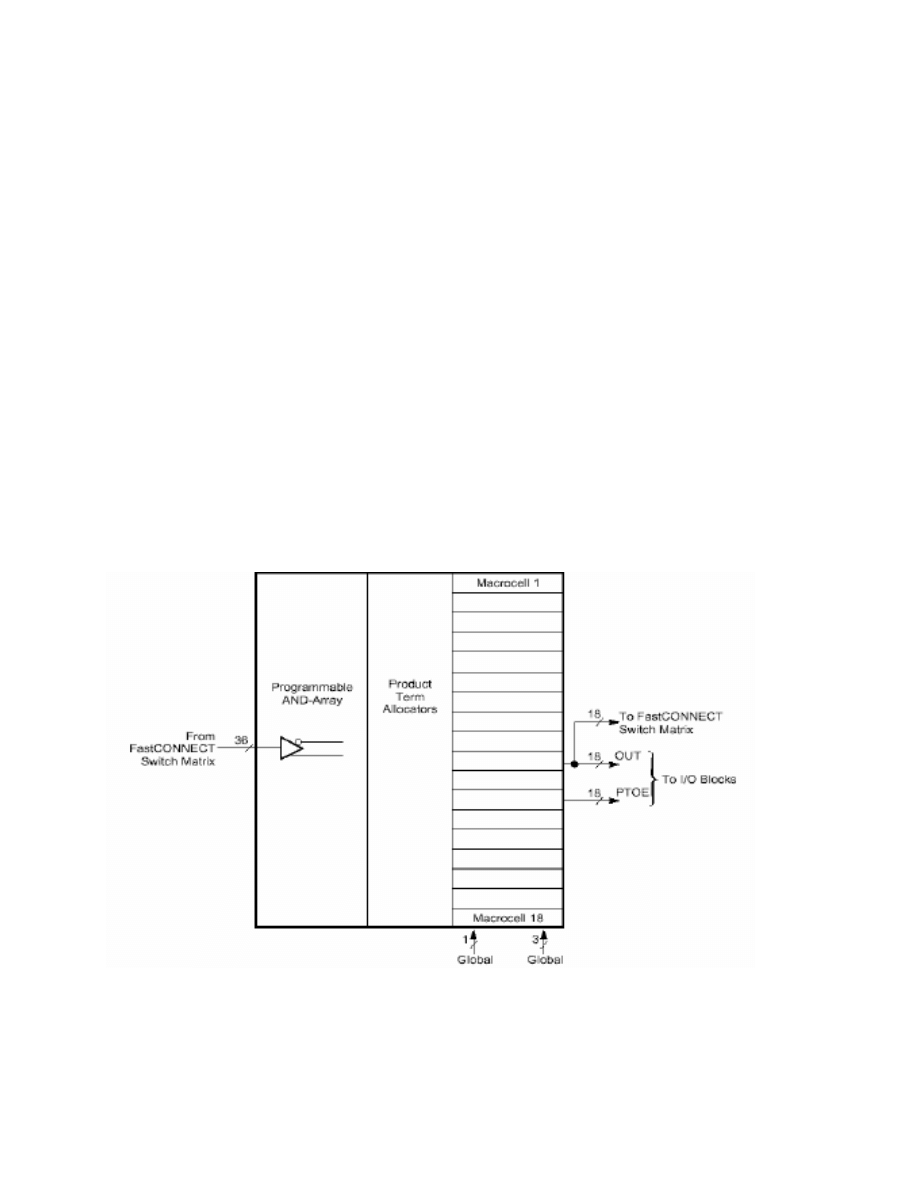

zawieraj cym bloki funkcyjne (FB – Function Block) i bloki wej cia/wyj cia (IOB – I/O

Block), które s

czone mi dzy sob za pomoc matrycy prze czaj cej (FastCONNECT

switch matrix) (rys. 4.8).

Bloki IOB mi dzy innymi buforuj sygna y wej ciowe i wyj ciowe z uk adu oraz zapewniaj

odpowiednie parametry elektryczne zacisków.

Ka dy blok funkcyjny FB daje mo liwo

zaprogramowania 36 wej

i 18 wyj . Matryca

prze czaj ca czy wszystkie wyj cia bloku FB z wej ciami innego bloku FB. Dla ka dego

bloku FB wyj cia w liczbie od 12 do 18 (w zale no ci od liczby wyprowadze obudowy)

skojarzone z sygna ami output enable steruj bezpo rednio blokami IOB.

Blok funkcyjny (FB) uk adów rodziny XC9500

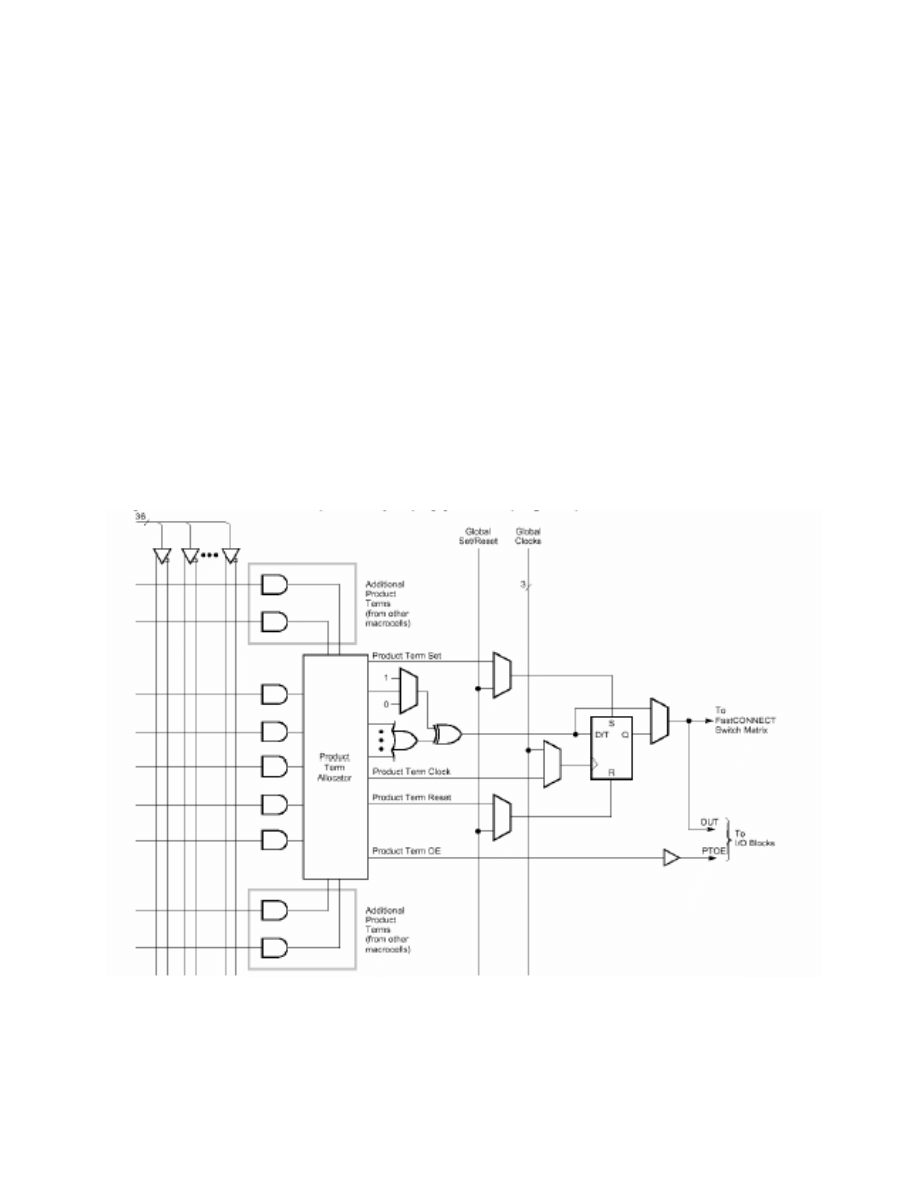

Ka dy blok funkcyjny, jak przedstawiono na rys. 4.9, sk ada si

z 18 niezale nych

makrokomórek, z których ka da mo e realizowa funkcj kombinacyjn b d rejestrow . Do

bloku funkcyjnego doprowadzony jest sygna zegara oraz sygna y set/reset. Blok funkcyjny

poprzez generacj stanów na 18 wyj ciach steruje matryc prze czaj c . Wyj cia te wraz z

sygna ami output enable steruj blokami IOB.

Do programowalnej matrycy iloczynów logicznych dochodz

72 sygna y (36 normalnych

sygna ów i 36 ich negacji). Sygna y te s

przez ni

czone do 90 linii product term

dochodz cych do 18 makrokomórek. Wewn trz ka dego bloku FB mo liwe jest zrealizowanie

po cze ( cie ek) z wyj

makrokomórek do matrycy iloczynów logicznych, bez potrzeby

wyprowadzania ich poza dany blok FB. cie ki te wykorzystywane s do tworzenia bardzo

szybkich liczników oraz uk adów stanów, gdzie wszystkie rejestry stanu s wewn trz tego

samego bloku FB.

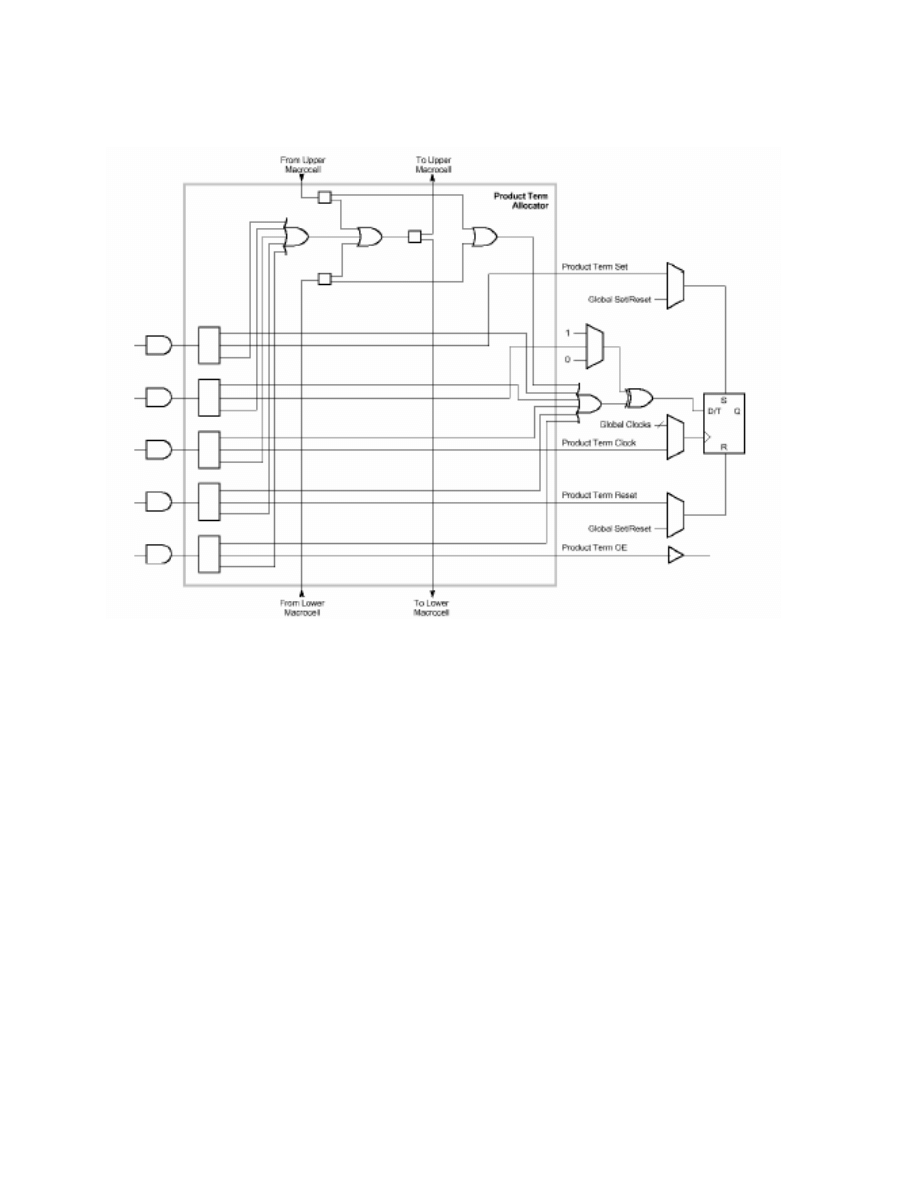

Ka da makrokomórka w bloku FB uk adu XC9500 mo e by indywidualnie skonfigurowana

tak, aby realizowa

funkcje kombinacyjne lub rejestrowe. Rys. poniMej przedstawia

makrokomórk i towarzysz ca jej struktur logiczn bloku FB.

Makrokomórka bloku FB uk adów rodziny XC9500

Pi ciu linii product terms bezpo rednio wyprowadzonych z matrycy iloczynów logicznych

mo na u y jako podstawowych wej danych (do bramek OR i XOR). Pozwalaj one na

implementacj funkcji kombinacyjnej lub mog pos u y jako wej cia steruj ce w czaj c w to

sygna y zegara, set/reset i output enable. Blok PTA (Product Term Allocator), zawarty w ka dej

makrokomórce, s u y do wyboru sposobu u ycia tych pi ciu linii. Rejestr makrokomórki mo e

by skonfigurowany jako przerzutnik D lub T, lub te mo e by przeznaczony do operacji

kombinacyjnych. Ka dy rejestr wyposa ony jest w dwie asynchroniczne operacje ustawiania

(set) i zerowania (reset). Podczas w czania zasilania wszystkie wykorzystywane rejestry s

inicjalizowane do stanu zdefiniowanego przez u ytkownika (w przypadku braku specyfikacji

domy lnie ustawiane jest 0). Wszystkie globalne sygna y takie jak sygna y zegara, set/reset oraz

output enable s dost pne dla ka dej makrokomórki. Sygna zegarowy dochodz cy do rejestru

mikrokomórki mo e by jednym z trzech globalnych sygna ów zegara lub sygna em zegara

pochodz cym z linii product term. Dodatkowo istnieje mo liwo

wyboru aktywnego zbocza

sygna u zegarowego. Poprzez wej cie GSR mo liwe jest ustawienie rejestru u ytkownika do

zdefiniowanego przez niego stanu.

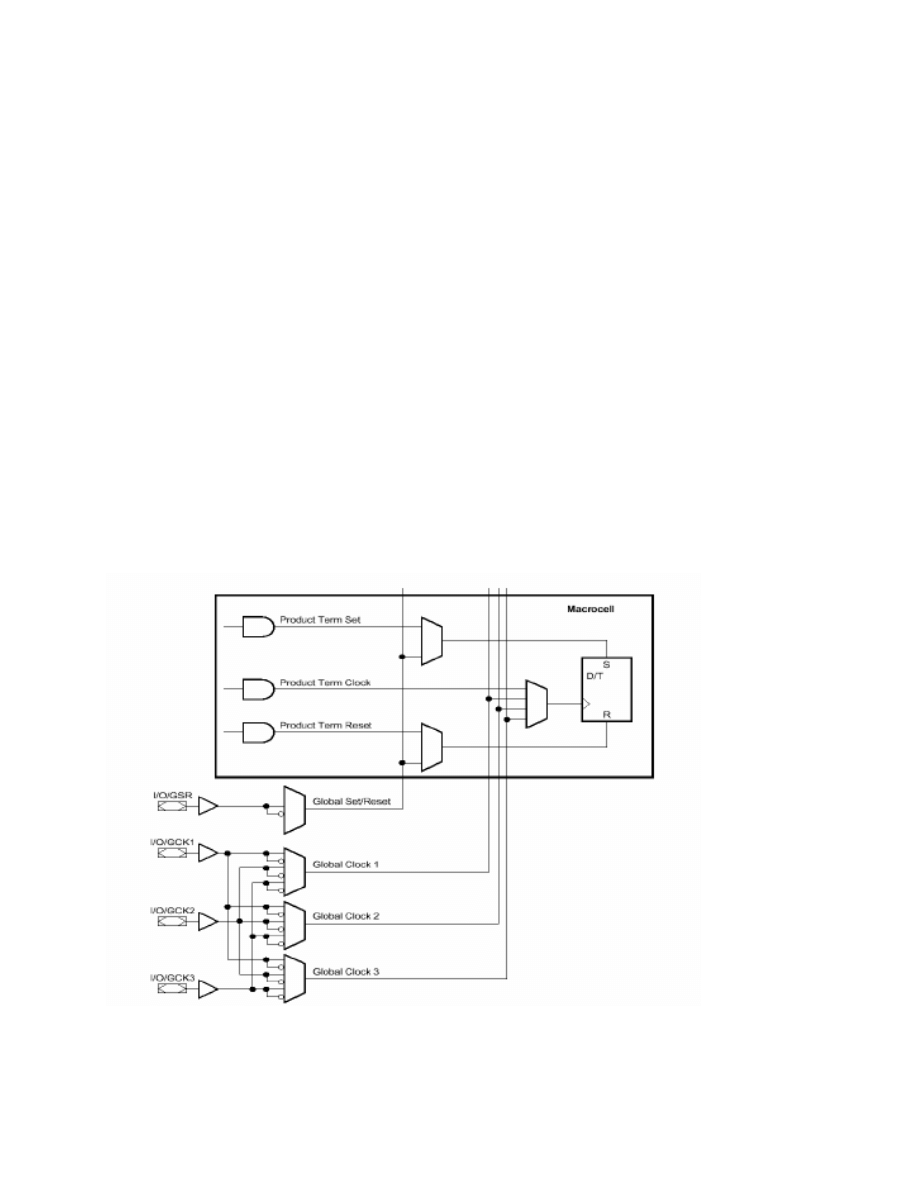

Sposób wyboru sygna ów zegarowych set/reset w makrokomórce bloku FB uk adów rodziny

XC9500

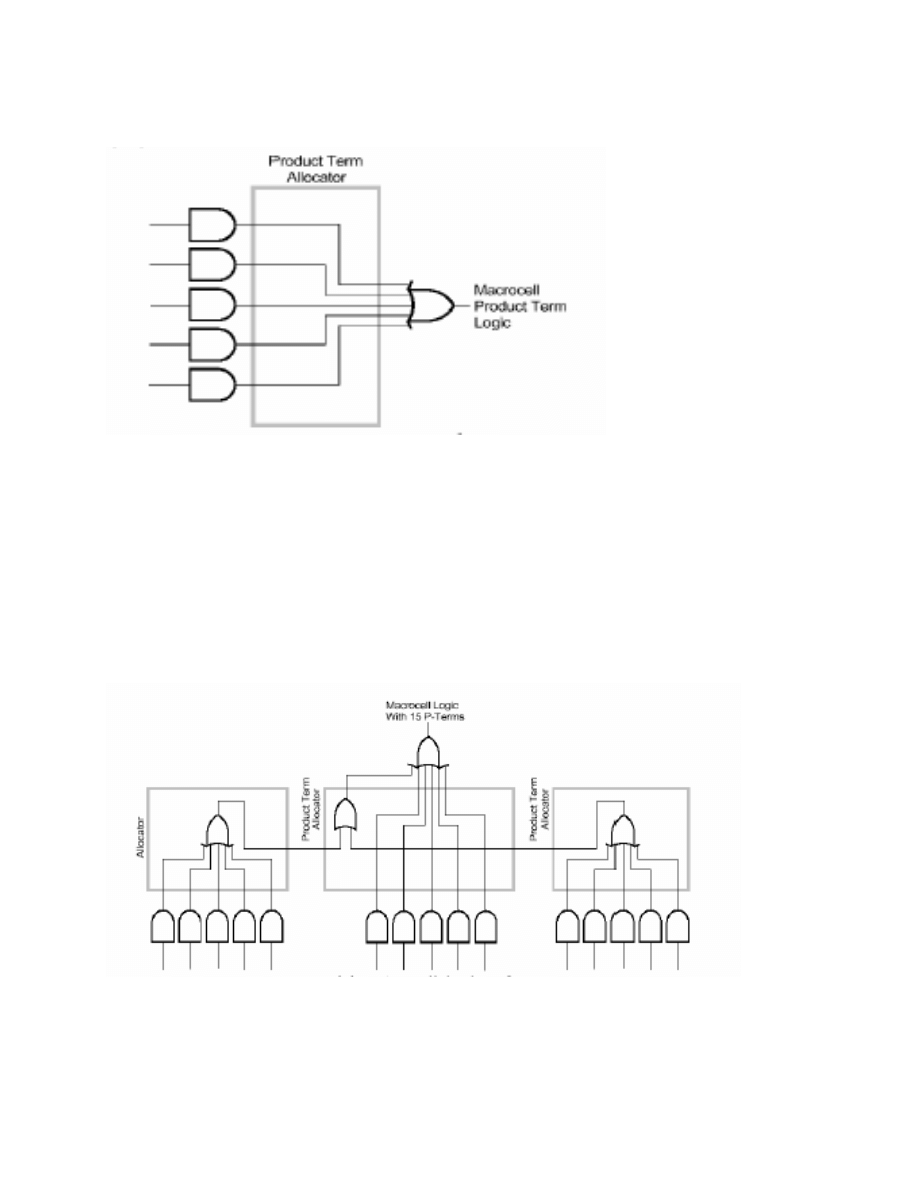

Blok PTA makrokomórki steruje wykorzystaniem pi ciu bezpo rednich linii product terms

dochodz cych do niej. Np. wszystkie pi linii mo e by do czonych do bramki OR.

Wykorzystanie bezpo rednich linii product terms w makrokomórce

Blok PTA mo e dokonywa zmian wewn trz FB i przydziela makrokomórce dodatkowe linie,

oprócz pi ciu podstawowych dochodz cych ju do niej. Ka da mikrokomórka wymagaj ca

dodatkowej linii product term mo e skorzysta z niewykorzystanej linii innej makrokomórki

wewn trz bloku FB. Pojedyncza makrokomórka mo e u y 15 linii produkt terms, przy czym

nale y uwzgl dni

dodatkowe opó nienia sygna ów na dodanych liniach, wynikaj ce z

wyd u enia si ich drogi wewn trz bloku FB.

Blok PTA z 15 liniami product terms

Elastyczno

ta wynika z budowy bloku PTA pokazanej na rys. poniMej.

Schemat logiczny bloku PTA

Matryca prze czaj ca dostarcza sygna y z bloków IOB i FB do wej

bloków FB. Wszystkie

wyj cia bloków FB i wej cia/wyj cia bloków IOB s podawane na t matryc . Za pomoc

matrycy u ytkownik wybiera sygna y, które maj dochodzi do danego bloku FB. Dodatkowo

realizuje ona iloczyn logiczny na drucie co zwi ksza funkcjonalno

ca ego uk adu.

Schemat logiczny matrycy prze czaj cej (FastCONNECT Switch Matrix)

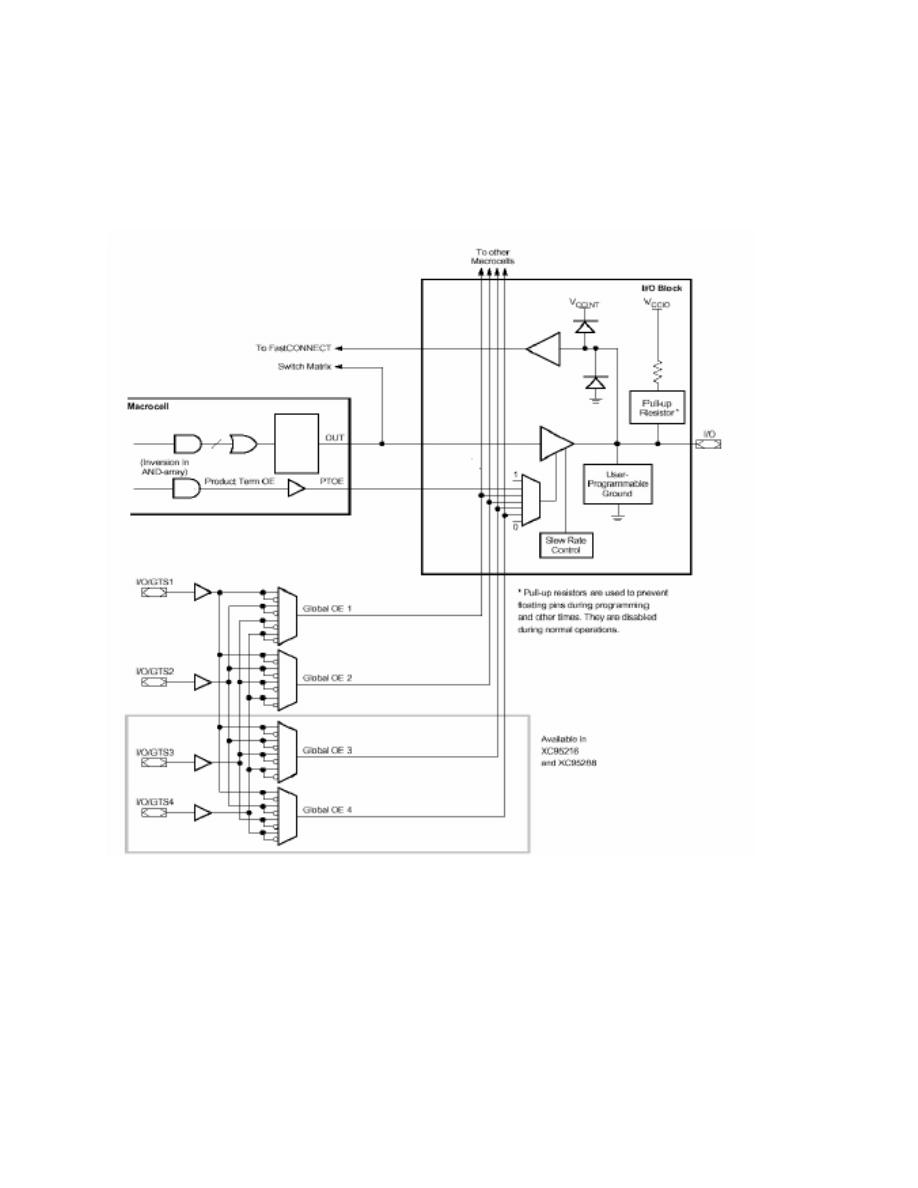

Bloki wej cia/wyj cia IOB stanowi

interfejs pomi dzy wewn trzn

logik , a pinami

wej cia/wyj cia uk adu. Ka dy blok zawiera bufor wej ciowy, sterownik wyj ciowy,

multiplekser wyboru output enable oraz programowalne uziemienie. Bufor wej ciowy jest

kompatybilny ze standardami 5V CMOS, 5V TTL i poziomami sygna u 3,3V. Bufor wej ciowy

u ywa wewn trznego 5V ród a zasilania (V

CCINT

) w celu zapewnienia sta ych progów wej cia i

eliminacji waha napi cia V

CCIO

. Sygna output enable mo e by generowany w nast puj cy

sposób, jako: sygna product term z makrokomórki, dowolny sygna zegara globalnego, zawsze

„1” lub zawsze „0”. Wyst puj

dwa globalne sygna y output enable dla uk adów do 144

makrokomórek oraz cztery sygna y globalne output enable dla uk adów z 180 lub wi ksz liczb

makrokomórek. Ka de wyj cie umo liwia kontrol szybko ci narastania napi cia wyj ciowego.

Szybko

narastania sygna u wyj ciowego mo e by programowo spowalniana w celu redukcji

szumów. Ka dy blok IOB zapewnia programow

obs ug pinu uziemienia. Pozwala to na

dodatkow konfiguracj pinów uk adów wej cia/wyj cia jako pinów uziemienia. Dzi ki temu

mo na znacznie zredukowa poziom szumów. Rezystory podci gaj ce (typowa warto

10k

.

)

s

do czone do ka dego uk adu wej cia/wyj cia w celu zabezpieczenia go przed stanem

nieokre lonym, w przypadku niewykorzystania tego uk adu przez projekt u ytkownika.

Rezystory te s aktywne w trybie programowania oraz kasowania uk adu, a tak e w momencie

w czania zasilania systemu.

Schemat logiczny bloku IOB wraz z uk adami steruj cymi sygna ami output enable

Rezystory s de aktywowane podczas normalnych operacji. Sterownik wyj ciowy jest zdolny do

przewodzenia pr du 24mA. Wszystkie sterowniki wyj ciowe w uk adzie mog

by

skonfigurowane dla poziomu 5V lub poziomu 3,3V przez po czenie wyj ciowego pinu zasilania

(VCCIO) do 5V lub do ród a zasilania 3,3V. Rys. 4.17 pokazuje jak uk ad XC9500 mo e by

zasilany tylko napi ciem 5V lub napi ciem 5V i 3,3V.

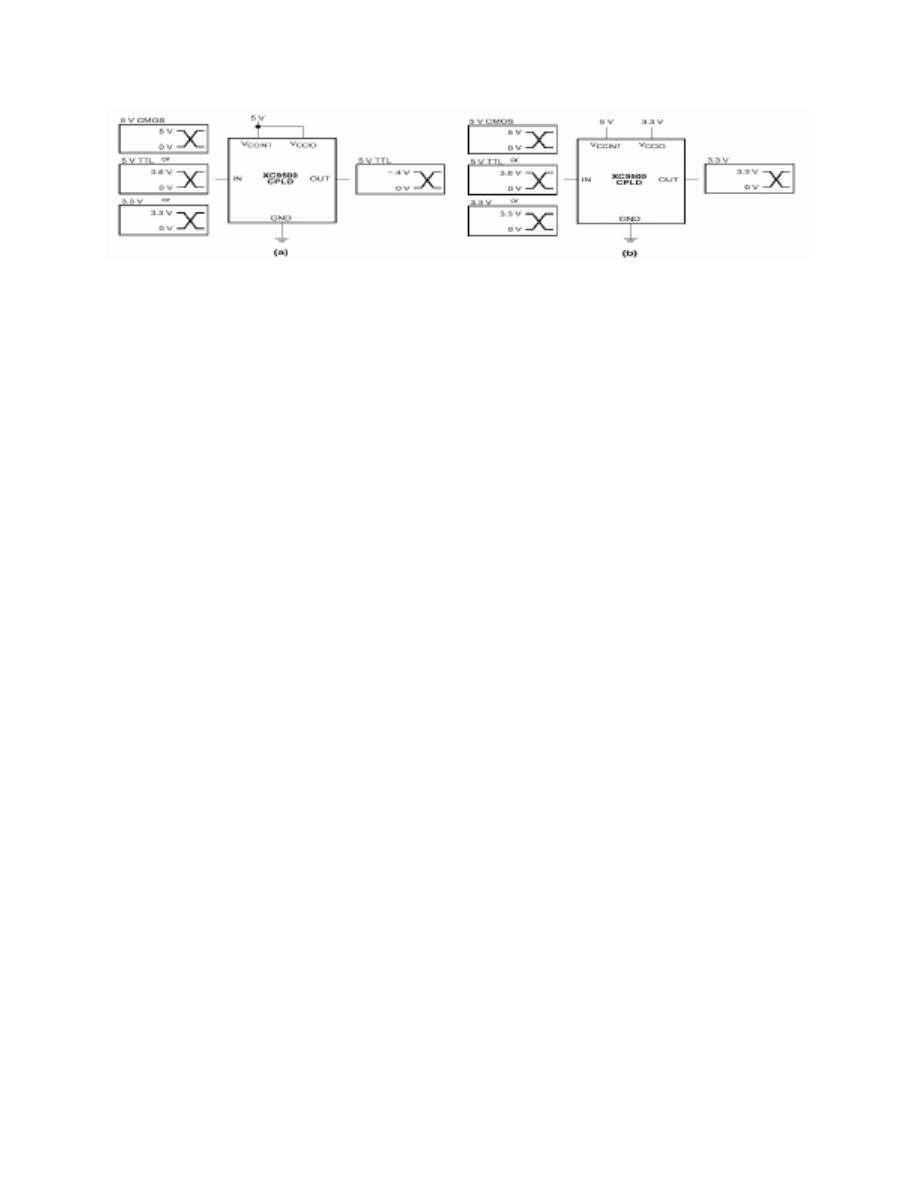

Sposoby zasilania uk adu rodziny XC9500:

a) jedno ród o zasilania 5V,

b)dwa ród a zasilania 5V i 3,3V

Programowanie i testowanie uk adów rodziny XC9500 jest realizowane za pomoc interfejsu

standardu IEEE 1149.1 (JTAG). Interfejs ten posiada nast puj c list instrukcji: EXTES,

SAMPLE/PRELOAD, BYPASS, USER-CODE, INTEST, IDCODE, HIGHZ.

Dodatkowo na potrzeby programowania uk adów w systemie (ISP) dodano 5 instrukcji: ISPEN,

FERASE, FPGM, FVFY, ISPEX. Stanowi one rozszerzenie zestawu instrukcji 1149.1. Zgodnie

ze specyfikacj

standardu IEEE 1149.1 piny TMS i TCK uk adu interfejsu JTAG s

podwieszone poprzez rezystory pull-up do zasilania.

Uk ady XC9500 zawieraj

zaawansowane sposoby ochrony danych, które ca kowicie

zabezpieczaj program przed nieautoryzowanym czytaniem lub pomy kowym skasowaniem, czy

przeprogramowaniem. U ytkownik mo e ustawi

odpowiednie bity w celu ochrony kodu

programu zawartego w uk adzie przed jego przeczytaniem. Skasowanie w ca o ci programu jest

jedynym sposobem na wyzerowanie bitów zabezpieczaj cych, tym samym na odblokowanie

odczytu z uk adu.

Wszystkie uk ady XC9500 oferuj

mo liwo

ustawienia trybu niskiego poboru mocy dla

ka dej makrokomórki z osobna lub dla wszystkich jednocze nie. Zatem wa ne dla danej

aplikacji cz ci uk adu mog pozosta w standardowym trybie poboru mocy, podczas gdy

pozosta e mog zosta zaprogramowane na operacje przy niskim poborze mocy.

W czasie w czania zasilania (power-up time) uk ady XC9500 s w stanie u pienia dopóki

napi cie zasilaj ce V

CCINT

nie osi gnie bezpiecznego poziomu (oko o 3,8 V). Do tego czasu

wszystkie piny uk adu oraz interfejsu JTAG s wy czone i podwieszone do zasilania za pomoc

rezystorów pull-up. Kiedy napi cie zasilania osi gnie bezpieczny poziom wszystkie rejestry

u ytkownika s inicjalizowane (typowo w czasie 100Ns dla 9536 - 95144, 200Ns dla 95216,

300Ns dla 95288) po czym uk ad jest gotowy do pracy.

Wyszukiwarka

Podobne podstrony:

sprawozdanie układy logiczne ćw 4

SYNTEZEAUTOMATU, ☆☆♠ Nauka dla Wszystkich Prawdziwych ∑ ξ ζ ω ∏ √¼½¾haslo nauka, Logika, układy LOGI

układy logiczne, ptul2, Tablice Karnaugha

Układy logiczne

Elementarne uklady logiczne

Układy logiczne cz.2, Laboratorium układów elektronicznych

Elektronika- Układy logiczne cz.1- dekodery, trans-latory.DOC, Wydz. E i A Grupa

Elektronika- Układy logiczne cz.1- dekodery, trans-latory.DOC, Wydz. E i A Grupa

Kombinacyjne uklady logiczne

UKŁADY LOGICZNE

11 PEiM Układy logiczne doc (2)

07 Podstawowe uklady logiczne (2)

Układy logiczne cz.1, Laboratorium układów elektronicznych

więcej podobnych podstron