Laboratorium Podstaw Elektroniki Instytutu Fizyki PŁ

1

wiczenie EL1

Elementy logiczne

Przed zapoznaniem si z instrukcj i przyst pieniem do wykonywania wiczenia nale y opanowa

nast puj cy materiał teoretyczny:

1.

Reprezentacja stanów logicznych 0 i 1 w najpopularniejszych typach układów logicznych TTL i CMOS.

[1-3,6]

2.

Opis wła ciwo ci statycznych bramek logicznych. Najwa niejsze charakterystyki i parametry bramek. [1-4]

3.

Co to jest margines zakłóce ? [1,2,6]

4.

Symbole graficzne funktorów realizuj cych podstawowe funkcje logiczne AND, OR, NOT, NAND, NOR,

EX-OR i EX-NOR oraz funktora wzmacniaj cego. [1-5]

5.

Porównanie konstrukcji bramek NAND zrealizowanych w technice TTL i CMOS. [1-5]

6.

Dopasowanie linii długich do przenoszenia sygnałów cyfrowych. [5]

Cel wiczenia

Celem wiczenia jest:

1. Zbadanie statycznych charakterystyk wej ciowych, przej ciowych i wyj ciowych bramki logicznej.

2. Jako ciowe zapoznanie si ze zniekształceniami impulsów w liniach długich przy niedopasowanej rezystancji

falowej linii i ródła sygnału.

Metoda pomiaru

Na stanowisku pomiarowym badana jest pojedyncza bramka logiczna wykonana w technice TTL realizuj ca

funkcj NOT. Badanie charakterystyk statycznych bramki metod „punkt po punkcie” odbywa si przy u yciu

multimetrów oraz nast puj cych zespołów zamkni tych razem z badan bramk w module pomiarowym:

a) dzielnik napi ciowy zbudowany na potencjometrze P

1

pozwalaj cy na sterowanie wej cia bramki napi ciami

regulowanymi w zakresie od 0 do 5V,

b) rezystancyjne obci enie, umo liwiaj ce regulacj potencjometrem P

2

pr dów wyj ciowych bramki w zakresie

od 0 do warto ci około 15 mA zbli onej do katalogowego maksymalnego ci głego pr du wyj ciowego,

c) alternatywne obci enie wyj cia badanej bramki w postaci wej kolejnych bramek w liczbie wybieranej od 1

do 12.

Zadawanie ró nych warto ci napi cia wej ciowego U

we

i pomiar nat enia wej ciowego pr du I

we

umo liwia

wyznaczenie charakterystyki wej ciowej bramki I

we

= f(U

we

). Z kolei zadawanie ró nych warto ci U

we

i pomiar

napi cia na wyj ciu bramki U

wy

umo liwia wyznaczenie rodziny charakterystyk przej ciowych U

wy

= f(U

we

) bramki

przy ró nych obci eniach. Ponadto pomiar napi cia U

wy

i pr du wyj ciowego I

wy

przy zmianach obci enia bramki

pozwala na wyznaczenie charakterystyk wyj ciowych I

wy

= f(U

wy

).

Poniewa bramki o małej liczbie wej s umieszczane po kilka sztuk w jednym układzie scalonym,

zastosowano układ UCY 7430 zawieraj cy jedn 8-io wej ciow bramk NAND. Dzi ki temu pomiar pr du

zasilania I

z

badanej bramki nie jest zaburzany przez inne bramki. Na panelu czołowym modułu pomiarowego

wyprowadzono tylko jedno z wej bramki NAND, podczas gdy pozostałe znajduj si zawsze w stanie wysokim.

Gdy czas przej cia sygnału przez przewód zbli a si do czasu narastania impulsu, w przewodzie nast puj

zniekształcenia impulsów, odbicia i drgania tłumione. Zjawiska te mo na ograniczy przez dopasowanie rezystancji

falowej ródła sygnału, przewodu i odbiornika. Na stanowisku pomiarowym wyj cia generatora, przewody

koncentryczne i wej cia oscyloskopu maj dopasowan rezystancj falow 50

Ω. Do sterowania długich odcinków

przewodów produkuje si specjalne układy scalone zwane sterownikami linii, jednak e badana bramka nie jest

przeznaczona do takich zastosowa lecz do sterowania wej kolejnych bramek. W przypadku podł czenia do jej

wyj cia przewodu koncentrycznego o długo ci około 1 m wyst puj silne zniekształcenia sygnału, które s innego

rodzaju przy przej ciu ze stanu logicznego wysokiego do niskiego a inne przy przej ciu odwrotnym - wynika to ze

zmian rezystancji wyj ciowej bramki, która w stanie niskim jest bardzo mała, natomiast w stanie wysokim jest du o

wi ksza od rezystancji falowej przewodu 50

Ω. Zniekształcenia badane s na stanowisku pomiarowym tylko

w sposób jako ciowy przez porównanie oscylogramów na oscyloskopie poł czonym przewodem najpierw

bezpo rednio z generatorem a nast pnie za po rednictwem badanej bramki.

Laboratorium Podstaw Elektroniki Instytutu Fizyki PŁ

2

Kolejno czynno ci

A. Charakterystyka wej ciowa bramki logicznej (wersja podstawowa)

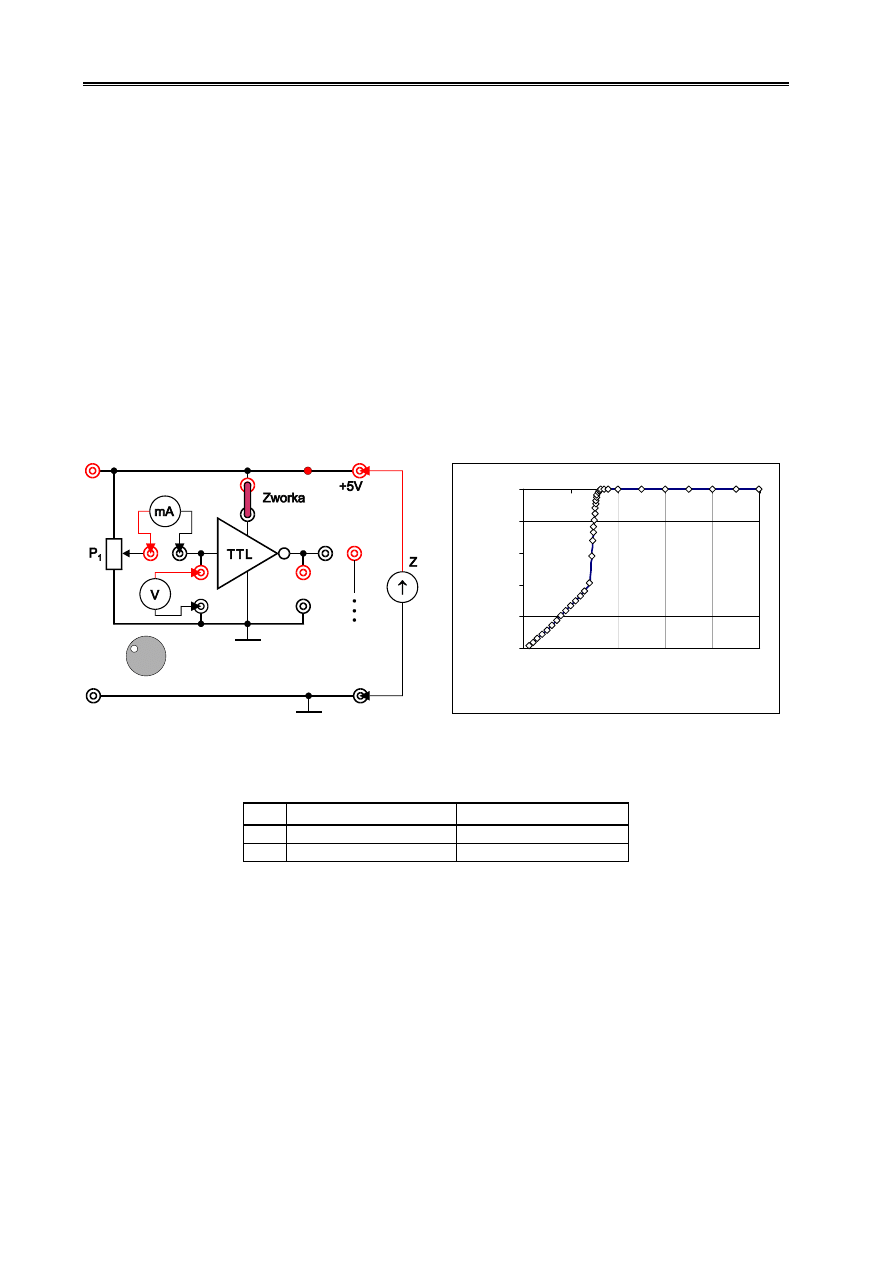

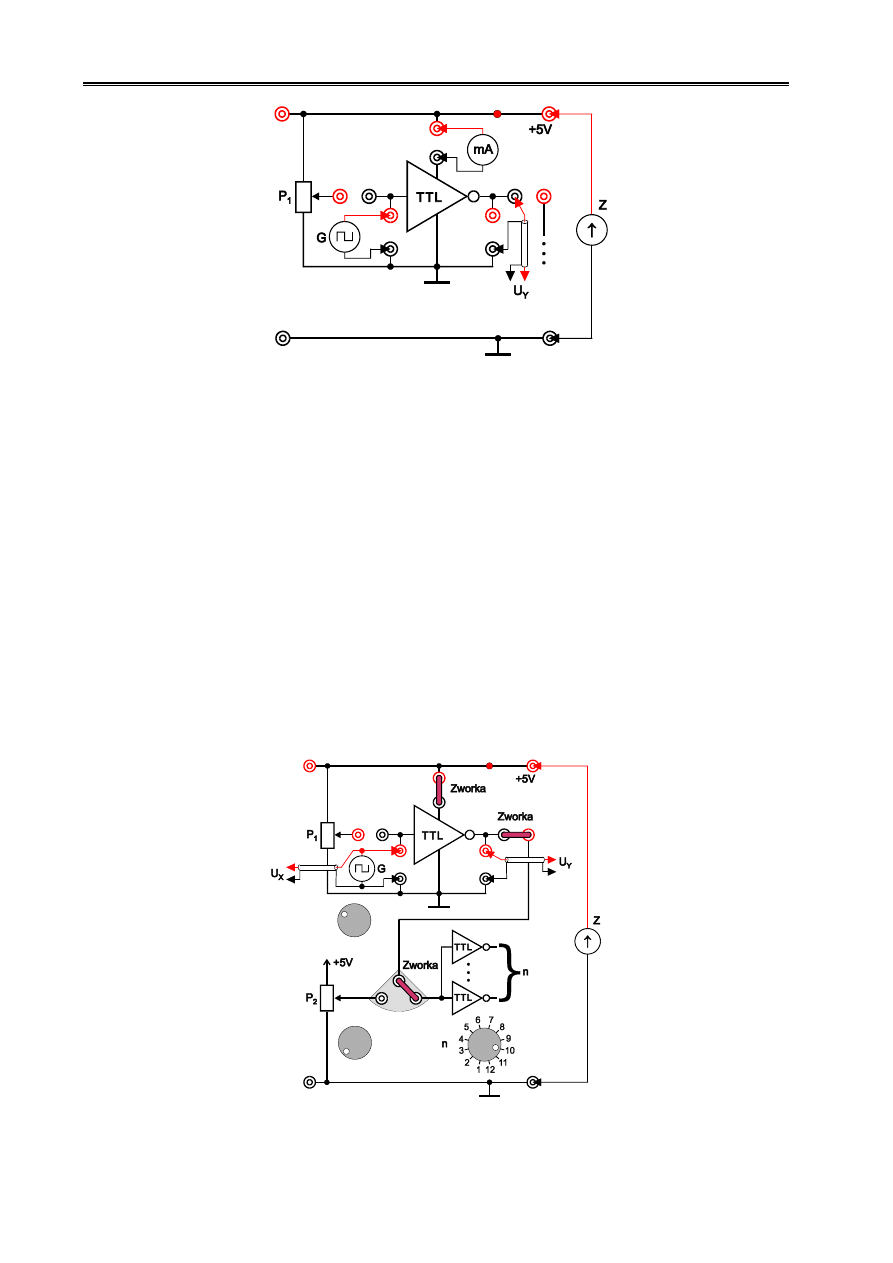

1. Podł czy Zasilacz (Z - DF1731SB3A), miliamperomierz (mA), woltomierz (V) oraz Zworki z modułem

zawieraj cym badan bramk logiczn jak na rys. 1.

UWAGA:

a) moduł pomiarowy powinien by zasilany z wyj cia zasilacza zapewniaj cego stałe napi cie +5V

(gniazda z prawej strony zasilacza). Nie u ywa wyj umo liwiaj cych płynn zmian napi cia,

b) nie wolno ł czy linii zasilania +5V i masy z gniazdami nie nale cymi na schemacie do tych linii.

Nieprzestrzeganie powy szych zalece grozi uszkodzeniem urz dze .

2. Na miliamperomierzu (pomiar I

we

) ustawi zakres pomiarowy do 2 mA.

3. Na woltomierzu (pomiar U

we

) ustawi zakres pomiarowy do 20 V.

4. Po uzyskaniu zezwolenia od opiekuna wł czy multimetry oraz zasilacz. Po zał czeniu zasilania sprawdzi

czy wieci si czerwona dioda umieszczona w module pomiarowym na linii +5V.

5. Zmieniaj c potencjometrem P

1

napi cie wej ciowe bramki U

we

w zakresie od 0 do 5V wyznaczy zale no

pr du wej ciowego I

we

od U

we

. Dla napi U

we

wynosz cych około 1,3…1,6 V nale y zwróci uwag na

zmniejszenie kroku pomiarowego, poniewa w tym obszarze dochodzi do znacznych zmian pr du I

we

na

skutek niewielkich przyrostów U

we

. Wyniki pomiarów zapisa w Tabeli 1.

Rys. 1. Schemat układu do wyznaczania charakterystyki

wej ciowej bramki logicznej.

-1,0

-0,8

-0,6

-0,4

-0,2

0,0

0

1

2

3

4

5

U

we

[V]

I

w

e

[m

A

]

Rys. 2. Przykładowa charakterystyka wej ciowa

bramki logicznej wykonanej w technice TTL.

Lp.

U

we

[V]

I

we

[mA]

Tabela 1. Tabela pomiarów dla charakterystyki wej ciowej bramki logicznej.

B. Charakterystyka przej ciowa i moc rozpraszana przez bramk logiczn (wersja podstawowa)

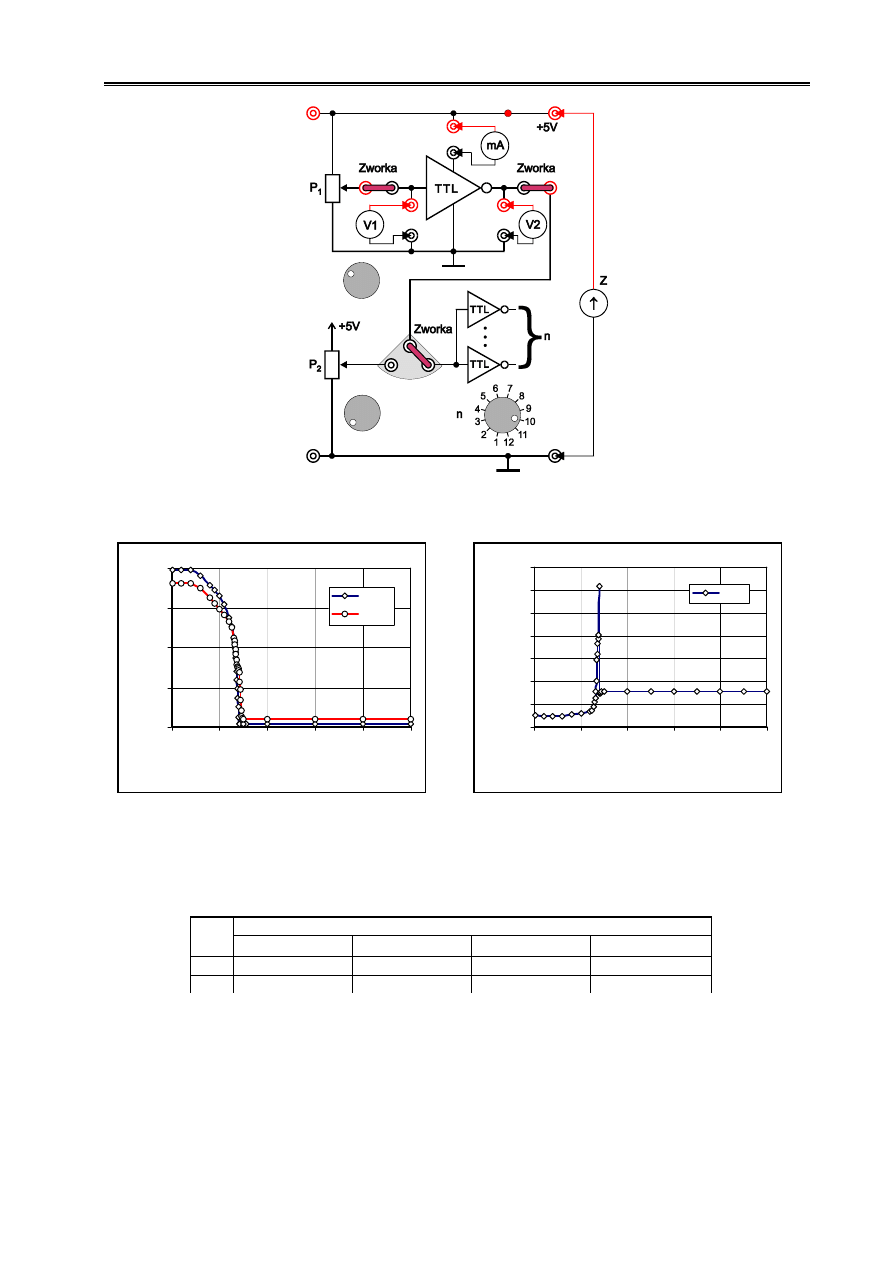

1. Poł czy układ przedstawiony na rys. 3. Miliamperomierz (mA) ustawi na pomiar pr dów stałych na zakresie

200 mA, natomiast woltomierze (V1) i (V2) na zakres do 20V.

2. Przeł cznikiem n wybra obci enie wyj cia badanej bramki np. przez n = 10 wej kolejnych bramek o ile

prowadz cy zaj cia nie zaleci innej warto ci n.

3. Zmieniaj c potencjometrem P

1

napi cie wej ciowe bramki U

we

w zakresie od 0 do 5V wyznaczy zale no

napi cia wyj ciowego U

wy

i pr du zasilania I

z

od U

we

. Dla napi U

we

wynosz cych około 1,2…1,5 V nale y

zwróci uwag na zag szczenie pomiarów w zwi zku z gwałtownymi zmianami U

wy

i I

z

na skutek niewielkich

przyrostów U

we

. Wyniki pomiarów zapisa w Tabeli 2.

Laboratorium Podstaw Elektroniki Instytutu Fizyki PŁ

3

Rys. 3. Schemat układu do wyznaczania charakterystyk przej ciowych i pr du zasilania bramki logicznej.

0

1

2

3

4

0

1

2

3

4

5

U

we

[V]

U

w

y

[V

]

n = 0

n = 12

Rys. 4. Przykładowa rodzina charakterystyk

przej ciowych bramki logicznej wykonanej w technice

TTL.

0

10

20

30

40

50

60

70

0

1

2

3

4

5

U

we

[V]

P

z

[m

W

]

n = 0

Rys. 5. Przykładowa charakterystyka mocy rozpraszanej

przez bramk logiczn wykonan w technice TTL.

n = …

Lp.

U

we

[V]

U

wy

[V]

I

z

[mA]

P

z

[mW]

Tabela 2. Tabela pomiarów dla charakterystyki przej ciowej bramki logicznej i rozpraszanej mocy.

Laboratorium Podstaw Elektroniki Instytutu Fizyki PŁ

4

C. Charakterystyka wyj ciowa bramki logicznej (wersja podstawowa)

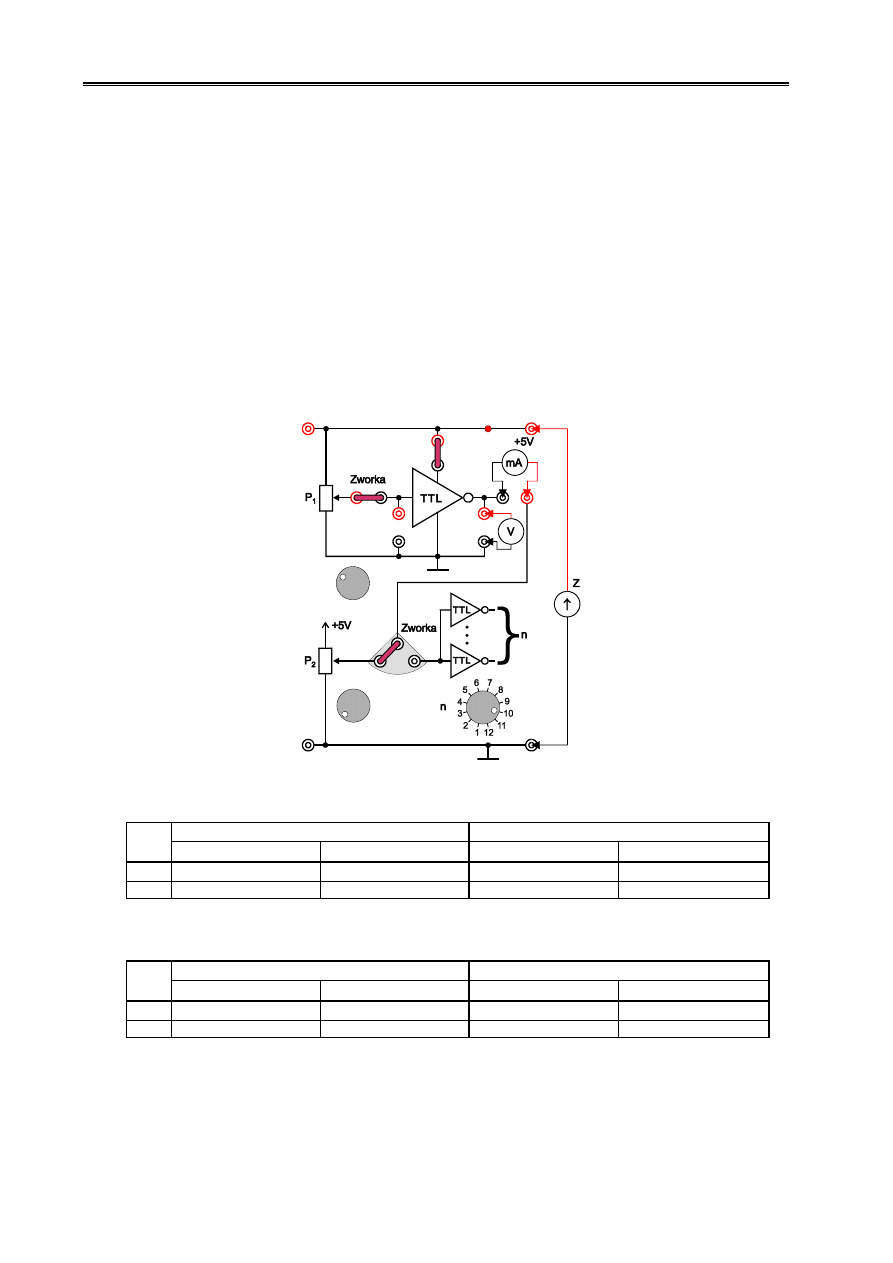

1. Podł czy obwód zgodnie ze schematem przedstawionym na rys. 6. Miliamperomierz (mA) ustawi na pomiar

pr dów stałych na zakresie 200 mA, natomiast woltomierz (V) na zakres do 20V.

2. Zada stan niski na wej ciu bramki ustawiaj c gałk potencjometru P

1

w skrajne lewe poło enie.

3. Zmieniaj c potencjometrem P

2

pr d wyj ciowy I

wyH

z pewnym ustalonym krokiem (np. 1 mA) w całym

dost pnym zakresie (od 0 do około 15 mA) wyznaczy zale no napi cia wyj ciowego U

wyH

od I

wyH

odpowiadaj c stanowi wysokiemu na wyj ciu bramki. Wyniki pomiarów zapisa w Tabeli 3.

4. Zada stan wysoki na wej ciu bramki ustawiaj c gałk potencjometru P

1

w skrajne prawe poło enie

i powtórzy pomiary z punktu 3 wyznaczaj c U

wyL

i I

wyL

odpowiadaj ce stanowi niskiemu na wyj ciu bramki.

5. Zamiast rezystancyjnego obci enia wyj cia bramki zastosowa teraz obci enie wej ciami kolejnych bramek.

W tym celu najni ej poło on zwork nale y obróci o 90

o

wzgl dem sytuacji pokazanej na rys. 6.

6.

Zmieniaj c przeł cznikiem n liczb doł czonych wej bramek obci aj cych kolejno od 1 do 12 mierzy

napi cia wyj ciowe U

wyH

i pr d wyj ciowy I

wyH

odpowiadaj ce stanowi wysokiemu na wyj ciu bramki.

Dodatkowy pomiar dla n = 0 mo na wykona przez otwarcie zworki ł cz cej wyj cie badanej bramki

z obci eniem. Wyniki pomiarów zapisa w Tabeli 4.

7. Powtórzy pomiary z punktu 6 wyznaczaj c U

wyL

i I

wyL

odpowiadaj ce stanowi niskiemu na wyj ciu bramki.

Rys. 6. Schemat układu do wyznaczania charakterystyk wyj ciowych bramki logicznej przy obci eniu

rezystancyjnym.

stan wysoki

stan niski

Lp.

I

wyH

[mA]

U

wyH

[V]

I

wyL

[mA]

U

wyL

[V]

1

2

Tabela 3. Tabela pomiarów dla charakterystyk wyj ciowych bramki logicznej przy obci eniu rezystancyjnym.

stan wysoki

stan niski

n

I

wyH

[mA]

U

wyH

[V]

I

wyL

[mA]

U

wyL

[V]

0

1

Tabela 4. Tabela pomiarów dla charakterystyk wyj ciowych bramki logicznej przy obci eniu wej ciami

kolejnych bramek.

Laboratorium Podstaw Elektroniki Instytutu Fizyki PŁ

5

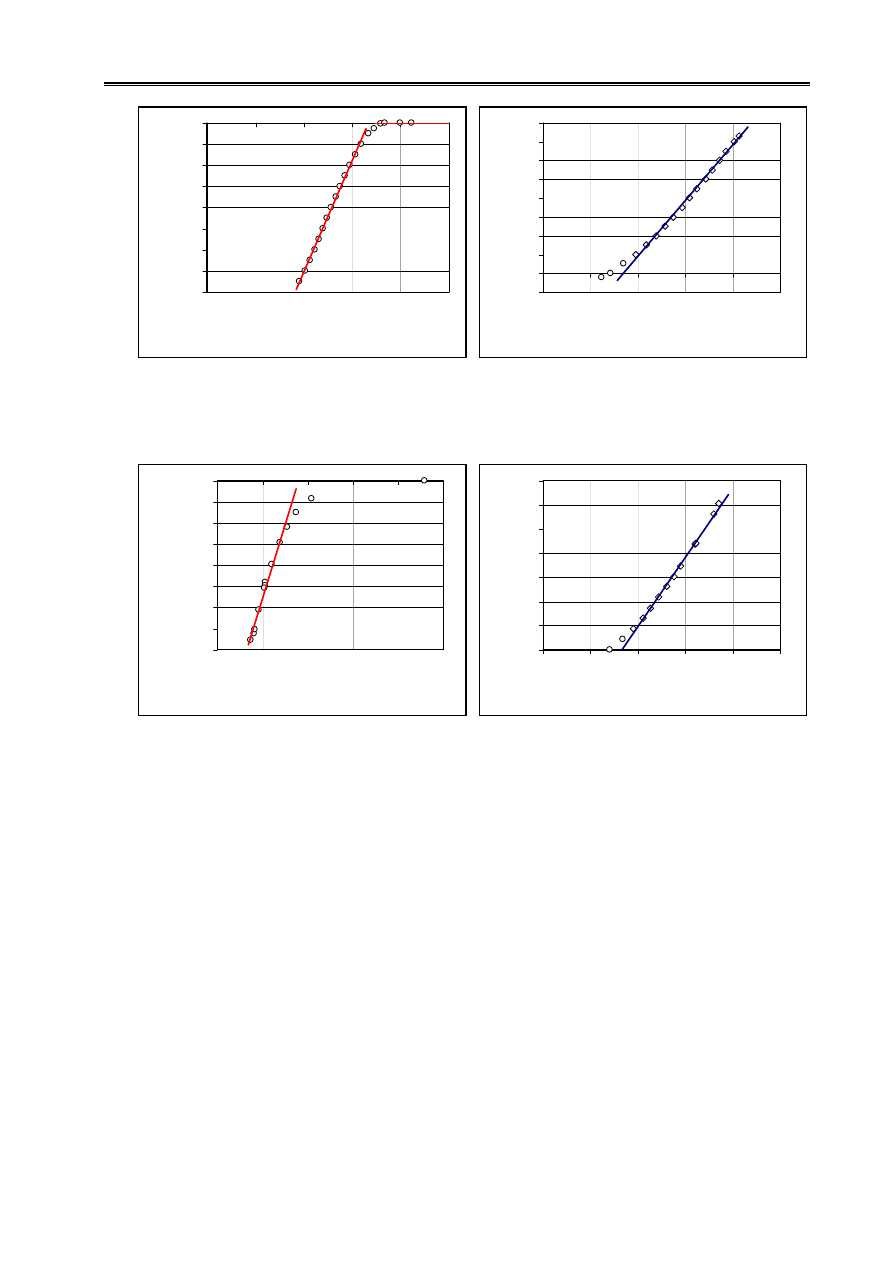

-16

-14

-12

-10

-8

-6

-4

-2

0

0

1

2

3

4

5

U

wyH

[V]

I

w

yH

[m

A

]

a)

-2

0

2

4

6

8

10

12

14

16

0,00

0,05

0,10

0,15

0,20

0,25

U

wyL

[V]

I

w

yL

[m

A

]

b)

Rys. 7. Przykładowe charakterystyki wyj ciowe bramki logicznej wykonanej w technice TTL przy obci eniu

rezystancyjnym.

a) stan wysoki na wyj ciu bramki, b) stan niski na wyj ciu bramki.

-0,08

-0,07

-0,06

-0,05

-0,04

-0,03

-0,02

-0,01

0,00

3,5

3,6

3,7

3,8

3,9

4,0

U

wyH

[V]

I

w

yH

[m

A

]

a)

0

2

4

6

8

10

12

14

0,00

0,05

0,10

0,15

0,20

0,25

U

wyL

[V]

I

w

yL

[m

A

]

b)

Rys. 8. Przykładowe charakterystyki wyj ciowe bramki logicznej wykonanej w technice TTL przy obci eniu

wej ciami kolejnych bramek.

a) stan wysoki na wyj ciu bramki, b) stan niski na wyj ciu bramki.

D. Obci enie wyj cia bramki lini dług (wersja rozszerzona)

1.

Poł czy oscyloskop bezpo rednio z wyj ciem cyfrowym generatora TTL/CMOS OUT i poci gn gałk

potencjometru PULL TO TTL CMOS LEVEL. Obracanie tej gałki a tak e gałek regulacji amplitudy,

składowej stałej i symetrii przebiegu nie ma adnego wpływu na sygnał na wyj ciu cyfrowym.

2.

Wł czy oscyloskop i generator. W generatorze ustawi maksymaln cz stotliwo (około 2,2 MHz).

3. Przerysowa oscylogram.

4. Wył czy generator, usun zworki w module pomiarowym, podł czy generator (G) i miliamperomierz (mA)

o zakresie 200 mA jak na rys. 9. Wyj cie bramki pozostawi na razie nieobci one.

5. Wł czy miliamperomierz i generator. Zanotowa pr d zasilania bramki bez obci ania jej wyj cia

przewodem koncentrycznym.

6. Poł czy wyj cie bramki z oscyloskopem jak na rys. 9. Zwróci uwag na nierównowa no dwóch gniazd

poł czonych z wyj ciem bramki, co nie zostało pokazane na schemacie - nie u ywa wyj cia przeznaczonego

we wcze niejszych układach do podł czenia woltomierza gdy nat enie pr du jest w nim ograniczone w celu

ochrony bramki przed omyłkowym podł czeniem multimetru pracuj cego jako amperomierz.

7. Zanotowa pr d zasilania bramki i przerysowa oscylogram.

8. Wył czy zasilanie i rozł czy poł czenia.

Laboratorium Podstaw Elektroniki Instytutu Fizyki PŁ

6

Rys. 9. Schemat układu do obserwacji zniekształce wnoszonych przez lini dług obci aj c wyj cie bramki.

E. Wizualizacja charakterystyki przej ciowej bramki logicznej (wersja rozszerzona)

1.

Podł czy generator (G), oscyloskop (U

X

i U

Y

) i zasilacz (Z) zgodnie ze schematem przedstawionym na

rys. 10. Zwróci uwag na to, by sygnał z generatora był pobierany z wyj cia uniwersalnego OUTPUT a nie

z wyj cia sygnału cyfrowego TTL/CMOS OUT. Za po rednictwem trójnika doprowadzi sygnał z generatora

jednocze nie do kanału CH1 w oscyloskopie i do wej cia badanej bramki.

2.

Ustawi w generatorze minimaln amplitud i wył czy tłumiki.

3.

Po uzyskaniu zezwolenia od opiekuna wł czy generator, oscyloskop i zasilacz.

4.

Wybra trójk tny kształt przebiegu oraz cz stotliwo rz du 1 kHz. Oscyloskop ustawi do pracy z kanałem

CH1. Wyzerowa sygnał na tym wej ciu przez ustawienie przeł cznika trybu pomiaru w pozycj GND

i przesun pionowo przebieg na ekranie odpowiadaj cy napi ciu 0V na wybran lini w dolnej cz ci ekranu.

Przeł czy kanał CH1 w tryb pomiaru DC. W generatorze wyci gn (lekko do przodu) gałk regulacji

składowej stałej PULL TO VAR DC OFFSET. Dobra amplitud sygnału i składow stał w generatorze tak,

by oscyloskop pokazał przebieg jednokierunkowy zmieniaj cy si pomi dzy 0 V a 5 V.

5.

Przeł czy oscyloskop w tryb pracy X-Y.

6.

Przeł cznikiem n zada obci enie wyj cia badanej bramki zgodne ze stosowanym wcze niej w rozdziale B.

Przerysowa przebieg z ekranu oscyloskopu, zanotowa wzmocnienia VOLTS/DIV.

7.

Powtórzy obserwacj dla innego obci enia bramki.

Rys. 10. Schemat układu do wizualizacji charakterystyki przej ciowej bramki logicznej.

Laboratorium Podstaw Elektroniki Instytutu Fizyki PŁ

7

Opracowanie sprawozdania

1.

Na podstawie uzyskanych wyników wykona wykres charakterystyki wej ciowej bramki I

we

= f

1

(U

we

).

Wykorzystuj c odczytan z wykresu maksymaln warto I

we max

i katalogow warto dopuszczalnego

ci głego pr du na wyj ciu bramki 16 mA sprawdzi czy maksymalna liczba bramek obci aj cych

(16 mA /I

we max

) przy pracy z nisk cz stotliwo ci przeł czania jest wi ksza od katalogowej warto ci 10

uwzgl dniaj cej rozrzut parametrów i wzrost rozpraszanej mocy przy wy szych cz stotliwo ciach.

2.

Wykona wykres charakterystyki przej ciowej U

wy

= f

2

(U

we

) dla wybranej liczby n bramek obci aj cych.

Znale w literaturze przedziały napi przyj te w technice TTL do reprezentowania stanu logicznego

niskiego (logiczne zero), wysokiego (logiczna jedynka) i nieokre lonego. Sprawdzi czy badana bramka

poprawnie odwzorowuje cały przedział napi odpowiadaj cych stanowi niskiemu na wej ciu w stan wysoki

na wyj ciu oraz przedział napi dla stanu wysokiego na wej ciu w stan niski na wyj ciu. Je li tak, obliczy

margines zakłóce statycznych (czyli trwaj cych długo w porównaniu do czasu propagacji sygnału przez

bramk ). Margines zakłóce statycznych dla stanu niskiego definiuje si jako ró nic U

IL

– f

2

(U

IH

), gdzie U

IL

jest progowym napi ciem rozgraniczaj cym stan niski od nieokre lonego, za U

IH

jest progowym napi ciem

mi dzy stanem wysokim i nieokre lonym. Margines zakłóce statycznych dla stanu wysokiego wynosi

f

2

(U

IL

) – U

IH

. Warto ci f

2

(U

IL

) i f

2

(U

IH

) odczytuje si z wykresu charakterystyki przej ciowej. Mniejszy z

dwóch znalezionych marginesów nale y uzna za ogólny margines zakłóce statycznych. Przy zakłóceniach

mniejszych od wielko tego marginesu gwarantowany jest poprawny stan logiczny na wej ciu kolejnej

bramki.

3.

Na podstawie warto ci pr du zasilania bramki I

z

obliczy rozpraszan moc P

z

= U

z

I

z

przyjmuj c napi cie

zasilania U

z

= 5 V. Wykona wykres mocy P

z

= f

3

(U

we

).

4.

Wykona wykresy charakterystyk wyj ciowych I

wy

= f

4

(U

wy

) w stanie niskim i wysokim dla obu typów

zastosowanych obci e bramki. Na podstawie wykresów stwierdzi , czy istnieje graniczne obci enie bramki

prowadz ce do nieokre lono ci stanu na wyj ciu bramki przy jednoznacznie okre lonym stanie na jej wej ciu.

5.

Na podstawie prostoliniowych odcinków charakterystyk wyj ciowych wykonanych w poprzednim punkcie

wyznaczy wyj ciowe rezystancje ró niczkowe

∂U

wy

/

∂I

wy

bramki w stanie niskim i wysokim. Rezystancje te

s odwrotno ciami współczynników kierunkowych odpowiednich prostych. Nie wyznacza rezystancji

ró niczkowych na podstawie przyrostów warto ci dla dwóch s siednich punktów pomiarowych, gdy tak

otrzymane przyrosty mog by obci one znacznym bł dem wzgl dnym.

6.

Je eli zbadano transmisj sygnału z wyj cia bramki przez lini dług nale y zinterpretowa oscylogramy

opieraj c si na porównaniu rezystancji falowej u ytego przewodu z rezystancjami wyj ciowymi bramki

wyznaczonymi w poprzednim punkcie.

7.

Porówna charakterystyk przej ciow bramki uzyskan metod oscyloskopow z charakterystyk wynikaj c

z pomiarów metod punkt po punkcie. Przedyskutowa uzyskane wyniki.

Literatura

[1] J. Kalisz, Podstawy elektroniki cyfrowej, WKiŁ, Warszawa 2002.

[2] W. Marciniak, Przyrz dy półprzewodnikowe i układy scalone. Zasady działania, technologia i zastosowania,

WNT, Warszawa 1979.

[3] P. Horowitz, W. Hill, Sztuka elektroniki, WKiŁ, Warszawa 2001,

[4] A. Rusek, Podstawy elektroniki, cz

2, Wydawnictwa Szkolne i Pedagogiczne, Warszawa, 1983.

[5] U. Tietze, Ch. Schenk, Układy półprzewodnikowe, WNT, Warszawa 1987.

[6] A. Charoy, Zakłócenia w urz dzeniach elektronicznych, tom 1, WNT, Warszawa 1999.

Wyszukiwarka

Podobne podstrony:

sprawozdanie el1

El1 M wnski

EL1

el1, Studia, sprawozdania, sprawozdania z układów elektronicznych

EL1

kl2 kartkówka el1

el1

El1 Dąbrowski doc

więcej podobnych podstron