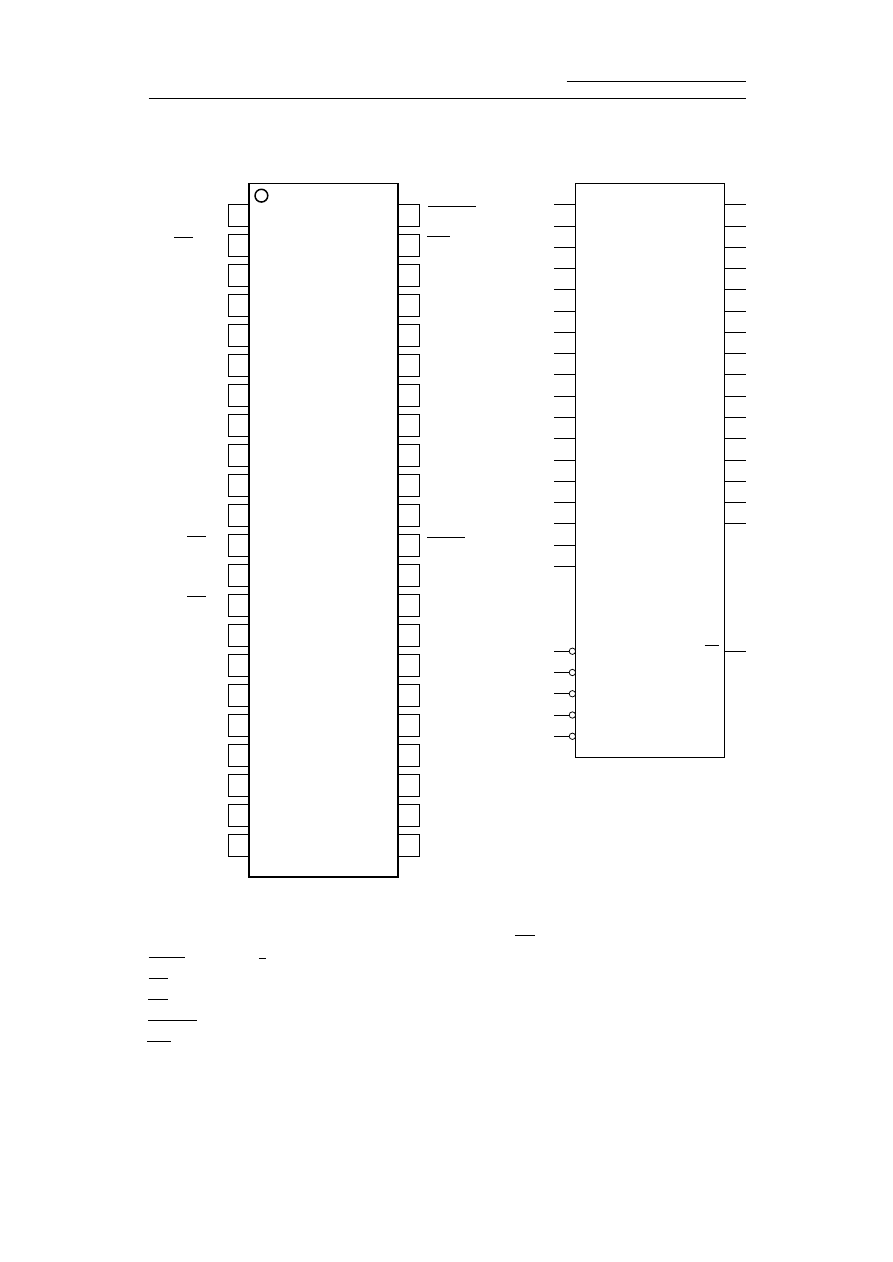

MBM29F400TA-90PF (1/2)

IL11D

3

34

35

36

37

38

39

40

41

42

4

5

6

7

8

9

10

11

43

33

44

12

14

DQ15/A-1

DQ14

DQ13

DQ12

DQ11

DQ10

DQ9

DQ8

DQ7

DQ6

DQ5

DQ4

DQ3

DQ2

DQ1

DQ0

RY/BY

31

29

27

25

22

20

18

16

30

28

26

24

21

19

17

15

2

A17

A16

A15

A14

A13

A12

A11

A10

A9

A8

A7

A6

A5

A4

A3

A2

A1

A0

WE

BYTE

RESET

CE

OE

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

RY/BY

OUT

A17

IN

A7

IN

A6

IN

A5

IN

A4

IN

A3

IN

A2

IN

A1

IN

A0

IN

CE

IN

OE

IN

DQ0

I/O

DQ8

I/O

DQ1

I/O

DQ9

I/O

DQ2

I/O

DQ10

I/O

DQ3

I/O

DQ11

I/O

NC

GND

RESET

IN

WE

IN

A8

IN

A9

IN

A10

IN

A11

IN

A12

IN

A13

IN

A14

IN

A15

IN

A16

IN

BYTE

IN

DQ15/A-1

I/O

DQ7

I/O

DQ14

I/O

DQ6

I/O

DQ13

I/O

DQ5

I/O

DQ12

I/O

DQ4

I/O

GND

V

DD

C-MOS 4 M (512 K

x

8/256 K

x

16)-BIT FLASH MEMORY

—TOP VIEW—

INPUT

A0 - A17, A-1

BYTE

CE

OE

RESET

WE

; ADDRESS

; 8/16 BITS MODE SELECT

; CHIP ENABLE

; OUTPUT ENABLE

; HARDWARE RESET

; WRITE ENABLE

OUTPUT

RY/BY

INPUT/OUTPUT

DQ0 - DQ15

; READY/BUSY

; DATA

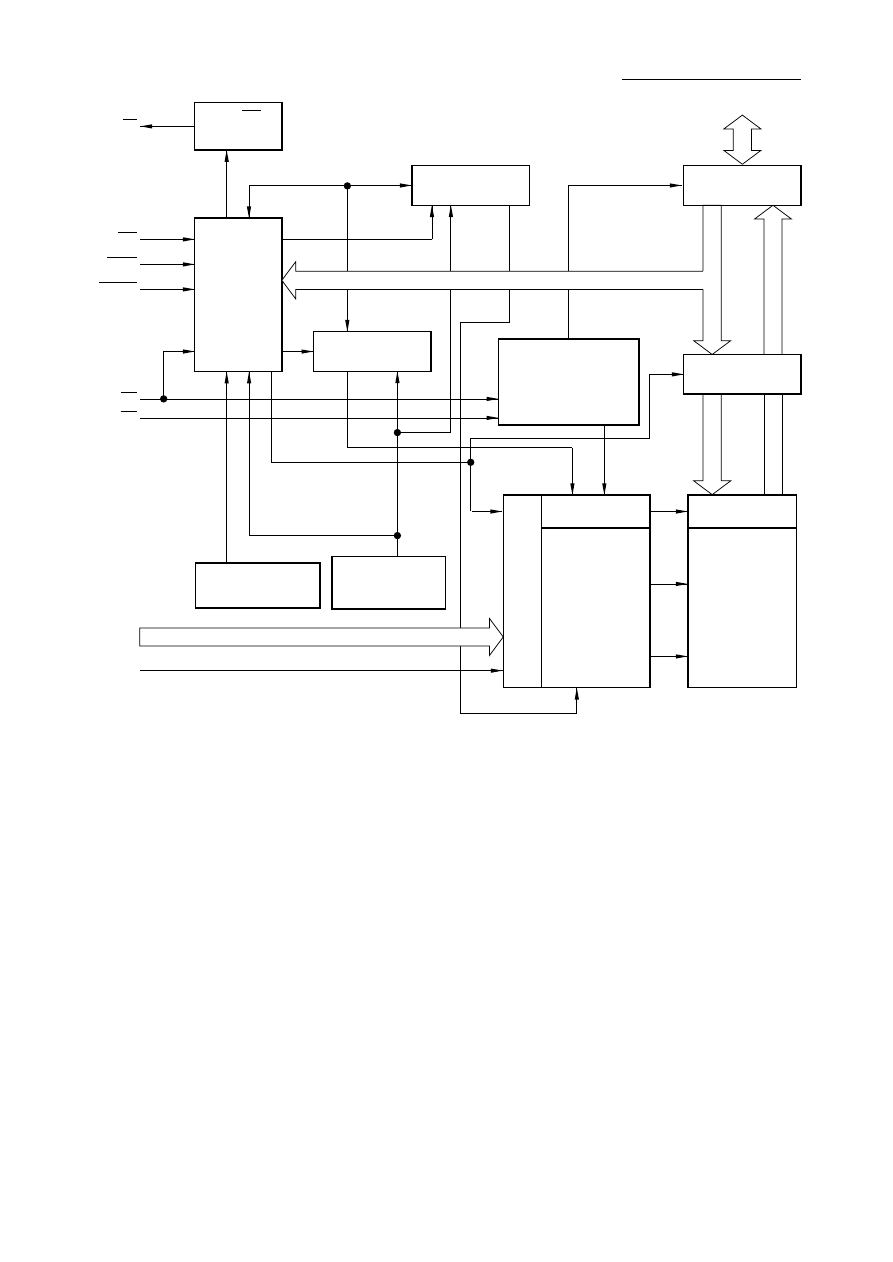

MBM29F400TA-90PF (2/2)

2

RY/BY

43

WE

33

BYTE

44

RESET

12

CE

14

OE

31

A - 1

3 - 11

34 ^ 42

A0 - A17

RY/BY

BUFFER

CONTROL

CIRCUIT

LOW POWER

DETECT CIRCUIT

WRITE/ERASE

PULSE TIMER

WRITE CIRCUIT

ERASE CIRCUIT

INPUT/OUTPUT

BUFFER

DATA LATCH

CHIP ENABLE

OUTPUT ENABLE

CIRCUIT

Y DECODER

Y GATE

X DECODER

4,194,304

CELL

MATRIX

ADDRESS LATCH

STB

DQ0 - DQ15

15 - 22

24 - 31

STB

Wyszukiwarka

Podobne podstrony:

MBM, MBM29F400BA 12PF

MBM, MBM29F016 12PFTN

MBM, MBM29F400TC 90PFTN

MES, Polibuda MBM PWR 2012-2016, Sem. V, MES, koło

ściąga metrologia (2), PWR mbm, Podstawy metrologii

TEST OGÓLNY BHP rozwiązania, Polibuda MBM PWR 2012-2016, Sem. III, Ergonomia i BHP

mbm ocena obszerna

Cwiczenie 08 c, Pwr MBM, Fizyka, Laborki

fizyka dla opornych 2, Pwr MBM, Fizyka, sprawozdania vol I, sprawozdania część I

MÓJ, Polibuda MBM PWR 2012-2016, Sem. V, MES, koło

pytania z materialow z tamtego roku1, PWr - zip, III rok - semestr 6, Materiałoznawstwo I - MBM, Egz

Materialy, MBM PWR, Materiałoznawstwo, Materiały pomocnicze

Seminarium M01-77a 2012 2013, MBM, uczelnia, VI semestr, seminara

cw26(teoria), Studia PWr W-10 MBM, Semestr II, Fizyka, Fizyka - laborki, Fizyka - laborki, Fizyka La

Metalurgia proszków(1), MBMKalisz, mbm, 1

więcej podobnych podstron