105

Elektronika Praktyczna 5/2005

K U R S

LiveDesign w praktyce,

część 3

W poprzednim numerze zatrzy-

maliśmy się z przykładowym projek-

tem układu licznika Johnsona na eta-

pie rozmieszczania elementów. Sche-

mat, pokazany na

rys. 12 zawiera

już wszystkie elementy, ponumerowa-

ne automatycznie, jest wyposażony w

obiekty masy oraz specjalne porty, za-

pewniające komunikację z elementami

płyty uruchomieniowej. Czas przejść

do kolejnego etapu.

Tworzymy połączenia…

…pomiędzy elementami schema-

tu. Sieć połączeń można tworzyć na

dwa sposoby –prowadząc linie połączeń

(wire, bus) pomiędzy wyprowadzeniami

elementów oraz za pomocą etykiet sieci

(net label). Fizyczne połączenia, tworzo-

ne za pomocą przewodów (wire) i ma-

gistral (bus) łączą w jedną sieć obiek-

ty na ich końcach. Ale podobny efekt

można uzyskać, posługując się etykieta-

mi sieci (net label), które łączą w jed-

ną sieć wszystkie punkty obwodu, opa-

trzone tą samą etykietą, pomimo braku

fizycznego połączenia.

Wszystkie połączenia w naszym pro-

jekcie wykonamy jawnie, z wykorzysta-

niem przewodów i magistral, natomiast

niektóre z nich zaopatrzymy w etykie-

ty, które poprawią czytelność schematu

Kontynuujemy kurs projektowania układów programowalnych

za pomocą systemu DXP 2004 firmy Altium. W bieżącym

numerze zajmiemy się dokończeniem i konfiguracją pierwszego

przykładowego projektu FPGA.

i ułatwią poruszanie się po

projekcie.

Zaczynamy od połączeń

przewodami (wire). Nale-

ży pamiętać, żeby nie mylić

przewodów (wire) z liniami

(line), które są obiektami ry-

sunkowymi i nie tworzą po-

łączeń elektrycznych!

Połączenie rozpoczynamy

wybierając z menu menu

Place>Wire

(skrót: P, W)

, a

następnie klikamy punkt na

schemacie, w którym połą-

czenie ma się zaczynać –

zwykle port lub wyprowa-

dzenie elementu. Przesuwa-

my kursor do punktu, w którym chce-

my zacząć kolejny segment połączenia i

klikamy ponownie, aż dojdziemy do in-

nego portu lub wyprowadzenia elemen-

tu, który chcemy przyłączyć. Układa-

nie połączeń możemy kontynuować lub

przerwać, klikając prawy klawisz mysz-

ki lub naciskając ESC.

W trybie prowadzenia połączeń, mo-

żemy zmieniać styl połączenia, który ma

wpływ na wygląd linii połączenia. Na-

ciskając kombinację klawiszy Shift+Spa-

cja

, program przełącza się sekwencyjne

pomiędzy trybem łączenia pod kątem

90º, 45º, dowolnym kątem oraz try-

bem Auto Wire, w

którym wskazujemy

tylko punkty do po-

łączenia, a program

automatycznie wyty-

cza trasę linii.

Prowadząc połą-

czenia, należy zwra-

cać uwagę, aby za-

pewnić prawidło-

wy styk przewodu

z wyprowadzeniem

elementu lub portu.

Prawidłowe połą-

czenie następuje w

miejscu styku, który

program wskazuje

kursorem w kształ-

cie powiększonego,

czerwonego krzyża. Nie jest to trudne,

ponieważ przy prawidłowych ustawie-

niach poruszamy się po siatce, a po-

nadto program sam „przyciąga” kursor

do punktów styku, kiedy tylko zbliży-

my się w ich pobliże.

Należy wykonać wszystkie połącze-

nia, zwracając uwagę na miejsca, w któ-

rych linie się krzyżują. Kiedy w miej-

scu przecięcia linii widać mały, okrągły

punkt połączenia – miejsce takie stano-

wi połączenie elektryczne. W przeciw-

nym wypadku, połączenia niema. Pro-

gram automatycznie wstawia punkty

połączeń i powinny się one pojawić w

miejscach, które widać na pokazanym

schemacie (

rys. 13).

Oznaczamy połączenia…

…za pomocą etykiet sieci (Net La-

bel

), które poprawią czytelność schema-

tu. Mimo, że w naszym przypadku na-

noszenie etykiet nie jest konieczne, po-

nieważ wszystkie połączenia są wyko-

nane jawnie, oznaczanie etykietami jest

dobrą praktyką. Taki schemat jest bar-

dziej czytelny, łatwiej się po nim poru-

szać i wykrywać błędy.

Etykiety umieszczamy wybierając z

menu Place>Net Label (skrót: P, N)

.

Obok znaku kursora pojawi się symbol

etykiety. Można ją edytować, zanim zo-

stanie położona na schemacie. Naciśnię-

cie klawisza TAB uruchamia okno dialo-

Rys. 12. Arkusz schematu z rozłożonymi elementami licz-

nika Johnsona

Rys. 13. Schemat licznika Johnsona z poprowa-

dzonymi połączeniami i naniesionymi etykietami

K U R S

Elektronika Praktyczna 5/2005

106

gowe Net Label. Zmieniamy nazwę ety-

kiety np. na LEFT i klikamy OK, aby

zamknąć okno dialogowe.

Kładziemy etykietę na schemacie w

taki sposób, aby jej dolny, lewy róg

(tzw. gorący punkt), dotykał miejsca,

które chcemy oznaczyć. Kiedy dotyka-

my połączenia, kursor zmienia kształt

na czerwony krzyż, który oznacza pra-

widłowy punkt styku.

Nanosimy etykiety w miejscach po-

kazanych na schemacie. Należy zwracać

uwagę, aby nazwy etykiet były unikal-

ne. Nie można również nanosić dwóch

różnych etykiet, dla tego samego połą-

czenia. Klikając prawy klawisz myszki

lub ESC, opuszczamy tryb nanoszenia

etykiet.

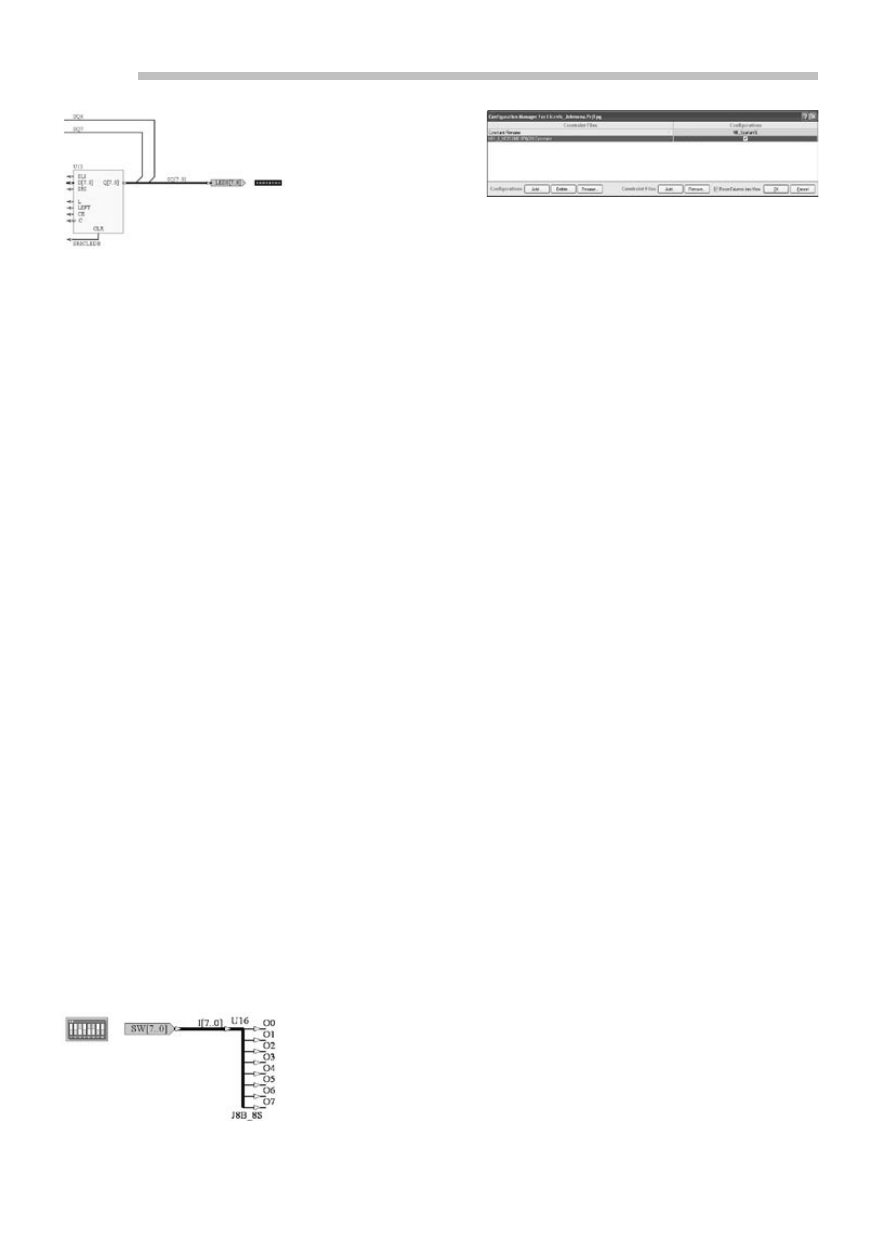

Magistrale…

…uzupełniają pojedyncze połącze-

nia w przypadkach, kiedy mamy do

czynienia z grupą sygnałów. Prowa-

dzenie połączeń magistralowych odby-

wa się podobnie, jak dla pojedynczych

przewodów, ale trzeba pamiętać o kil-

ku kwestiach. Przede wszystkim, nale-

ży oznaczać etykietami wszystkie magi-

strale oraz ich fragmenty, które nie za-

chowują ciągłości. Trzeba pamiętać rów-

nież, że szerokość magistrali i łączo-

nych obiektów powinna być taka sama.

Istotne jest również to, że połączenia

sygnałów obiektu i magistrali przebie-

gają zawsze od lewej strony, do pra-

wej, więc inaczej zachowuje się magi-

strala oznaczona np. D[0..7], a inaczej

D[7..0], choć obie posiadają identyczną

szerokość i te same sygnały. W naszym

projekcie wykorzystamy magistralę ozna-

czoną SQ[7..0] do połączenia portu LED

do elementu SR8CLEDB, jak pokazano

na

rys. 14.

Magistralę wybieramy

z menu Place>Bus (skrót

P, B) i prowadzimy iden-

tyczną techniką, jak po-

jedyncze połączenie. Na-

stępnie magistralę ozna-

czamy etykietą SQ[7..0].

Należy zawsze nadawać

etykiety magistralom, po-

nieważ inaczej nie da się jasno okre-

śli, w jaki sposób magistrala łączy ele-

menty na jej końcach.

Musimy jeszcze dodać wejścia do

magistrali, jak pokazano na rys. 14.

Wybieramy z menu Place>Bus Entry

(skrót: P, U) i umieszczamy dwa wej-

ścia do naszej magistrali SQ[7..0] z po-

łączeń SQ0 i SQ7. W tym trybie, ko-

rzystając z klawisza SPACJI, możemy

obracać wejścia do szyny, aby dopaso-

wać odpowiedni kąt podłączenia. Klika-

jąc prawy klawisz myszki lub naciska-

jąc ESC, opuszczamy tryb nanoszenia

wejść do magistrali.

Jeszcze jedną magistralę należy do-

dać pomiędzy przełącznikiem DIP i ele-

mentem J8B_8S, jak widać na

rys. 15.

Sprawdzamy schemat...

…uruchamiając kompilację projek-

tu. Podczas kompilacji program prze-

prowadza m.in. weryfikację projektu w

oparciu o szereg kryteriów, które kon-

figurujemy w zakładce Error Reporting

okna dialogowego Options for FPGA Pro-

ject,

dostępnego z menu Project>Project

Options

.

Uruchamiamy kompilację, wybierając

z menu Project>Compile FPGA Project

[nazwa_projektu]

. Jeśli wystąpią istotne

błędy, pojawią się one automatycznie w

panelu Messages. Mniej ważne ostrze-

żenia również pojawiają się w pane-

lu Messages, jednak żeby je zobaczyć,

musimy ręcznie wywołać panel, klika-

jąc zakładkę System

u dołu okna pro-

jektu i wybierając Messages. Alterna-

tywnie panel możemy włączyć z menu

View>Workspace Panels>System>Messa-

ges

. Klikając dwukrotnie każdą linię z

informacją o błędzie, uzyskujemy dostęp

do szerszej informacji na jego temat, z

możliwością wskazania miejsca wystą-

pienia na schemacie.

Konfigurujemy projekt…

…aby określić platformę sprzęto-

wą, na której będzie zaimplementowa-

ny. Wykorzystamy w naszym przykła-

dzie płytę uruchomieniową NanoBo-

ard z zamontowanym jednym z modu-

łów FPGA, który zawiera układ Xilinx

Spartan IIE XC2S300E–6PQ208C. Doda-

my teraz konfigurację i tzw. pliki con-

straint

, które określają numerację wypro-

wadzeń i nazwę układu FPGA na pły-

cie NanoBoard.

Wybieramy z menu polecenie Pro-

ject>Configuration Manager

, które uru-

chamia okno dialogowe Configura-

tion Manager For [nazwa_projektu]

(

rys. 16). Dodajemy konfigurację klika-

jąc przycisk Add w sekcji Configura-

tions

i nadajemy jej nazwę np. NB_

SpartanIIE, która w jasny sposób okre-

śla docelową implementację.

Teraz dodajemy plik constraint (wy-

muszeń projektowych) do naszej konfi-

guracji, klikając przycisk Add w sek-

cji Constraints. Wybieramy plik NB1_

6_XC2S300E–6PQ208.Constraint, który

jest zlokalizowany w folderze ...\Altiu-

m2004\Library\FPGA

. Trzeba jeszcze za-

znaczyć kratkę obok dołączonego pli-

ku constraint.

Po kliknięciu przycisku OK, okno

dialogowe zostanie zamknięte, a w

strukturze naszego projektu pojawi się

nowy folder nazwany Settings, który za-

wiera dodany właśnie plik w folderze

Constraint Files

.

Plik możemy otworzyć i przeanali-

zować w oknie edytora tekstowego w

środowisku DXP. Gdybyśmy chcieli za-

implementować projekt na innym ukła-

dzie FPGA, np. Altera Cyclone, który

również znajduje się w zestawie z pły-

tą NanoBoard, należy dodać nową kon-

figurację. Otwieramy okno Configura-

tion Manager

, jak poprzednio i doda-

jemy nową konfigurację, klikając przy-

cisk Add. Następnie, do nowej konfigu-

racji dodajemy plik ...\Altium2004\Libra-

ry\FPGA\NB1_6_EP1C12Q240.Constraint

,

który jest właściwy dla płyty NanoBo-

ard z układem Altera Cyclone.

W podobny sposób, możemy przy-

gotować konfiguracje projektu na inne

platformy, np. na płytę uruchomienio-

wą z zestawu ewaluacyjnego LiveDesign

firmy Altium lub konfigurację dla na-

szej własnej płyty PCB, na której znaj-

dzie się docelowo kość FPGA. Odpo-

wiedni plik constraint można przygoto-

wać ręcznie, bazując na przykładach i

dokumentacji.

Za miesiąc zajmiemy się programo-

waniem układu FPGA i uruchamianiem

projektu.

Grzegorz Witek, Evatronix

Rys. 14. Widok magistrali i wejść do

magistrali

Rys. 15. Połączenie magistralowe po-

między przełącznikiem DIP i elemen-

tem J8B_8S

Rys. 16. Wygląd okna dialogowego Configuration

Manager

Wyszukiwarka

Podobne podstrony:

11 2005 105 106

105 106 407 pol ed02 2005

Świecie 14 05 2005

05 2005 031 036

105 106 (2)

05 2005 066 067

105 106

Rozp Ministra Infrastruktury z 6 05 2005 r w sprawie pozbawienia dróg kategorii dróg krajowych (2)

10 2005 103 106

31.05.2005 ginexy II potok, gielda(1)

rmf wykład6 (4 05 2005) WOYE6RE7JDI27GP2VL2DTKPRQIOFPZ5DFKTIZWA

06 2005 103 106

1510466 1800SRM0985 (05 2005) UK EN

1580505 0700SRM1123 (05 2005) UK EN

1283890431 Control Engineering 05 2005

więcej podobnych podstron