PRACA PRZEJŚCIOWA

Z

PROJEKTOWANIA UKŁADÓW

ANALOGOWYCH

Temat: Przetwornica napięcia z 5V na

±

12V

Wykonawca:

Marcin Szpakiewicz

WSZ sem. VII gr. E2

Rok szk. 2001/2002

2

Wstęp

Celem mojej pracy było zaprojektowanie układu, który miał za zadanie

powielać napięcie wejściowe. Napięcie zasilania (wejściowe) wynosi +5V,

natomiast napięcia wyjściowe zgodnie z założeniem projektu miały wynosić

odpowiednio +12V i –12V. Projekt został oparty na zwykłym powielaczu

napięcia, z zastosowaniem odpowiednio sterowanych kluczy tranzystorowych.

Zaletą układu jest to, że na wyjściu mamy dwa napięcia dodatnie i ujemne,

natomiast wadą układu jest bardzo mała wydajność prądowa.

3

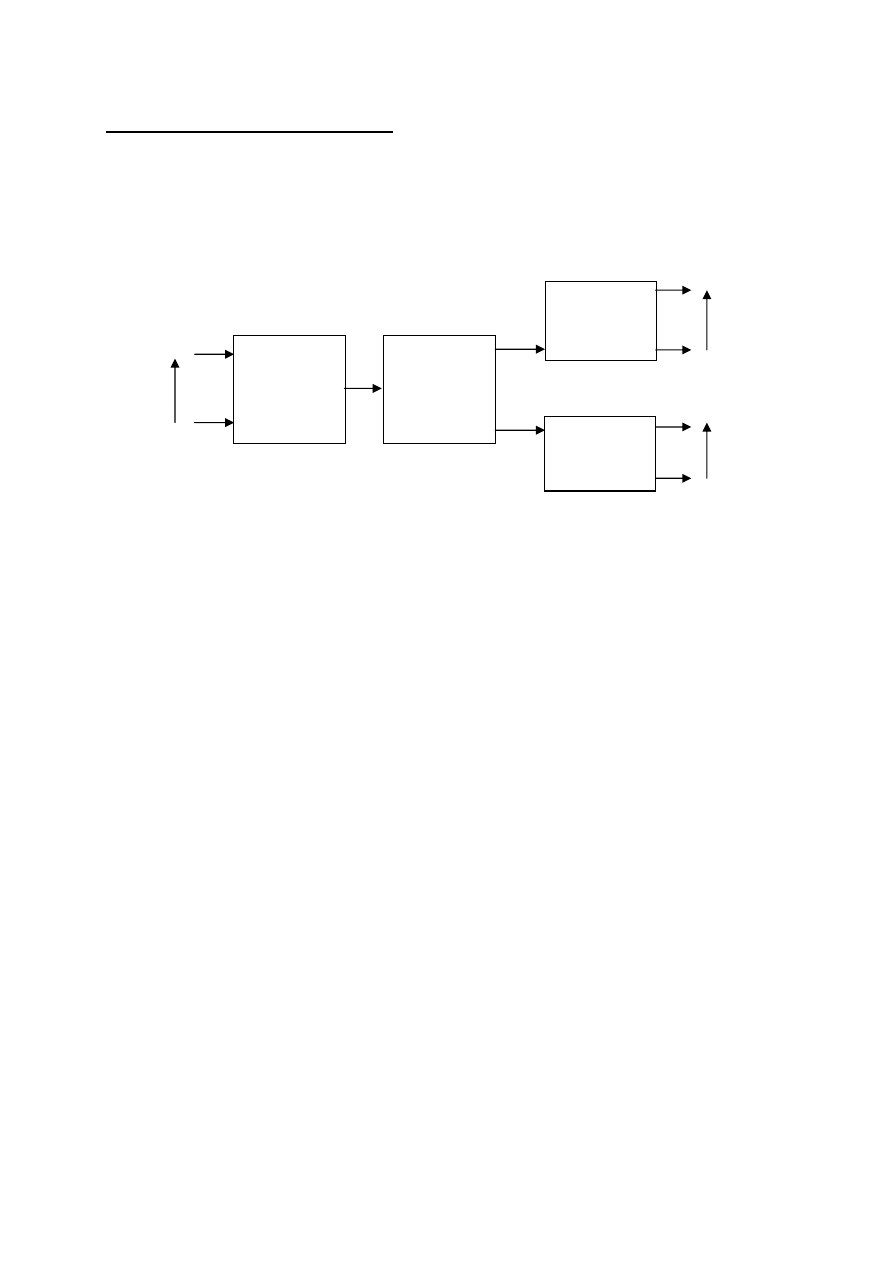

Schemat blokowy układu

Jak widać na schemacie blokowym układ składa się z czterech bloków.

Pierwszym z nich jest generator przebiegu prostokątnego, który będzie sterował

kluczami tranzystorowymi, tak aby w odpowiedni sposób przeładowywały one

kondensatory w blokach powielaczy napięcia. Napięcie wejściowe U

we

=5V,

natomiast napięcie wyjściowe powinno wynosić U

wy

=12V.

U

we

-U

wy

Generator

fali

prostokątnej

Zespół klu-

czy tran-

zystoro-

wych

Powielacz

napięcia

dodatniego

Powielacz

napięcia

ujemnego

U

wy

4

Realizacja poszczególnych bloków

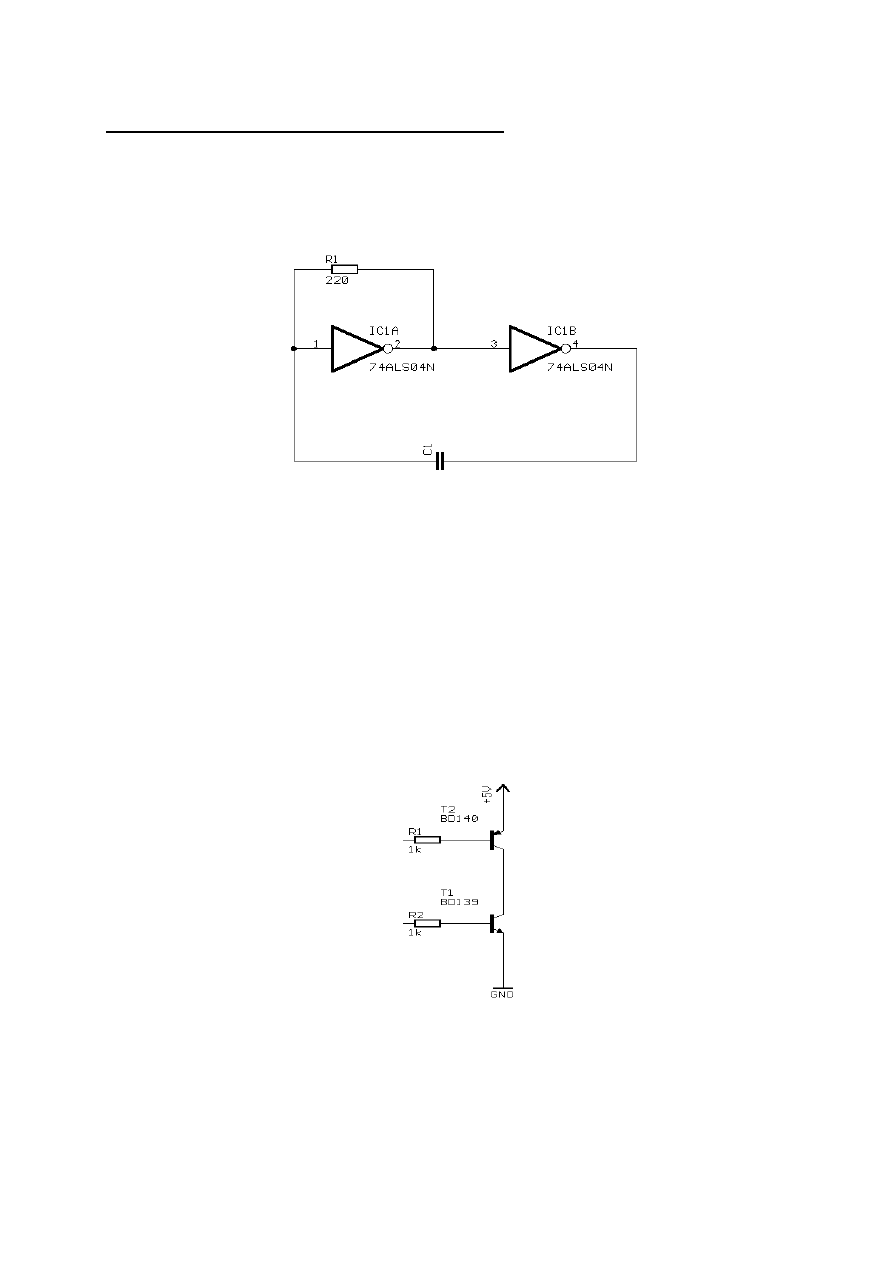

1) Generator fali prostokątnej

Generator zrealizowano z wykorzystaniem układu scalonego

zrealizowanego w technice TTL. Do budowy generatora wykorzystano

inwertery 7404 z serii LS. W układzie tym rezystor linearyzuje jeden z

inwerterów, co poprawia pewność wzbudzenia się drgań tego generatora.

Kondensator C1 zapewnia sprzężenie zwrotne. Okres przebiegu na wyjściu

jest określony poniższym wzorem.

C

R

T

⋅

⋅

=

3

2) Klucze tranzystorowe

Klucze tranzystorowe zbudowano w oparciu o tranzystor npn i pnp. Takie

połączenie tranzystorów zapewnia, że w danej chwili gdy na wejściu mamy

stan wysoki to będzie przewodził tranzystor T1, a gdy mamy stan niski

przewodził będzie tranzystor T2.

5

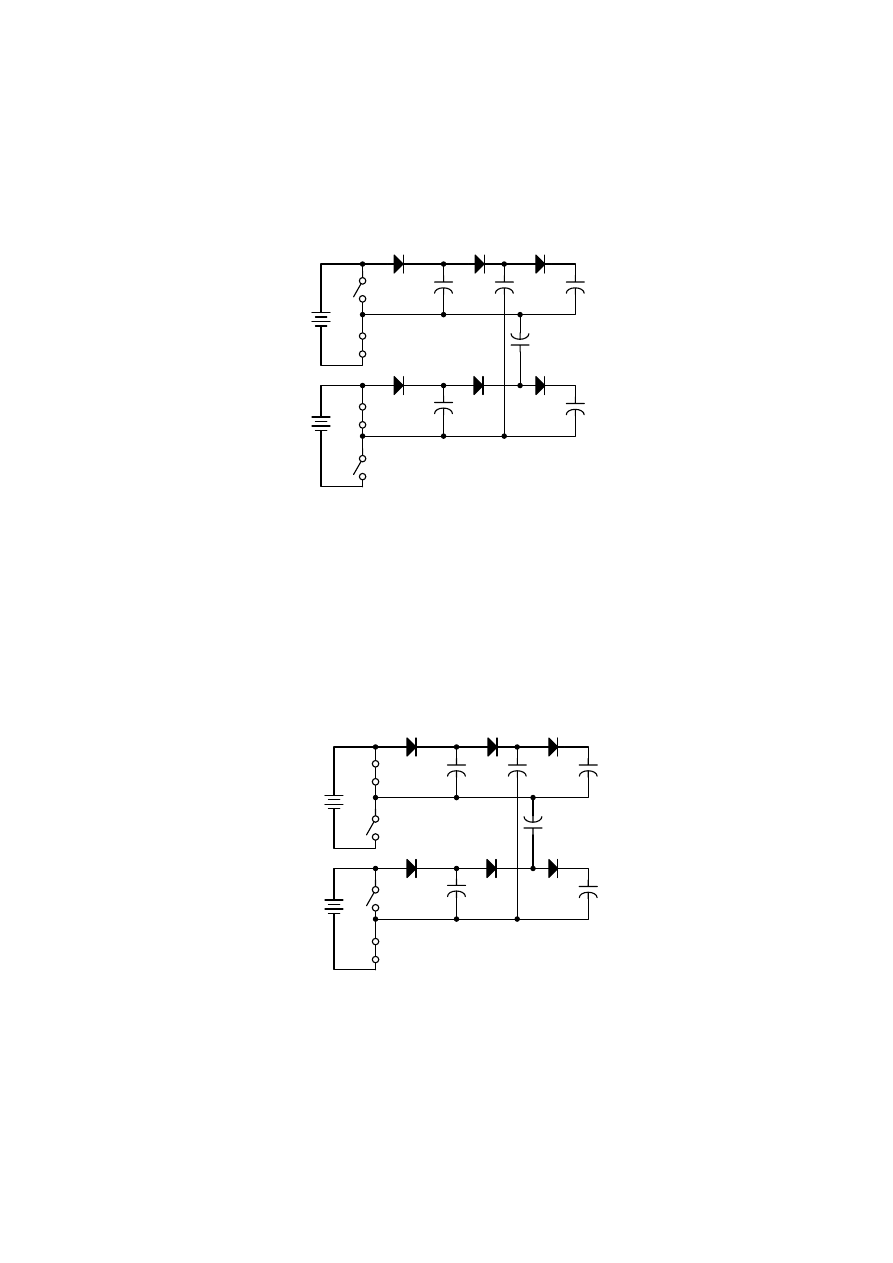

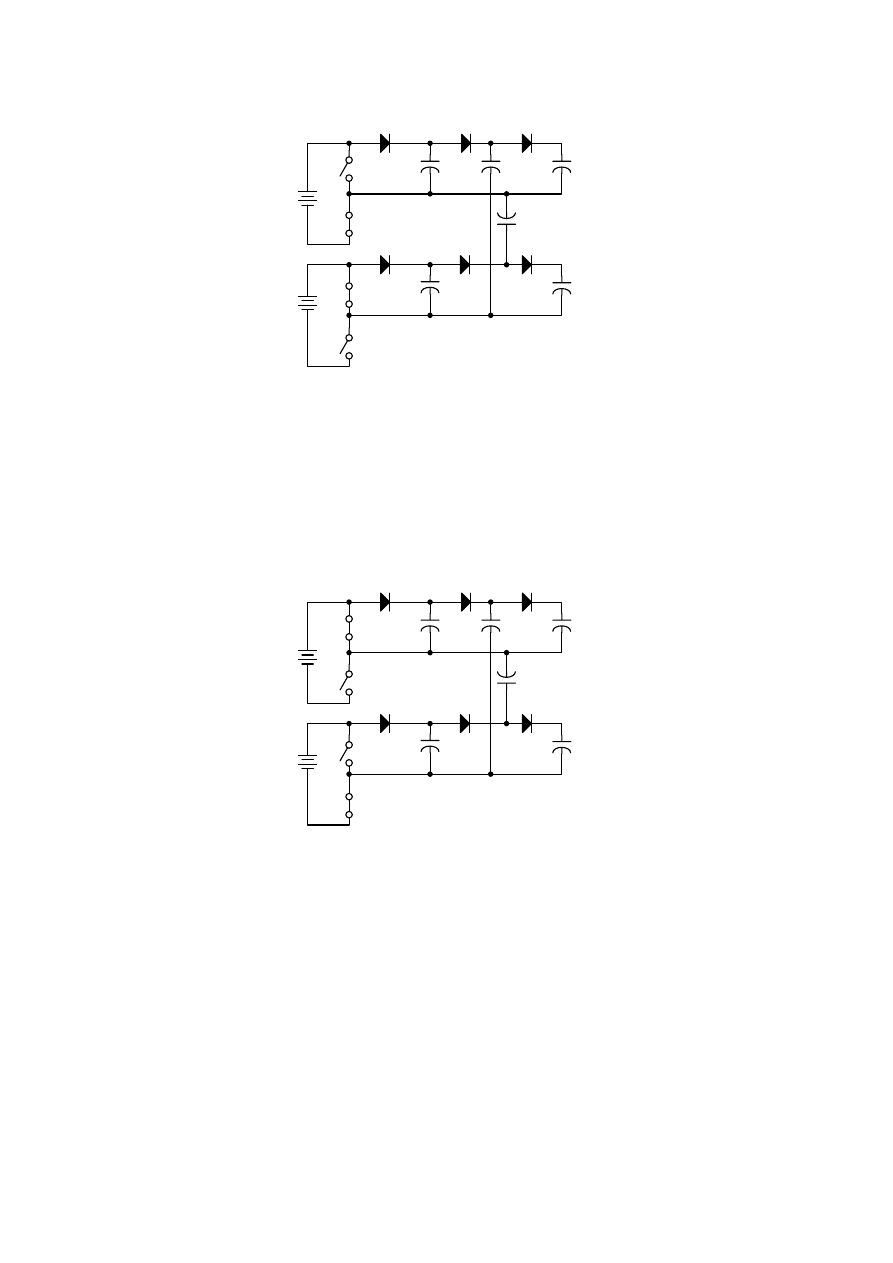

3) Układ powielacza napięcia i jego zasada działania

+ V2

+ V1

S4

S3

D6

D5

D4

+

C6

+

C4

S2

S1

+

C5

D3

D2

D1

+

C3

+

C2

+

C1

Układ składa się z dwóch identycznych powielaczy napięcia sterowanych

kluczami S1, S2, S3 i S4, połączonych z źródłami zasilania V1 i V2.

Zakładamy, że w pierwszej fazie powielania napięcia klucze S2 i S3 są

zwarte. W takim układzie ładuje się — poprzez diodę D1 — kondensator C1 do

napięcia zasilania V1. U

C1

=V1.

+ V2

+ V1

S4

S3

D6

D5

D4

+

C6

+

C4

S2

S1

+

C5

D3

D2

D1

+

C3

+

C2

+

C1

Po

naładowaniu się kondensatora C1, następuje przełączenie kluczy

i teraz zwarte są S1 i S4. Jak widać kondensator C4 ładuje się poprzez diodę D4

i klucz S4 do napięcia zasilania V2, wynika stąd, że napięcie U

C4

=V2.

Równocześnie w takim układzie ładuje się kondensator C2 poprzez klucz S1,

kondensator C1 oraz klucz S4. Napięcie na kondensatorze C2 będzie wynosiło

napięcie zasilania V1 powiększone o napięcie U

C1

(U

C2

=V1+U

C1

).

6

+ V2

+ V1

S4

S3

D6

D5

D4

+

C6

+

C4

S2

S1

+

C5

D3

D2

D1

+

C3

+

C2

+

C1

Znowu

następuje przełączenie kluczy i znowu przewodzą klucze S2 i S3.

Tym razem ładuje się kondensator C5 poprzez klucz S3, kondensator C4 diodę

D5 i klucz S2. Wartość napięcia na tym elemencie wynosi U

C5

=U

C4

+V2.

Dodatkowo ładuje się kondensator C3, poprzez klucz S3, kondensator C2, diodę

D3 i klucz S2. Napięcie U

C3

=U

C2

+V2. Również rozpoczyna się powtórny cykl

ładownia kondensatora C1.

+ V2

+ V1

S4

S3

D6

D5

D4

+

C6

+

C4

S2

S1

+

C5

D3

D2

D1

+

C3

+

C2

+

C1

Przy ponownym przełączeniu kluczy, ładuje się nam kondensator C6,

poprzez klucz S1, kondensator C5, diodę D6 i klucz S4. Tym sposobem na

kondensatorze C6 mamy napięcie równe co do wartości napięciu V1+U

C5

. Jeżeli

przyjmiemy, że napięcia V1=V2=Vz to na kondensatorach C3 i C6 mamy takie

same napięcia równe:

Vz

U

U

C

C

⋅

=

=

3

6

3

Przyjmując napięcie zasilania Vz=5V, na wyjściu układu mamy napięcie

15V, w zależności jak podłączymy się do okładek kondensatorów C3 i C6,

będziemy mieli, albo napięcie dodatnie, albo ujemne.

7

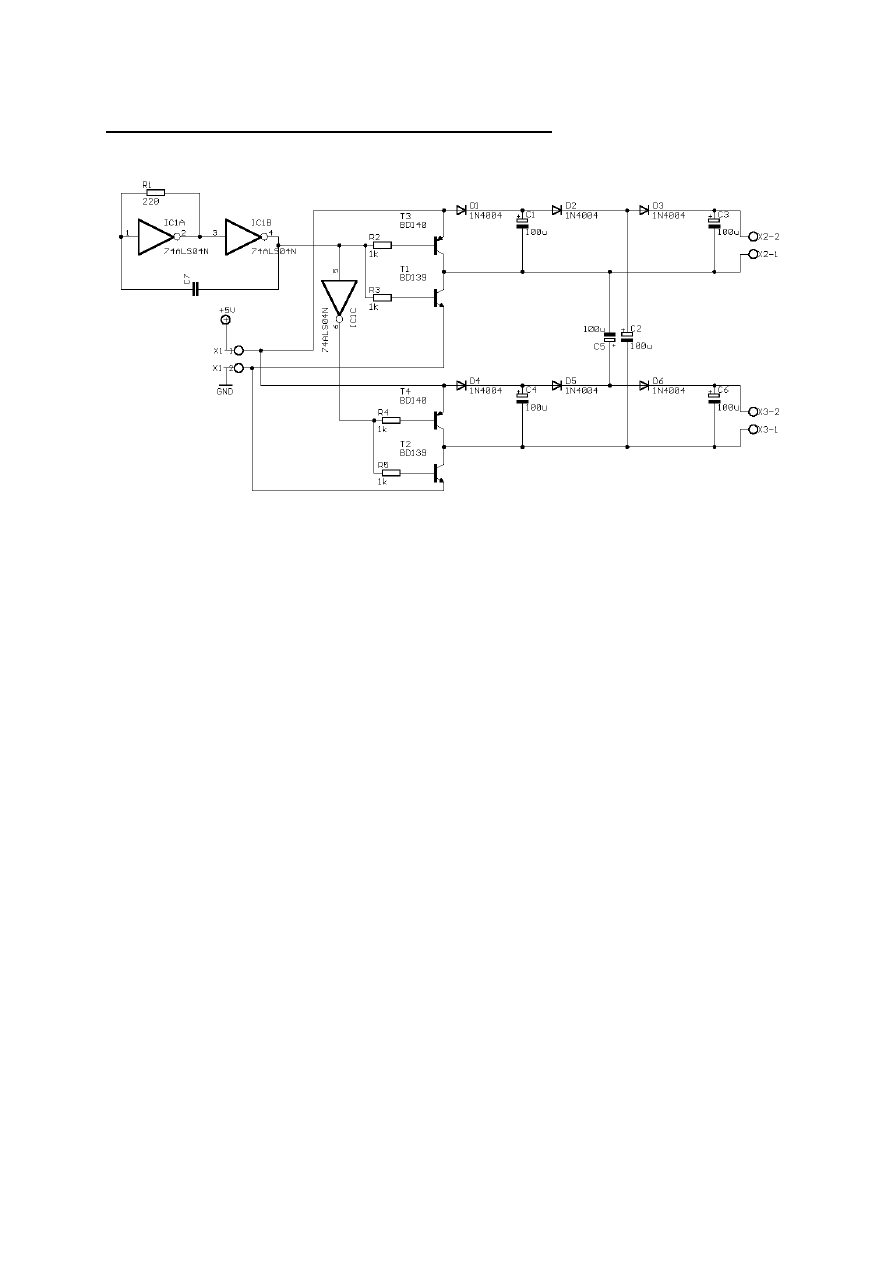

Schemat ideowy przetwornicy napięcia

Powyżej znajduje się schemat ideowy przetwornicy napięcia. Układ jest

zasilany napięciem +5V. Role kluczy S1 i S3 spełniają tranzystory T3 i T4,

natomiast odpowiednikiem kluczy S2 i S4 są tranzystory T1 i T2. Rezystory R2

do R5 mają za zadanie ograniczyć prąd baz tranzystorów. Przełączaniem kluczy,

tak jak to omówiono w poprzednim rozdziale „zajmuje” się generator

prostokątny, z którego bezpośrednio podawany jest sygnał na klucz T3 i T1,

a na klucz T4 i T2, sygnał ten podawany jest poprzez bramkę NOT, tak aby

zapewnić przeciwną polaryzacje kluczy. Ponieważ w poprzednim rozdziale

przyjęliśmy, że diody są idealne to napięcie na wyjściu było równe

U

C6

=U

C3

=15V. W układzie rzeczywistym na diodach wystąpi spadek napięcia

wobec czego napięcie wyjściowe będzie pomniejszone o ten spadek i będzie

wynosić:

D

WE

C

C

U

U

U

U

⋅

−

⋅

=

=

3

3

3

6

Ponieważ spadek na diodzie wynosi ok. 0.6 V to npięcie wyjściowe

będzie równe:

V

V

V

U

U

C

C

2

,

13

8

,

1

15

6

3

=

−

=

=

8

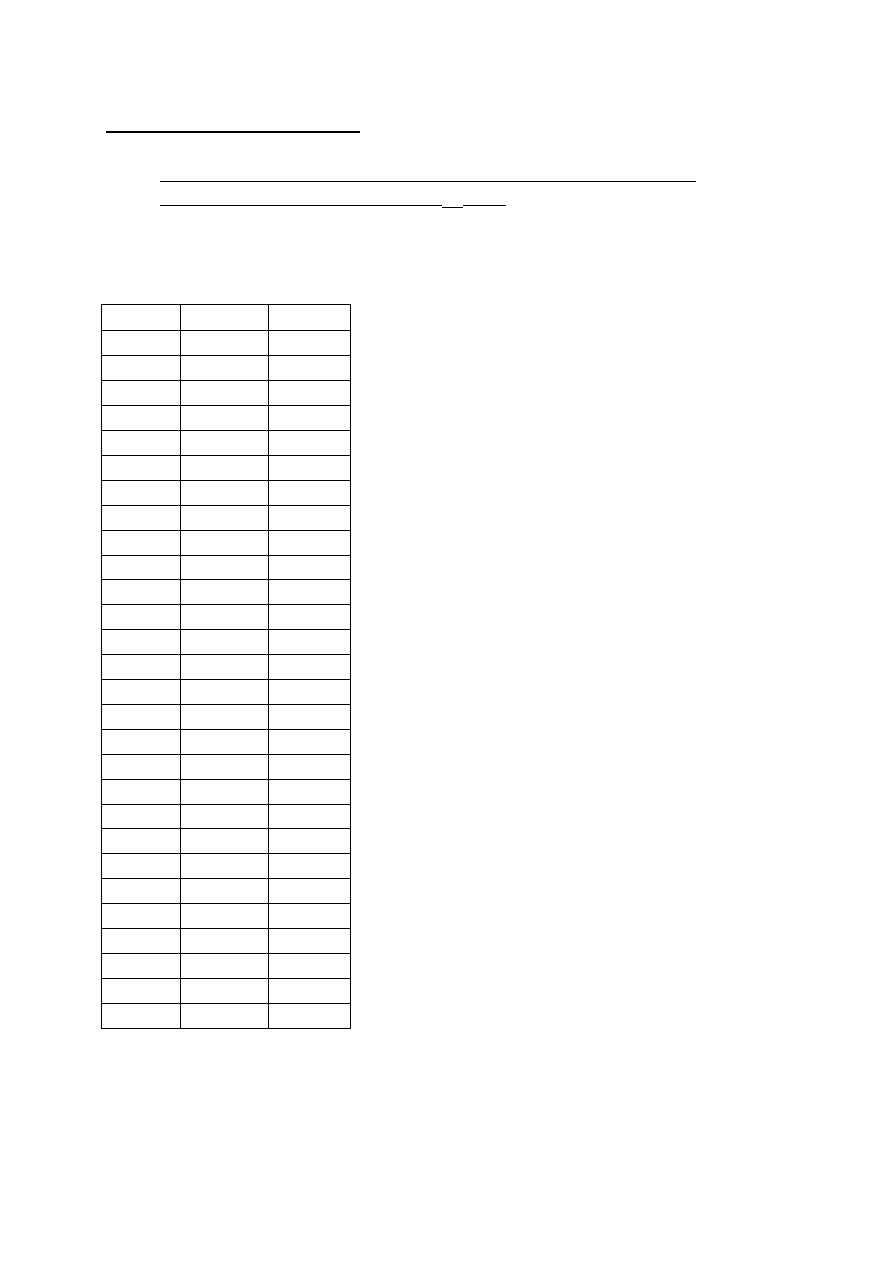

Pomiary laboratoryjne

1) Pomiar napięcia wyjściowego względem obciążenia, dla dwóch

częstotliwości kluczowania dla U

WE

=5V.

a) Dla f

gen

=15,15

[kHz]

R

obc

[

Ω

] I

obc

[mA] U

WY

[V]

100k 0,12

13,02

90k 0,14

13,02

80k 0,15

12,95

70k 0,18

12,86

60k 0,21

12,82

50k 0,24 12,82

40k 0,31

12,74

30k 0,41

12,66

20k 0,61

12,56

10k

1,2

12,36

9k

1,34

12,34

8k

1,52

12,30

7k

1,68

11,91

6k 2,01

11,72

5k 2,34 11,63

4k 2,88 11,62

3k 3,79 11,62

2k 5,56 11,59

1k

10,62

10,71

900

11,64

10,55

800

13,05

10,34

700

14,38

10,10

600

16,35 9,81

500

18,96 9,40

400 22,15 8,85

300 27,10 8,03

200 35,15 6,74

100 47,10 4,46

9

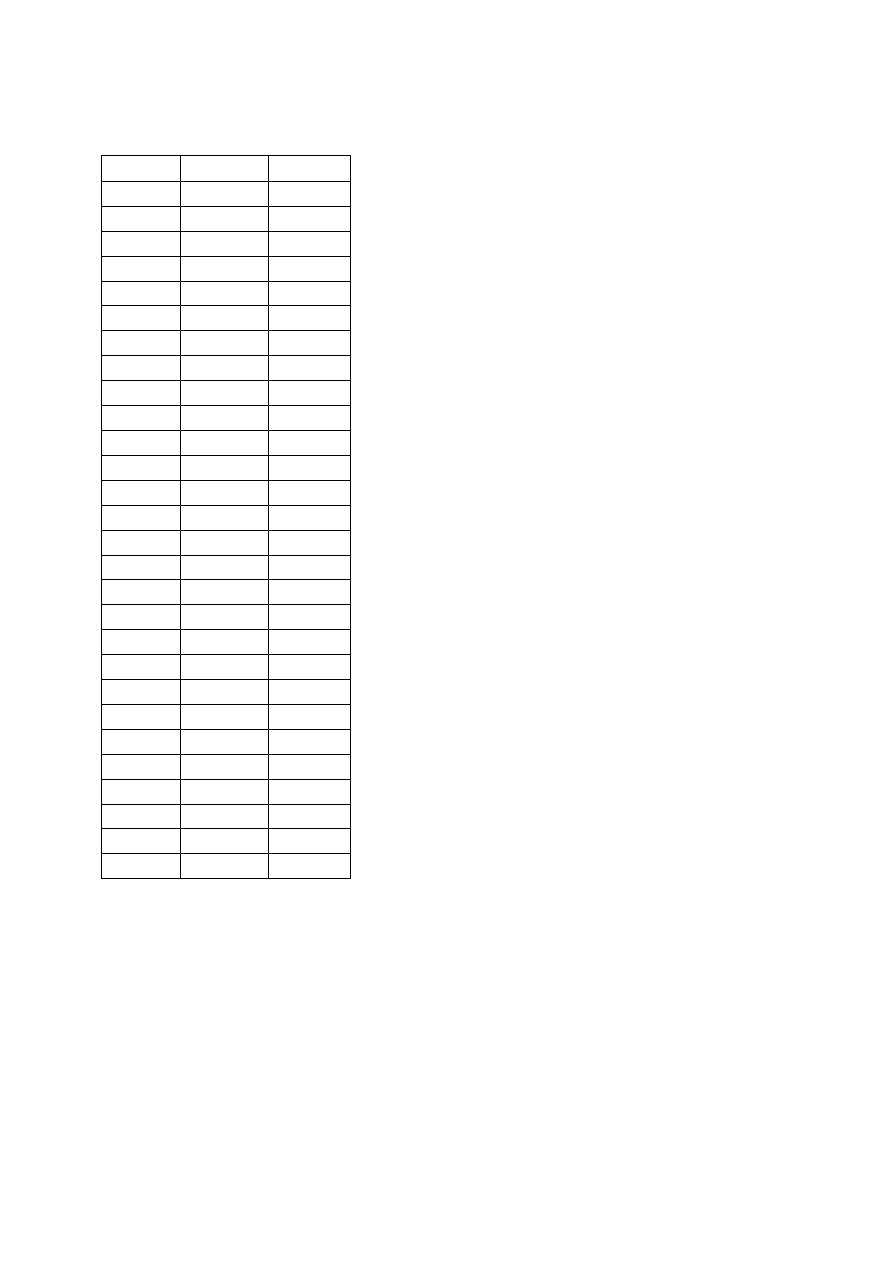

b) Dla f

gen

=1,515 [kHz]

R

obc

[

Ω

] I

obc

[mA] U

WY

[V]

100k 0,12

12,69

90k 0,13

12,64

80k 0,15

12,64

70k 0,17

12,64

60k 0,20 12,64

50k 0,25 12,63

40k 0,31

12,56

30k 0,41

12,51

20k 0,61

12,44

10k

1,20

12,17

9k

1,33

12,16

8k

1,50

12,14

7k

1,71

12,13

6k 2,00 12,05

5k 2,37 12,00

4k 2,92 11,82

3k 3,87 11,75

2k 5,71

11,56

1k

10,89

11,04

900

12,00

10,91

800

13,29

10,76

700

14,86

10,54

600

16,89

10,26

500

19,46 9,87

400 23,00 9,35

300 28,70 8,76

200 37,00 7,54

100 50,34 5,17

10

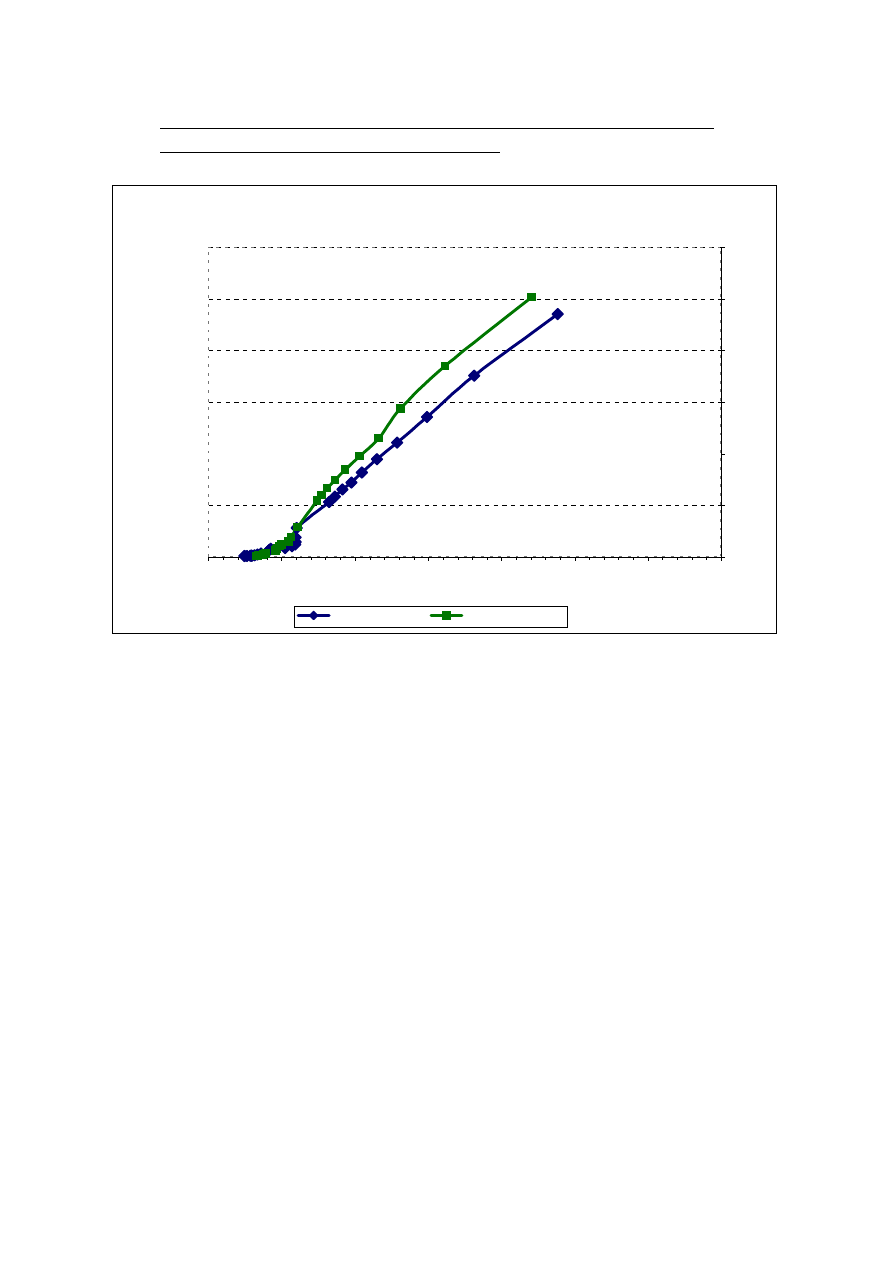

2) Wykres zależności napięcia wyjściowego względem obciążenia na

podstawie przeprowadzonych pomiarów

Zależność napięcia wyjściowego od obciążenia

0

10

20

30

40

50

60

0

2

4

6

8

10

12

14

Napięcie wyjściowe [V]

Pr

ąd obci

ąż

enia [mA]

fgen=15,15kHz

fgen=1,515 kHz

Jak wynika z otrzymanych pomiarów, na wyjściu układu otrzymujemy

powielone napięcie wejściowe, około 3 razy (pomniejszone o spadki napięć na

diodach). Jednak wraz ze wzrostem prądu obciążenia można zauważyć spadek

napięcia wyjściowego. Wynika to stąd, że kondensatory nie „nadążają”

z przeładowywaniem się. Pomiary przeprowadzono dla dwóch częstotliwości.

Jak widać dla częstotliwości fgen=1,515 kHz prąd przy którym napięcie

wyjściowe jest równe ok. 12V, jest większe o 1mA niż dla częstotliwości

fgen=15,515 kHz. Poza tym, przy obciążeniu układu prądem w granicach

50mA, na wyjściu dla drugiego pomiaru napięcie jest trochę większe od

napięcia zasilania, natomiast dla pomiaru pierwszego na wyjściu otrzymujemy

napięcie niższe niż napięcie zasilania.

11

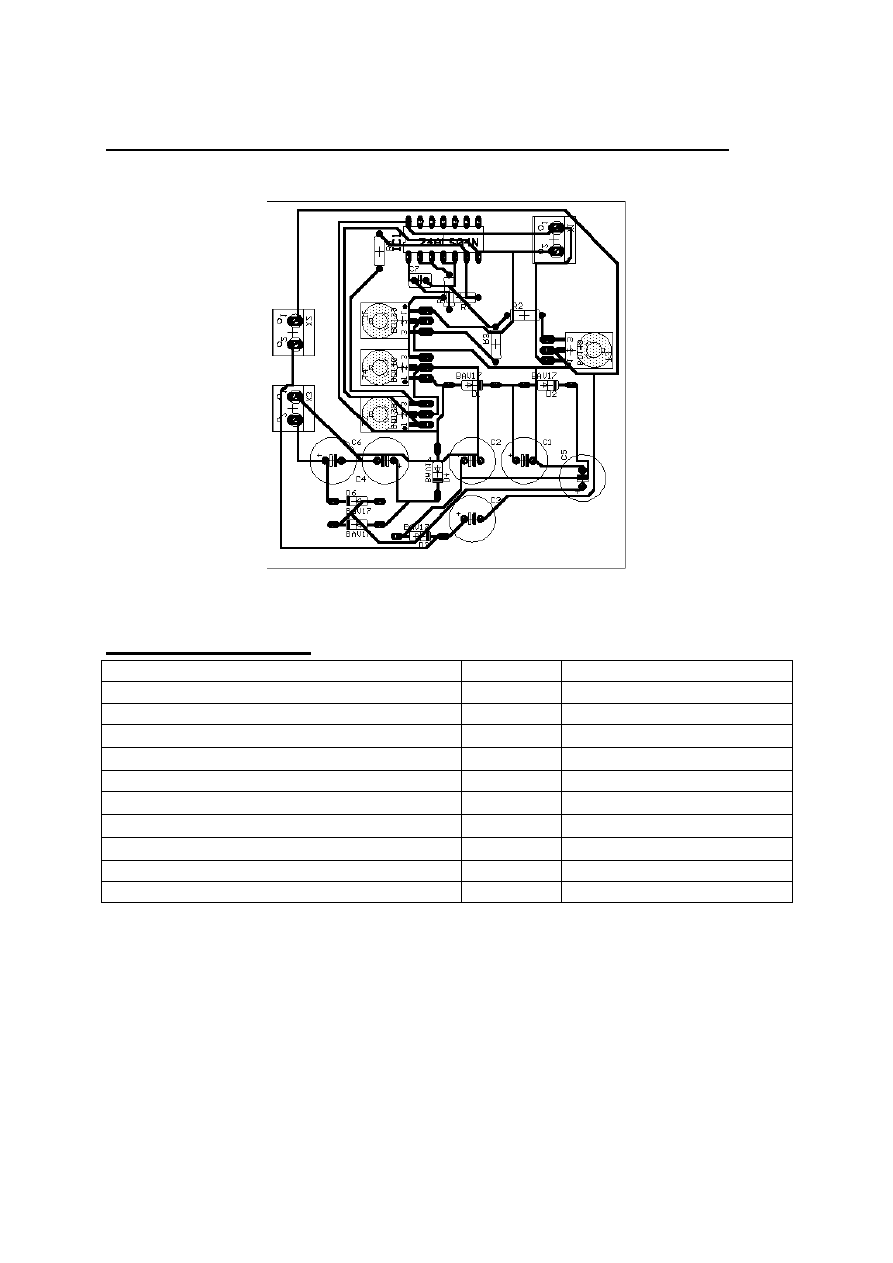

Projekt obwodu drukowanego dla układu przetwornicy

Wykaz elementów

Nazwa Typ

Ilość sztuk

Tranzystor npn T1, T2

BD 139 2

Tranzystor pnp T3, T4

BD 140 2

Diody D1

÷

D6

1N4002 6

Kondensatory elektrolityczne C1

÷

C6

100

µ

F

6

Kondensator C7

100nF

1

1

µ

F

1

Rezystor R2

÷

R4

1k 4

R1

200

Ω

1

Układ TTL IC1 7404

1

Połączenia śrubowe X1, X2, X3

3

12

Literatura

„Praktyczny elektronik” numery 4/96, 6/98

„Elektronika dla Wszystkich” numery 12/00, 3/99, 3/96, 7/96

Strony internetowe:

http://www.eletroda.pl/

http://www.elektro.prv.pl/

http://boss.iele.polsl.gliwice.pl/katalogi/

Wyszukiwarka

Podobne podstrony:

przetwornica 5vna12v

przetworniki indukcyjne

Prop aut W9 Ses cyfr Przetworniki fotoelektryczne

Przetworstwo produktow rolniczych

MLEKO I PRZETWORY MLECZNE (2)

Ceny detaliczne i spożycie warzyw i ich przetworów

W10 Przetw A Cmin

W9 Przetw C A

przetworniki II opracowane

Przetwarzanie mleka koziego

dupont przetworstwo tworzyw4

Przetwornica buck id 406722 Nieznany

Materiały nieżelazne Tworzywa sztuczne Przetwórstwo Auto Expert

przetworka spr ostatnie

dupont przetworstwo tworzyw9

Przetwornica el

Przetwarzanie i utrwalanie żywności (2)

więcej podobnych podstron