Zbli¿amy siê ju¿ do koñca tego cy-

klu – wielu pomyœli nareszcie. Przewi-

dziany jest on w³aœciwie dla nowych en-

tuzjastów elektroniki, których mam

nadziejê nie zniechêci. Zaczyna jednak

trochê przypominaæ niekoñcz¹ce siê se-

riale telewizyjne. W przedostatniej czê-

œci przedstawiam wiadomoœci dotycz¹ce

pamiêci pó³przewodnikowych – istotne-

go elementu wielu urz¹dzeñ elektro-

nicznych.

Zadaniem pamiêci jest przechowy-

wanie informacji. W elektronice cyfro-

wej informacj¹ bêdzie stan napiêcia

okreœlaj¹cy stan logiczny. Uk³ady cyfro-

we przetwarzaj¹ i przechowuj¹ (pamiê-

taj¹) informacje w postaci binarnej

(0 – 1). Informacje przetwarzane musz¹

byæ wczeœniej zapamiêtane. Wynik prze-

twarzania tak¿e bêdzie zapamiêtany.

Uk³ady s³u¿¹ce do tego celu nazywane

s¹ rejestrami i s¹ istotnymi dla dzia³ania

mikroprocesorów i komputerów.

Pamiêci¹ bêdziemy nazywali wy-

dzielony uk³ad s³u¿¹cy do przechowy-

wania wiêkszej iloœci informacji. Ele-

mentarne informacje przechowywane

s¹ w tzw. komórkach pamiêci. Z pozna-

nych dotychczas elementów uk³adów

logicznych, najbardziej nadaj¹ siê do za-

pamiêtania stanu logicznego przerzutni-

ki bistabilne. Przyk³adem uk³adu pamiê-

ci jest rejestr przesuwny prezentowany

w poprzednim odcinku. Charaktery-

styczne dla niego jest wyprowadzanie

informacji w sposób szeregowy.

Istotnym zagadnieniem dotycz¹cym

pamiêci jest mo¿liwoœæ zapisania infor-

macji w okreœlonym miejscu jak i jej po-

branie. Wymaga to uporz¹dkowania

rozmieszczenia komórek i realizacji tzw.

adresowania, czyli wskazywania komór-

ki do zapisu lub odczytu informacji.

Pierwszym kryterium podzia³u pa-

miêci jest sposób wprowadzania i wy-

prowadzania danych. Mo¿e byæ on sze-

regowy lub równoleg³y. Z tym wi¹¿¹ siê

ró¿ne struktury pamiêci: szeregowa

i matrycowa.

Struktura szeregowa wystêpuje

w rejestrze przesuwnym. Do tego rodza-

ju pamiêci nale¿¹ tak¿e rejestry zbudo-

wane z elementów o tzw. sprzê¿eniu ³a-

dunkowym (CCD). Struktura matrycowa

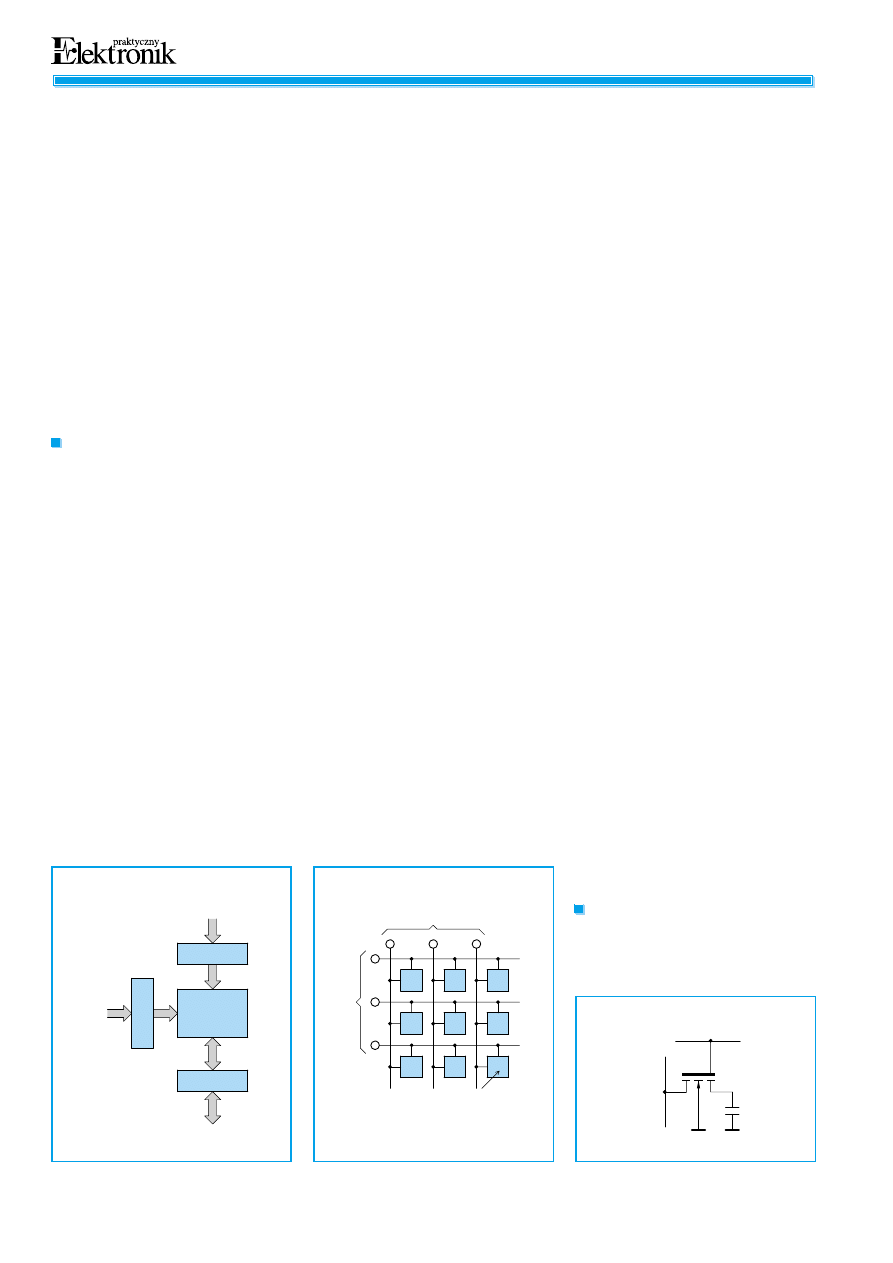

pokazana jest na rysunku 1.

Zasadniczym blokiem pamiêci ma-

trycowej jest matryca pamiêci zawiera-

j¹ca uporz¹dkowane komórki pamiêci.

Komórki te rozmieszczone s¹ na p³a-

szczyŸnie np. uk³adu scalonego i ich po-

³o¿enie mo¿na okreœliæ za pomoc¹

wspó³rzêdnych X i Y (rys. 2). Adres ko-

mórki sk³ada siê wiêc z dwóch czêœci.

Czêœæ X wybiera przez dekoder X wier-

sze (poziomo) w jakich rozmieszczone

s¹ komórki, a czêœæ Y przez dekoder Y

wybiera kolumny (pionowo). Dane s¹

wprowadzane lub wyprowadzane z pa-

miêci przez uk³ad we/wy.

Dostêp do komórek pamiêci z szere-

gowym wyprowadzaniem informacji

jest utrudniony i zale¿y od miejsca po³o-

¿enia komórki. Od miejsca po³o¿enia

komórki zale¿y czas uzyskania wiado-

moœci. Przy równoleg³ym wyprowadza-

niu wiadomoœci czas uzyskania informa-

cji nie zale¿y od umiejscowienia komór-

ki pamiêci.

Innym kryterium podzia³u jest mo¿-

liwoϾ wielokrotnego zapisu informacji

do pamiêci. St¹d bierze siê podzia³ na

pamiêci o dostêpie swobodnym RAM

i pamiêci tylko do odczytu ROM.

Pamiêæ RAM umo¿liwia wielokrotny

zapis i odczyt informacji podczas nor-

malnego dzia³ania. Gorzej jest z trwa³o-

œci¹ zapisanej informacji. Czêœæ pamiêci

RAM wymaga jej odœwie¿ania, a wszyst-

kie trac¹ zapisane dane po wy³¹czeniu

zasilania (wyj¹tek stanowi¹ tzw. nieulot-

ne pamiêci RAM).

Pamiêci ROM natomiast przecho-

wuj¹ zapisane informacje w sposób

trwa³y. Informacje te mo¿na wielokrot-

nie odczytywaæ. Zapis jest operacj¹ jed-

norazow¹ lub co najmniej utrudnion¹.

Do podstawowych parametrów pamiêci

nale¿¹:

– pojemnoœæ, okreœlaj¹ca maksymaln¹

iloœæ informacji (liczon¹ w bajtach lub

bitach), jaka mo¿e byæ przechowywa-

na w pamiêci;

– czas dostêpu, odstêp czasu od chwili

wystawienia adresu komórki pamiêci

do uzyskania danych na wyjœciu pa-

miêci (liniach danych);

– organizacja pamiêci, d³ugoœæ s³owa

zapisywanego w jednej komórce pa-

miêci (pod jednym adresem), liczona

w bitach. Czêsto podawana jest jako

iloczyn d³ugoœci s³owa i iloœci ko-

mórek.

Mo¿na podzieliæ na dwie zasadni-

cze grupy: pamiêci dynamiczne DRAM

i pamiêci statyczne SRAM.

Elektronika inaczej cz. 37 –

pamiêci pó³przewodnikowe

we/wy

Uk³ad we/wy

Matryca

Pamiêci

Dekoder X

Adres X

Dekoder Y

Adres Y

Rys. 1 Pamiêæ matrycowa

Struktura i podzia³ pamiêci

Komórka

Pamieci

X

Y

Rys. 2 Matryca pamiêci

Pamiêci RAM

Linia bitow

Linia s³owa

Rys. 3 Komórka pamiêci dynamicznej (1 bit)

21

2/99

Komórka pamiêci statycznej wyko-

rzystuje przerzutnik bistabilny. Do jego

realizacji w uk³adzie scalonym wymaga-

ne jest zastosowanie kilku tranzystorów.

Powoduje to doœæ du¿e wymiary komór-

ki i w efekcie zmniejsza pojemnoœæ mo¿-

liw¹ do uzyskania z okreœlonej po-

wierzchni uk³adu scalonego. Zalet¹ pa-

miêci statycznej jest utrzymywanie za-

wartoœci przez ca³y czas zasilania

bez koniecznoœci odœwie¿ania. Wad¹,

niestety wysoka cena i stosunkowa ma-

³a pojemnoœæ.

Pamiêci dynamiczne powsta³y dla

uzyskania tanich pamiêci o du¿ej po-

jemnoœci. Komórka takiej pamiêci wy-

korzystuje tylko jeden tranzystor (rys. 3).

Informacja zapamiêtywana jest w posta-

ci ³adunku elektrycznego (napiêcia) na

pojemnoœci.

Informacja podawana na liniê bi-

tów jest zapisywana w kondensatorze

C po podaniu napiêcia dodatniego na

liniê s³owa – bramkê tranzystora. Od-

czyt informacji z linii bitów nastêpuje

po podaniu napiêcia na liniê s³owa. Ma-

³a wartoœæ pojemnoœci (u³amki pF)

i up³ywnoœci powoduj¹ roz³adowanie

siê pojemnoœci i stopniow¹ utratê infor-

macji. Dla jej podtrzymania niezbêdne

jest tzw. odœwie¿anie Polega ono na cy-

klicznym odczycie komórek pamiêci.

Realizuje to zwykle specjalny uk³ad od-

œwie¿ania. Odœwie¿anie komplikuje ko-

rzystanie z pamiêci dynamicznej, ale

du¿e pojemnoœci przy niskich kosztach

s¹ istotnym atutem.

W³aœnie pamiêci dynamiczne stano-

wi¹ podstawow¹ pamiêæ RAM mikro-

komputerów. Nowoczesne pamiêci dy-

namiczne osi¹gaj¹ czasy dostêpu rzêdu

60 ns przy pojemnoœciach 64 Mb (me-

ga bitów). Pojemnoœci pamiêci RAM po-

daje siê zwykle w bitach (1 kb – 1024

bity, 1 Mb – 1024 kB). Zwiêksza siê czas

miêdzy kolejnymi odœwie¿eniami (kilka-

dziesi¹t ms). Specjalne sposoby wyko-

rzystania pamiêci tzw. synchronicz-

ne (SDRAM) pozwalaj¹ na obni¿enie

efektywnego czasu dostêpu. Modu³y

pamiêci SDRAM, nazywane DIMM pra-

cuj¹ z czêstotliwoœciami zegara ponad

100 MHz.

Pamiêci statyczne pocz¹tkowo po-

siada³y bardzo du¿e czasy dostêpu. Roz-

wój technologii pó³przewodników spra-

wi³, ¿e spad³y one do rzêdu 6 ns. Stoso-

wane s¹ do realizacji tzw. pamiêci CA-

CHE stanowi¹cych w mikrokomputerach

pomost miêdzy bardzo szybkim mikro-

procesorem i stosunkowo powoln¹ pa-

miêci¹ dynamiczn¹. Rozwi¹zanie to po-

dyktowane jest wysok¹ cen¹ i mniejszy-

mi pojemnoœciami pamiêci statycznych.

Uk³ady scalone pamiêci dynamicznych

posiadaj¹ zwykle organizacjê bitow¹

(1 bit). Pamiêci statycznych natomiast

bajtow¹ (do 8 Bajtów – 64 bity). Aktu-

alnie s¹ stosowane pamiêci dynamicz-

ne w formie modu³ów o organizacji

64 bitów.

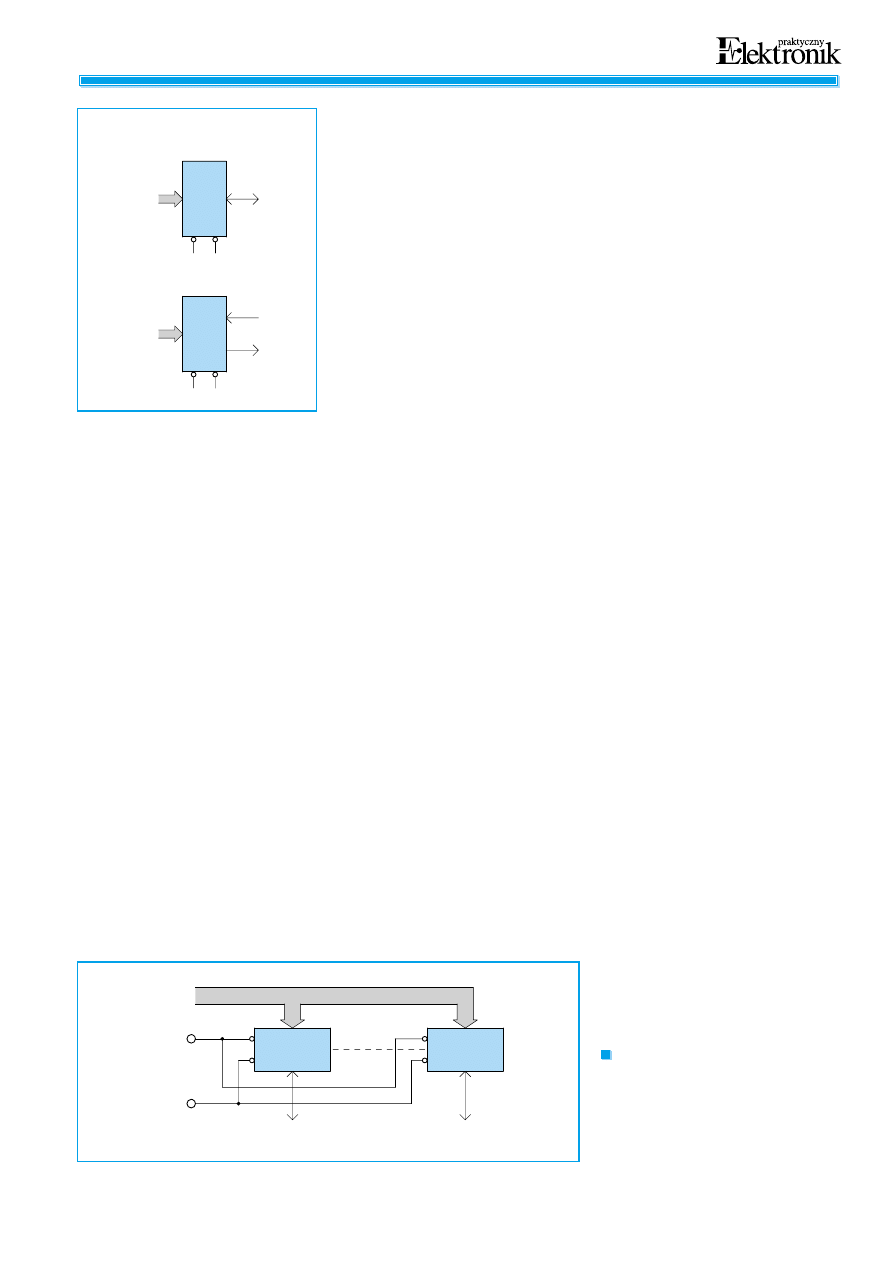

Do pamiêci RAM doprowadzany

jest adres, sygna³y steruj¹ce CE, R/W

(zapis W lub odczyt R) oraz dane (rys 4).

Adres, podawany liniami adresowymi

s³u¿y do wyboru komórki, do której zo-

stanie zapisana informacja lub ,z której

zostanie odczytana. Sygna³ steruj¹cy CE

uaktywnia pamiêæ, tzn. do³¹cza j¹ do li-

nii adresowych i danych. Mo¿e s³u¿yæ

do wyboru bloku pamiêci (tzw. strony).

Na strony mo¿e byæ podzielona du¿a

pamiêæ. Wtedy czêœæ linii adresowych,

za pomoc¹ dekodera adresów wybiera

blok pamiêci, a pozosta³e linie adreso-

we wybieraj¹ komórkê pamiêci. Istniej¹

pamiêci z dwukierunkow¹ lini¹ danych

lub z dwoma jednokierunkowymi (zapis–

odczyt). Iloœæ linii danych zale¿y od d³u-

goœci s³owa. Linie adresowe czêsto s¹

multipleksowane – najpierw podawany

jest adres wiersza a póŸniej kolumny.

Pozwala to przy ograniczonej iloœci wy-

prowadzeñ na zaadresowanie wiêkszej

iloœci komórek.

Powszechnie stosowane s¹ pamiêci

z dwukierunkow¹ lini¹ danych. Nowo-

czesne pamiêci z dwoma liniami jedno-

kierunkowymi umo¿liwiaj¹ jednoczesny

odczyt i zapis. Stosowane s¹ w kartach

graficznych mikrokomputerów jako tzw.

Video RAM (VRAM).

Pojedyncze uk³ady scalone pamiêci

mog¹ byæ ³¹czone w bloki o ¿¹danej

organizacji (d³ugoœci s³owa). Wejœcia

steruj¹ce i adresowe s¹ wtedy ³¹czone

równolegle. Rysunek 5 przedstawia w³a-

œnie blok pamiêci RAM o organizacji

8 bitowej i pojemnoœci 1 kB (1024 Baj-

ty, 1 Bajt – to 8 bitów).

Oddzieln¹ grupê pamiêci RAM

o w³aœciwoœciach zbli¿onych do pamiêci

ROM s¹ tzw. nieulotne pamiêci RAM.

Zazwyczaj s¹ to pamiêci statyczne,

których komórki mog¹ byæ zapisywane

wielokrotnie i ich zawartoϾ utrzymuje

siê nawet po wy³¹czeniu zasilania. Jed-

nym z przyjêtych oznaczeñ pamiêci nie-

ulotnych jest skrót NVRAM. Wykonywa-

ne s¹ tak¿e w wersjach z szeregowym

lub równoleg³ym wyprowadzaniem da-

nych. Wersja z szeregowym wyprowa-

dzaniem danych stosowana jest z tzw.

magistral¹ I

2

C do zapamiêtywania na-

staw w sprzêcie powszechnego u¿ytku

(wie¿e audio, telewizory itp.).

Pod tym pojêciem mieœci siê du¿a

ró¿norodnoœæ wersji pamiêci sta³ych,

³¹cznie z pamiêciami elektrycznie kaso-

wanymi. Charakterystyczn¹ cech¹ pa-

miêci ROM jest ewentualna mo¿liwoœæ

kasowania ca³ej jej zawartoœci. Pamiêæ

D0

R/W

Dane

CE

DI

Adres

b)

R/W

CE

Dane

DI/O

Adres

a)

Rys. 4 Pamiêci RAM

D7

D0

Wybór

bloku

Odczyt

Zapis

DI/0

CE

R/W

R/W

CE

DI/0

A0÷A9

Rys. 5 Blok Pamiêci RAM o organizacji 8 bitowej

Pamiêci ROM

22

2/99

RAM pozwala na modyfikacjê zawarto-

œci dowolnej komórki przy zachowaniu

zawartoœci innych komórek.

Jedna z wersji pamiêci ROM progra-

mowana jest w procesie produkcyjnym

u producenta pamiêci. Przy produkcji

uk³adów scalonych u¿ywa siê tzw. masek

(szablonów) i jedna z masek zawiera w³a-

œnie rozmieszczenie informacji, które

w sposób trwa³y s¹ zapisywane we wnê-

trzu uk³adu scalonego. St¹d pochodzi

okreœlenie pamiêci programowanych

mask¹, które tak¿e nazywane s¹ pamiê-

ciami ROM. Wykonywane s¹ w technolo-

gii MOS, a zapis informacji polega

na zmianie gruboœci izolacji miêdzy

bramk¹ a kana³em. Osi¹gaj¹ pojemnoœci

rzêdu 1 Mb.

Kolejna wersja umo¿liwia jednokrot-

ny zapis informacji bez mo¿liwoœci skaso-

wania i modyfikacji zawartoœci komórek.

Programowanie mo¿e byæ zrealizowane

przez u¿ytkownika z wykorzystaniem

specjalnego programatora. Polega na

przepalaniu pr¹dem siatki delikatnych

po³¹czeñ. Odmiana ta nazywana jest pa-

miêci¹ PROM. Wykonywane s¹ w tech-

nologii bipolarnej, czemu zawdziêczaj¹

du¿¹ szybkoœæ (ma³y czas dostêpu) ale

jednoczeœnie charakteryzuj¹ siê ma³¹ po-

jemnoœci¹.

Pamiêci EPROM podobnie jak po-

przednie mog¹ byæ programowane przez

u¿ytkownika. Ich istotn¹ cech¹ jest mo¿-

liwoœæ skasowania zawartoœci komórek

i ich ponowne zaprogramowanie. Kaso-

wanie pamiêci EPROM odbywa siê przez

naœwietlenie promieniami ultrafioleto-

wymi. Proces ten jest nieco uci¹¿liwy ze

wzglêdu na d³ugi czas naœwietlania pod-

czas kasowania (10÷30 min). Podstawo-

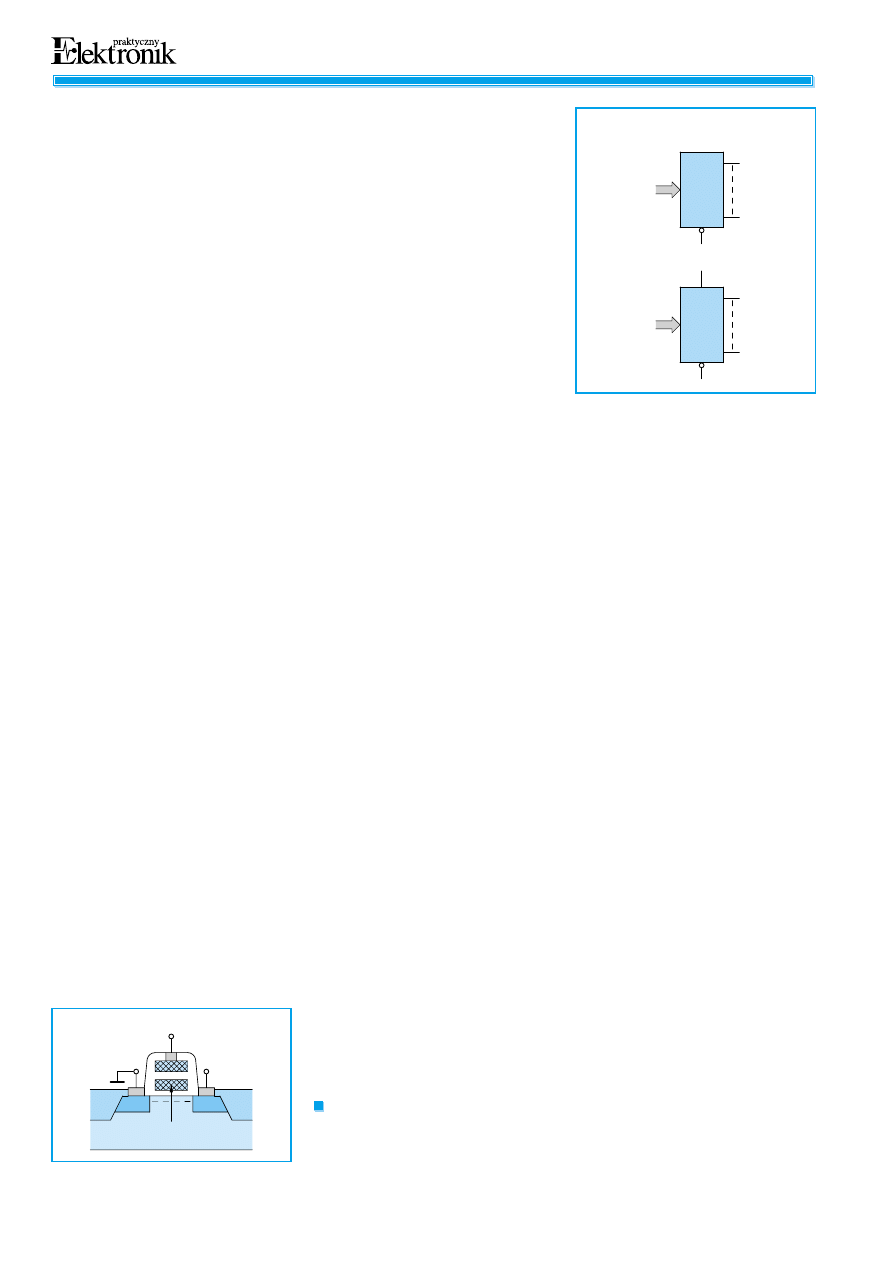

wym elementem komórki pamiêci

EPROM jest tranzystor polowy MOS z do-

datkow¹ tzw. swobodn¹ bramk¹.

Tranzystor ten posiada dwie bramki

polikrzemowe, z których jedna posiada

wyprowadzenie a druga tzw. swobodna

nie jest po³¹czona(rys. 6). Bramka swo-

bodna mo¿e jednak zostaæ na³adowana

w sposób trwa³y przy odpowiednim na-

piêciu na drenie i bramce podczas pro-

gramowania.

£adunek

elektryczny

bramki swobodnej decyduje o zachowa-

niu siê tranzystora jako przewodz¹cego

(0 logiczne) lub nieprzewodz¹cego (1).

Naœwietlanie ultrafioletem wyrównuje

³adunki wszystkich bramek swobodnych

czyli kasuje zapisan¹ informacjê. Charak-

terystyczn¹ cech¹ pamiêci EPROM jest

przezroczyste okienko do kasowania. Po-

jemnoœci osi¹gaj¹ rz¹d 1 Mb. Czasy do-

stêpu s¹ du¿e – rzêdu setek ns.

Postêpem w dziedzinie pamiêci sta-

³ych

by³o

wprowadzeni

pamiêci

EEPROM i EAROM. Pierwsze posiadaj¹

mo¿liwoœæ kasowania elektrycznego,

przy czym mo¿liwe jest stopniowe skaso-

wanie ca³ej zawartoœci. Drugie umo¿li-

wiaj¹ kasowanie selektywne czêœci za-

wartoœci. Kasowanie zawartoœci polega

na wpisaniu nowej wartoœci np. 0 do

wszystkich komórek – wymaga jednak

te¿ doœæ d³ugiego czasu. Wad¹ tej grupy

pamiêci jest du¿y czas dostêpu.

Ostatnio na znaczeniu zyskuje nowa

grupa pamiêci sta³ych tzw. FLASH ROM.

Pamiêci te posiadaj¹ mo¿liwoœæ szybkie-

go skasowania ca³ej zawartoœci jednym

impulsem elektrycznym. Powszechnie

stosowane s¹ one jako pamiêci sta³e mi-

krokomputerów tzw. BIOS, co pozwala

na jego uaktualnianie. Wyposa¿ane s¹

w nie najnowsze wersje mikrokompute-

rów jednouk³adowych. Osi¹gaj¹ pojem-

noœci 2 MB przy czasie dostêpu 100 ns.

Uk³ady scalone pamiêci ROM posia-

daj¹ najczêœciej organizacjê bajtow¹, co

oznacza d³ugoœæ s³owa wynosz¹c¹ 8 bi-

tów. przyk³adowe symbole pamiêci

ROM przedstawia rys. 7.

Do pamiêci ROM (PROM i EPROM)

doprowadzone s¹ linie adresowe, sygna³

steruj¹cy CS i wyprowadzone linie da-

nych o iloœci zale¿nej od d³ugoœci s³owa.

Nie ma tu sygna³ów zapis/odczyt, ponie-

wa¿ s¹ to pamiêci tylko do odczytu. Sy-

gna³ CS s³u¿y do uaktywniania pamiêci

czyli do pod³¹czania jej wyjœæ do linii da-

nych. Jest to równowa¿ne odczytowi da-

nych z pamiêci sta³ej (ROM). Pamiêæ

EPROM posiada dodatkowe wypro-

wadzenie s³u¿¹ce do do³¹czania napiê-

cia zasilaj¹cego przy programowaniu

(PGM).

Dotyczy oznaczeñ uk³adów scalonych

pamiêci. Panuje w tej dziedzinie du¿a ró¿-

norodnoœæ zale¿nie od upodobañ produ-

centa. Mo¿na dopatrzyæ siê pewnych

cech wspólnych. Pocz¹tek oznaczenia to

grupa 2÷3 liter okreœlaj¹ca producenta,

zastosowanie pamiêci (cywilne – militar-

ne), zakres temperatur otoczenia. najwa¿-

niejsze jest oznaczenie cyfrowe, poniewa¿

zawiera zwykle pojemnoœæ pamiêci.

W przypadku pamiêci dynamicz-

nych RAM zawiera ono organizacjê (d³u-

goœæ s³owa) i iloœæ s³ów wyra¿on¹

w k (kilo s³owach - 1024). Kolejne cyfry

oznaczaj¹ najczêœciej czas dostêpu. Np.

4164-150, to pamiêæ o organizacji 1 bit,

zawieraj¹ca 64 kilo s³owa 1 bitowe czyli

64 kb. Czas dostêpu wynosi 150 ns. In-

ne oznaczenie: 44256-70, to pamiêæ

o organizacji 4 b, zawieraj¹ca 256 kilo

s³ów (1 Mb) i czasie dostêpu 70 ns. Tru-

dniej jest rozszyfrowaæ parametry modu-

³ów pamiêci, zw³aszcza popularnych

modu³ów DIMM. Przeciêtny u¿ytkownik

musi zdaæ siê na informacje sprzedawcy.

Nie podaje siê dla nich czasów dostêpu

a jedynie czêstotliwoœæ zegara: 66 MHz

(LX) lub 100 MHz (BX). Oznaczenia lite-

rowe LX i BX pochodz¹ od oznaczeñ tzw.

chip setów produkcji firmy Intel i stoso-

wanych w mikrokomputerach PC.

Oznaczenie pamiêci ROM zawiera

najczêœciej zaszyfrowany numer uzgo-

dniony miêdzy producentem i zamawia-

j¹cym. W oznaczeniu pamiêci EPROM

znajduje siê pojemnoœæ wyra¿ona w kb.

Domyœlaæ siê trzeba organizacji bajtowej

i czasu dostêpu. Przyk³adowo 2732 to

oznaczenie pamiêci EPROM o pojemnoœci

32 kb lub 4 kB, wykonanej w technologii

MOS. Wykonanie w technologii CMOS za-

wiera dodatkowo literê C - 27C32.

à Ci¹g dalszy w nastêpnym numerze.

bramka

swobodna

Pod³o¿e p

Si02

D

+

n+

S

n+

G

Rys. 6 Komórka pamiêci EPROM

CS

Dane

D7

EPROM

PGM

D0

Adres

b)

D7

CS

D0

Dane

Adres

PROM

a)

Rys. 7 Pamiêci ROM

Oznaczenia pamiêci

23

2/99

Wyszukiwarka

Podobne podstrony:

pamieci polprzew

127 Pamięci półprzewodnikowe

01 Podstawowe informacje o pamięciach półprzewodnikowychid 2695 ppt

Pamięci półprzewodnikowe

Pamięci półprzewodnikowe, Szkoła, Systemy Operacyjnie i sieci komputerowe, utk, semestr I

Budowa i zasada działania pamięci półprzewodnikowych

pamieci polprzew

01 Podstawowe informacje o pamięciach półprzewodnikowychid 2695 ppt

03 Odświeżanie pamięci DRAMid 4244 ppt

wykład 12 pamięć

8 Dzięki za Pamięć

06 pamięć proceduralna schematy, skrypty, ramyid 6150 ppt

więcej podobnych podstron