Radioelektronik Audio-HiFi-Video 11/2001

Realizacja uk³adu steruj¹cego mo¿e byæ

ró¿na, zale¿na od mo¿liwoci jakimi dyspo-

nujemy oraz celu jaki chcemy osi¹gn¹æ.

Mo¿liwe s¹ zatem nastêpuj¹ce warianty

rozwi¹zañ:

1. wykorzystuj¹c uk³ady scalone klasy TTL

i inne elementy pó³przewodnikowe,

2. podobnie jak wariant 1 ale z uk³adami kla-

sy MOS (MIS) np. z serii 4xxx,

3. zastosowaæ mikroprocesor z pamiêci¹,

np. z rodziny 8051 lub inny,

4. wykorzystaæ komputer a konkretnie jego

np. wyjcie równoleg³e LPTx _ programuj¹c

s³owo 6-bitowe. Do tego celu dodatkowo

potrzebny jest specjalny uk³ad sprzêgaj¹cy

mocy (interfejs).

Rozwi¹zañ jest wiele i zale¿¹ od parame-

trów falownika, g³ównie jego napiêcia, mo-

cy oraz zakresu zmian czêstotliwoci.

Oprócz tego istniej¹ sposoby poprawia-

nia sinusoidy, zachowania siê falownika

przy zasilaniu odbiorników o charakterze

reaktancyjnym itd.

FALOWNIK TRÓJFAZOWY

(2)

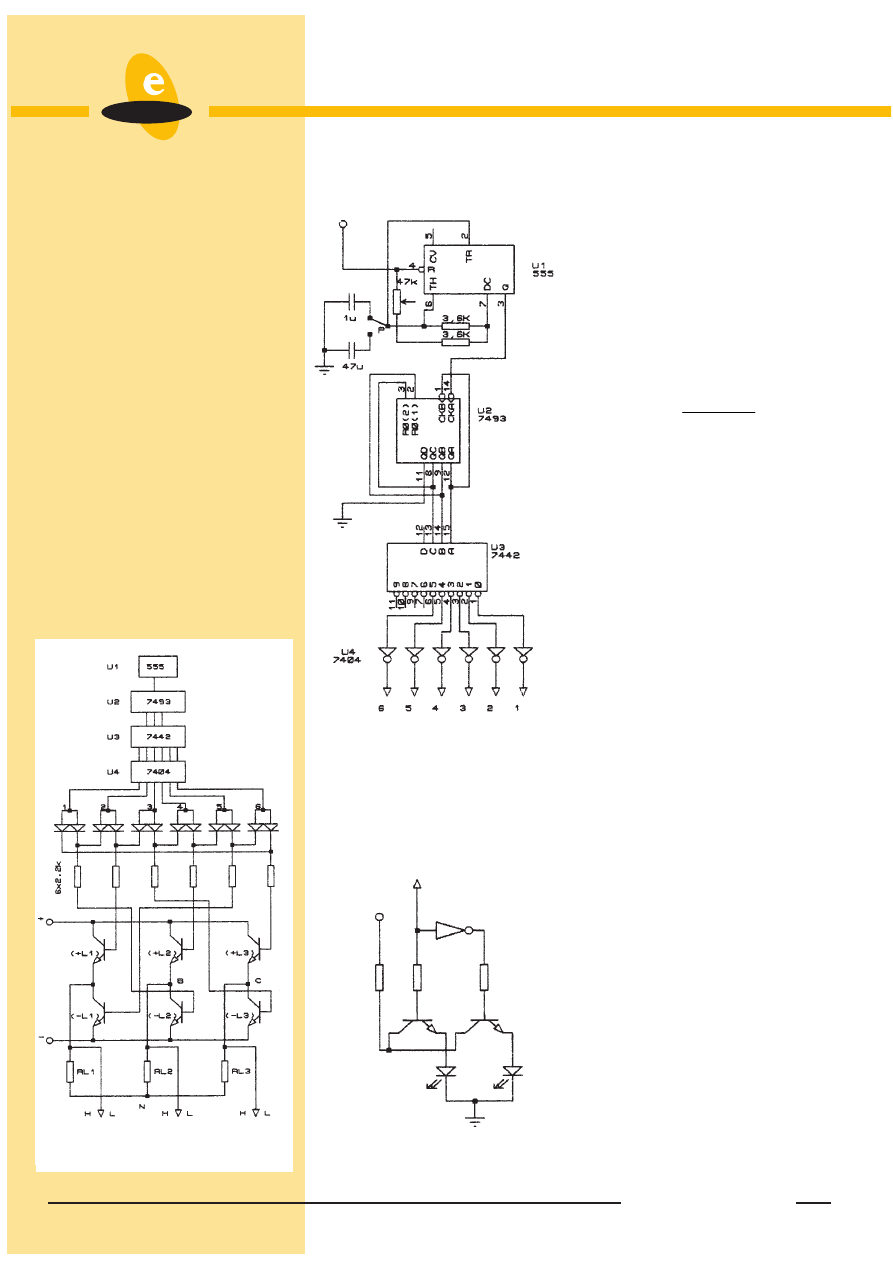

Przyst¹pmy zatem do rozwi¹zania pierwsze-

go wariantu zak³adaj¹c dla uproszczenia, ¿e

napiêcie zasilania równe 5 V bêdzie wspól-

ne dla obwodu steruj¹cego jak i roboczego

(dla obwodu roboczego powinno byæ wy-

¿sze). G³ównym elementem uk³adu steruj¹-

cego bêdzie licznik binarny zliczaj¹cy do

6. (modulo 6) oraz dekoder 1 z 6. Schemat

blokowy 3-fazowego falownika ze zmienn¹

czêstotliwoci¹ wraz z uk³adem do formowa-

nia impulsów przedstawiono na rys. 12.

Uk³ad do formowania impulsów przedsta-

wiono na rys. 13. Uk³ad U1 (555) generuje

impulsy prostok¹tne, których czêstotliwoæ

zale¿y od RC. Czêstotliwoæ generatora

opisuje wzór:

w którym:

R

a

_ rezystancja w³¹czona miêdzy koñ-

cówkê 7 a Ucc,

R

b

_ rezystancja w³¹czona miêdzy koñ-

cówki 6 i 7,

C _ kondensator zwieraj¹cy koñcówki 6 i 2

do masy.

Czêstotliwoæ generatora mo¿na zmieniaæ

skokowo przez zmianê pojemnoci prze-

³¹cznikiem P. Liczba stopni mo¿e byæ dowol-

na. Istnieje równie¿ mo¿liwoæ zmian czêsto-

tliwoci p³ynnie _ potencjometrem. Zarów-

no kondensatory jak i rezystory nie s¹ kry-

tyczne. Impulsy prostok¹tne s¹ doprowa-

dzane do licznika U2 (7493), do k. 14. Dwie

pêtle sprzê¿enia zwrotnego, QC z RO(2)

i QB z RO(1), tworz¹ licznik zliczaj¹cy do

szeciu. (modulo 6). Licznik U2 (7493) zasi-

la dekoder U3 (7424), na którego wyjciach

pojawiaj¹ siê kolejno stany niskie (L). Do

wyzwalania tranzystorów n-p-n potrzebny

jest impuls dodatni kierowany do baz, st¹d

potrzeba zastosowania inwerterów U4

(7404). W ten sposób na wyjciach inwerte-

rów kolejno od 1 do 6, bêd¹ siê pojawiaæ im-

pulsy dodatnie.

Wyjcia inwerterów 1, 2, 3, 4, 5 i 6 ³¹czymy

z takimi samymi wejciami matrycy diodo-

wej (rys. 12). Do wyjæ falownika A,

B i C mo¿na do³¹czyæ oscyloskop lub prób-

nik stanów logicznych, który w przypadku

ma³ych czêstotliwoci umo¿liwia wizualn¹

obserwacjê w³¹czania poszczególnych tran-

zystorów. Próbnik, np. dla fazy L1, mo¿e

byæ zrealizowany jak na rys. 14. Dla pozo-

sta³ych faz podobnie. W próbniku zastoso-

wano tranzystory n-p-n. Je¿eli na wejciu in-

wertera (wyjcie fazy L1) pojawi siê np. stan

wysoki (H), tranzystor T1 wejdzie w stan

przewodzenia, zawieci siê dioda D1 sy-

gnalizuj¹c stan wysoki (H). W tym czasie na

wyjciu inwertera bêdzie stan niski (L), wiêc

f

Ra

R C

b

=

+

144

2

,

(

)

Rys. 12. Schemat falownika 3-fazowego

Rys. 13. Uk³ad do formowania impulsów

Rys. 14. Próbnik stanów logicznych

Generator taktuj¹cy

(Multiwibrator

astabilny)

Licznik modulo 6

Dekoder 1 z 6

Inwertery

Wejcia do 3-fazowego odbiornika

(wskaników stanów logicznych, oscyloskopu)

L1

H L

120 2,2 K 2,2 K

T1 T2

D1 D2

Matryca diodowa

Przekanik

Wejcie do matrycy diodowej

Ucc

19

r

tranzystor T2 bêdzie w stanie blokowania

i dioda D2 nie bêdzie wieciæ. Takich prób-

ników musi byæ trzy, jeden dla jednej fazy.

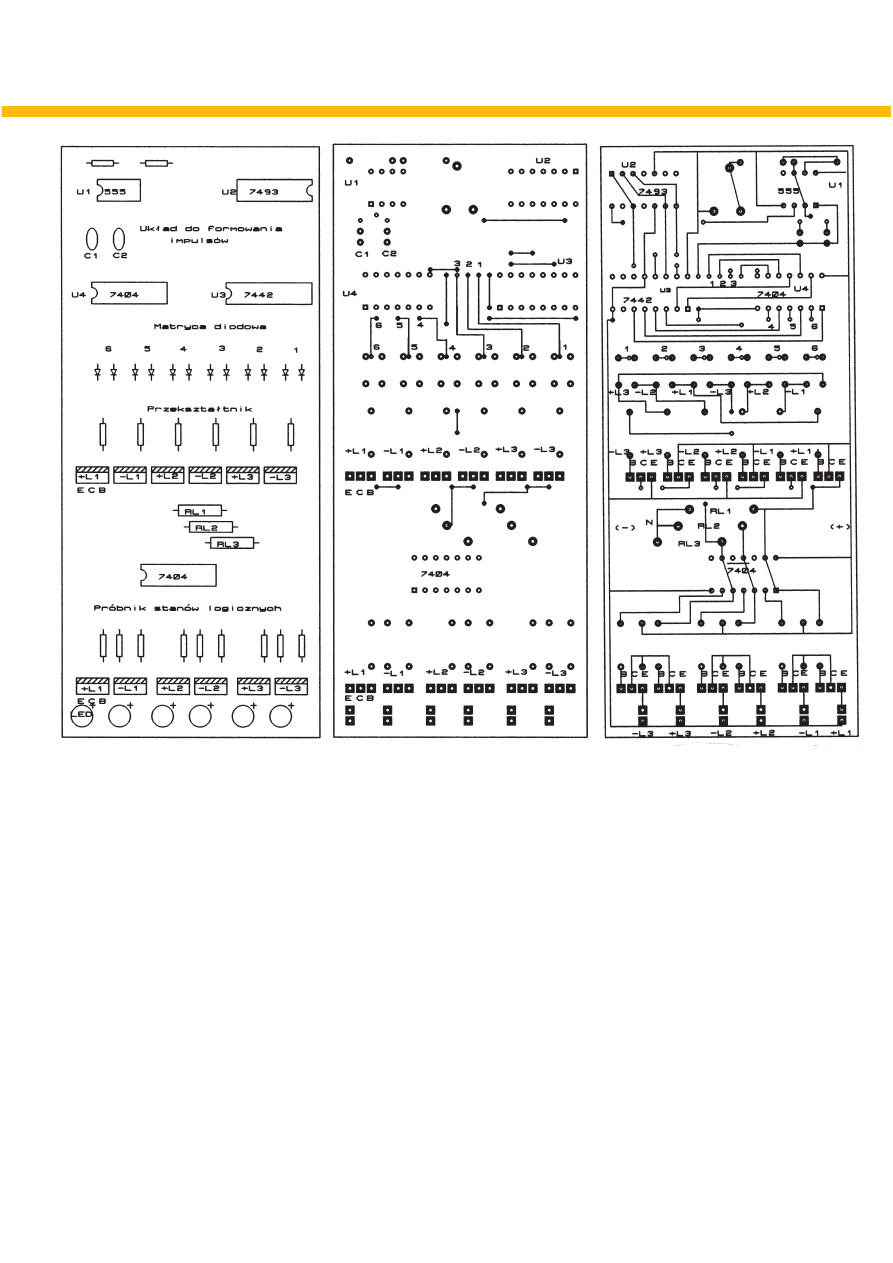

P³ytkê drukowan¹ falownika zaprojektowa-

no ³¹cznie z 3-fazowym próbnikiem stanów

Rys. 15. Rozmieszczenie elementów

Rys. 16. P³ytka drukowana skala 1:1

(widok od strony elementów)

Rys. 17. P³ytka drukowana skala 1:1

(widok od strony druku)

logicznych, który zaczyna siê od nienume-

rowanego inwertera 7404.

W zwi¹zku z tym, ¿e próbnik nie stanowi in-

tegralnej czêci falownika, mo¿na go nie

montowaæ.

Na rys. 15 przedstawiono rozmieszczenia

elementów falownika na p³ytce. Natomiast

na rys. 16 przedstawiono widok p³ytki od

strony elementów, a na rys. 17 _ od strony

druku.

n

Bogus³aw Jaroszczak

Wyszukiwarka

Podobne podstrony:

2001 11 29

2001 04 18

labirynt 8 11 18

2001 11 08 2162

2001 11 Szkoła konstruktorów klasa II

Egzamin Zobowiazania (11 18) id Nieznany

2001 04 18 0750

2001 11 25 wycena akcji, FCFF, FCFF, dźwignie finansowe, progi rentowności

2001 11 16

2001 11 22

NAUKA 4 2010 11 18

4, 11, 18

2010 11 18 patomorfologia

Anatomia 10 11 18

2001 03 18

2001 11 22 kol 1

11 18

2001 11 20

więcej podobnych podstron