C

C

e

e

c

c

h

h

y

y

a

a

r

r

c

c

h

h

i

i

t

t

e

e

k

k

t

t

u

u

r

r

y

y

v

v

o

o

n

n

N

N

e

e

u

u

m

m

a

a

n

n

n

n

a

a

1. Wspólna pamięć do przechowywania zarówno rozkazów jak

i danych.

2. Pamięć jednowymiarowa, złożona z kolejno ponumerowanych

komórek o jednakowej wielkości.

3. Brak

jawnego

rozróżniania rozkazów i danych.

4. Brak jawnej specyfikacji typów danych.

5. Praca sekwencyjna - przed rozpoczęciem wykonywania kolejnego

rozkazu musi zostać zakończone wykonywanie rozkazu

chronologicznie poprzedniego. Każdy rozkaz określa jednoznacznie

adres następnego.

S

S

c

c

h

h

e

e

m

m

a

a

t

t

b

b

l

l

o

o

k

k

o

o

w

w

y

y

m

m

i

i

k

k

r

r

o

o

k

k

o

o

m

m

p

p

u

u

t

t

e

e

r

r

a

a

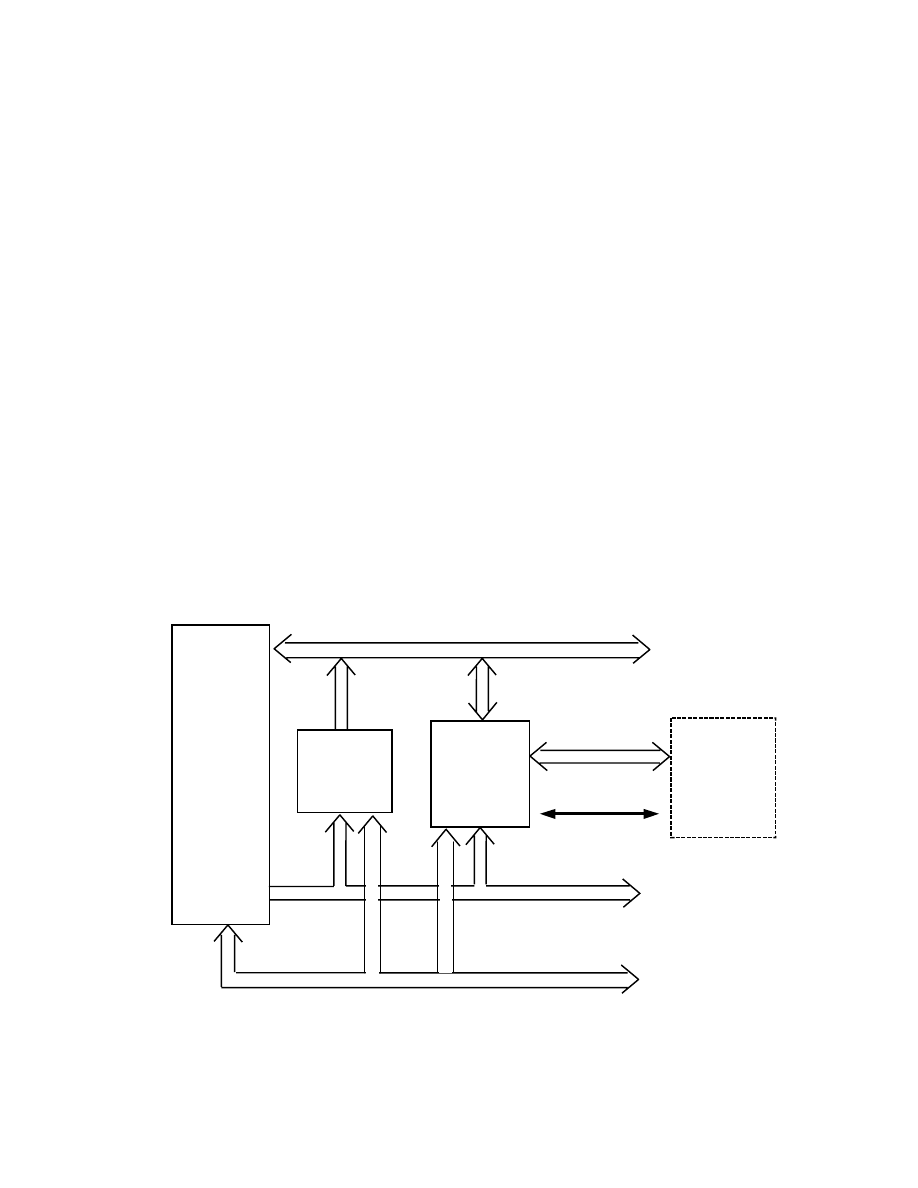

Mikro-

procesor

Pamięć

operacyj

Urządzeni

a wej/wyj

Progra-

mowane

układy

Szyna adresowa

Szyna danych

Szyna sterowania

Szyna wej/wyj

Sterowanie

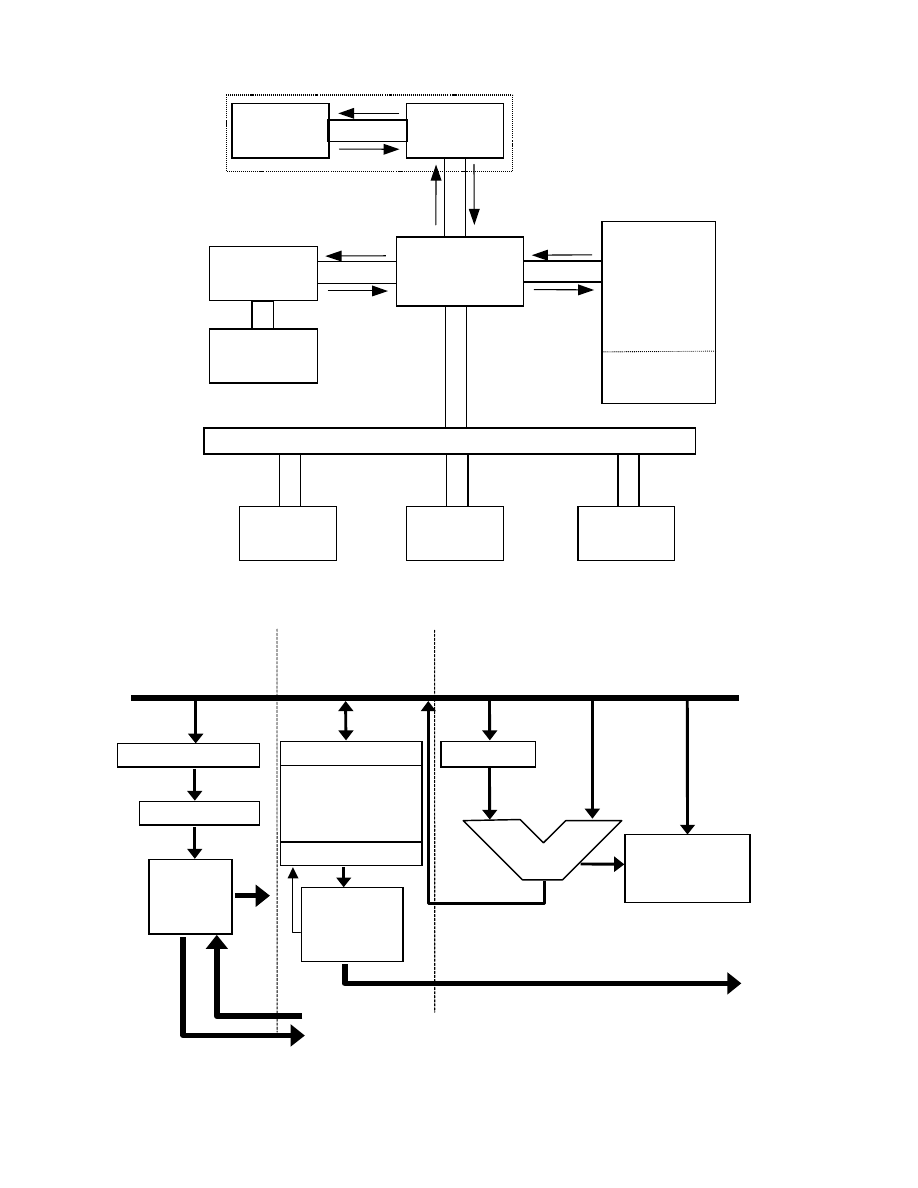

Przykładowa struktura systemu z magistralą AGP

Podstawowe zespoły funkcjonalne mikroprocesora

Intel

440 BX

L2

Cache

800 MB/s

Core

1,6 GB/s

Pentium II

800 MB/s

Pamięć

operacyjna

Tekstury

528 MB/s

AGP

Akcelerator

grafiki

Pamięć

karty

132 MB/s

PCI

Wej/wyj

Wej/wyj

Wej/wyj

Szyna sterowania

Rejestr instrukcji

Dekoder

Układ

sterujący

Multiplekser

Licznik rozkazów

Zespół rejestrów

ogólnego

przeznaczenia

Układ

realizujący

operację

±±±±

1

Akumulat

ALU

Szyna danych

Układ arytmetyczno-logiczny (ALU)

Zespół

rejestrów

Rejestr rozkazów,

dekoder i układ

sterujący

Szyna adresowa

Rejestr bitów

warunków

(znaczników)

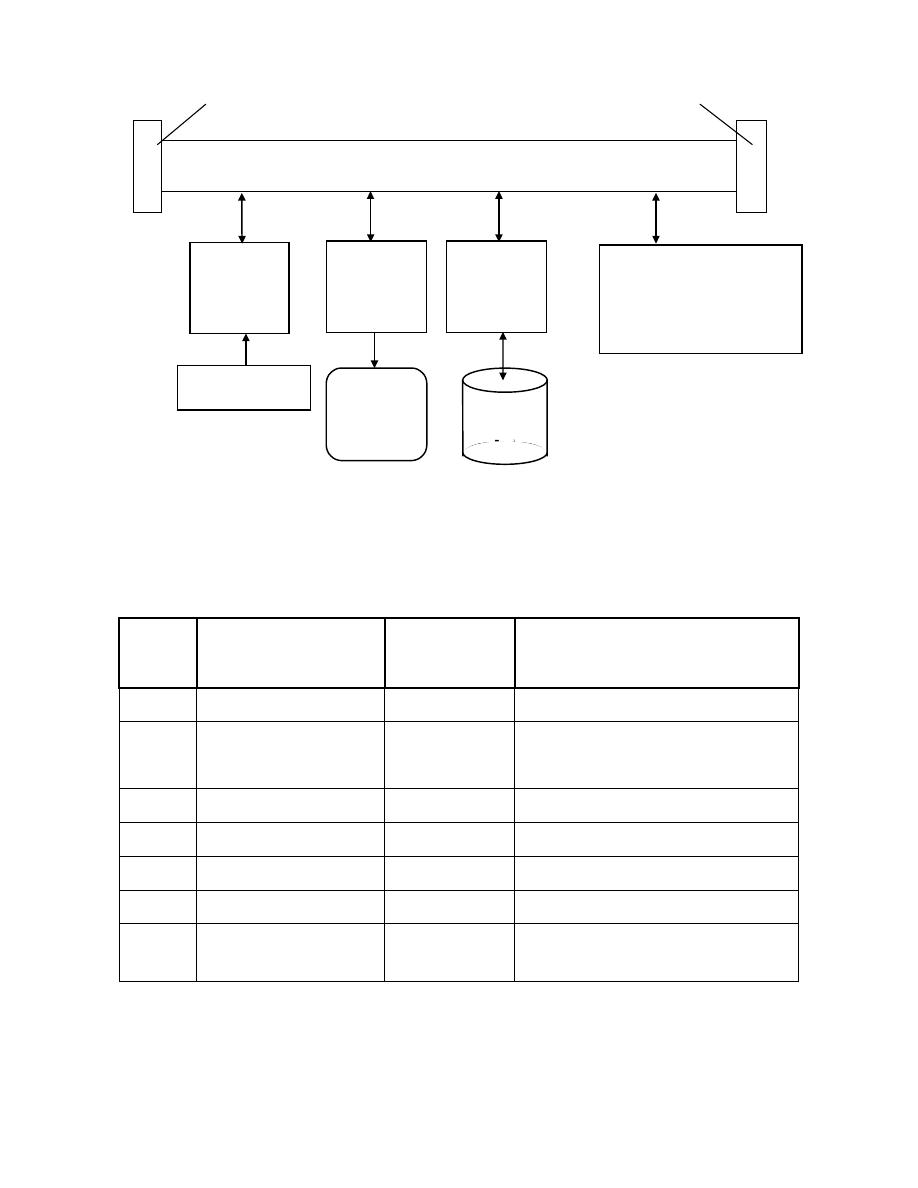

System z interfejsem typu "wspólna szyna"

Typy szyn

Typ

Szyny

Szybkość transmisji

lub szerokość pasma

Szerokość

szyny

Możliwość podłączenia

ISA

2,5 MB/s, 8 MHz

16 bitów

Wszystkie rodzaje kart rozszerzających.

Local

Bus

132 MB/s, 33 MHz

32 bity

Głównie karty graficzne i kontrolery

HDD.

PCI

132 MB/s, 33 MHz

32 bity

Wszystkie rodzaje kart rozszerzających.

PCI 2.1

264 MB/s, 33 MHz

64 bity

Wszystkie rodzaje kart rozszerzających.

VMC

130 MB/s

16 i 32 bity

Karty graficzne i video.

VAFC

150 MB/s

0d 8 do 32 bitów Karty graficzne i video.

AGP

266 MB/s lub 532 MB/s, 66

MHz / 100 MHz

32 bity (128

bitów)

Karty graficzne i video.

Magistrala systemowa we / wy

ADAPTER

ADAPTER

ADAPTER

KLAWIATURA

MONITOR

DYSK

TERMINATOR TERMINATOR

MIKROPROCESOR

Tabelka obrazująca tryby działania magistrali AGP:

AGP 1x

Podwojenie prędkości w porównaniu z PCI w wyniku podwojenia

częstotliwości magistrali. Należy pamiętać, że podwojenie dotyczy

wartości maksymalnych, w praktyce wyniki są niższe.

AGP 2x

W porównaniu z trybem 1x do przesyłania danych wykorzystuje się

również opadające zbocze sygnału zegara, co daje nam maksymalną

przepustowość na poziomie 528 MB/s. To czy karta będzie pracować

w trybie 2x zależy od producenta i modelu. Tak jak w poprzednim

wypadku 528 to wynik maksymalny.

AGP 4x

Ten dość przyszłościowy tryb przełamuje barierę 528 MB/s dzięki

zwiększeniu częstotliwości magistrali AGP z 66 na 100 MHz. Pozwala

to na osiągnięcie przesyłów rzędu 800 MB/s.

P

P

o

o

d

d

z

z

i

i

a

a

ł

ł

p

p

a

a

m

m

i

i

ę

ę

c

c

i

i

p

p

ó

ó

ł

ł

p

p

r

r

z

z

e

e

w

w

o

o

d

d

n

n

i

i

k

k

o

o

w

w

y

y

c

c

h

h

Przykładowa organizacja pamięci w systemie mikroprocesorowym

Pamięci półprzewodnikowe

stosowane w systemach

mikroprocesorowych

Pamięci o dostępie

bezpośrednim (RAM)

Pamięci stałe

NV SRAM

SRAM

SD RAM

FPM RAM

EDO RAM

BEDO RAM

Dynamiczne

Statyczne

Pamięci programowane

przez producenta

(ROM)

Pamięci programowane

jednokrotnie (PROM)

Pamięci programowane

wielokrotnie

(EPROM) i (E

2

PROM)

RD RAM

1

D0...D7

Bank pamięci

zawierający mniej

znaczące bajty

Układ wyboru

banku pamięci

Dekoder adresów

A1...A19

2

D8...D15

Bank pamięci

zawierający

bardziej znaczące

bajty

Multipleksowana

szyna adresów i

danych

AD8...AD15

AD0...AD7

BHE

A1...A19

A1...A19

A0

Układ wyboru

banku pamięci

Dekoder adresów

A1...A19

G

G

e

e

n

n

e

e

r

r

a

a

c

c

j

j

a

a

a

a

d

d

r

r

e

e

s

s

u

u

f

f

i

i

z

z

y

y

c

c

z

z

n

n

e

e

g

g

o

o

∑

Przemieszczenie

0 0 0 0

Segment

0 0 0 0

Adres efektywny

Adres bazowy segmentu

0

0

15

15

Adres fizyczny

20 bitowy

0

7

8

15

0

15

IP

Rejestry adresowe

Wskaźnik rozkazu

SP

Wskaźnik wierzchołka stosu

BP

Wskaźnik bazy

SI

Indeks źródła

DI

Indeks celu

Rejestry segmentowe

0

15

CS

Segment kodu programu

SS

Segment stosu

DS

Segment danych

ES

Segment dodatkowy

0

15

F

Rejestr znaczników (flag)

AH

AX

AL

BH

BX

BL

CH

CX

CL

DH

DX

DL

Rejestry ogólnego przeznaczenia

Akumulator

Rejestr bazowy

Rejestr zliczający

Rejestr danych

R

R

e

e

j

j

e

e

s

s

t

t

r

r

y

y

o

o

g

g

ó

ó

l

l

n

n

e

e

g

g

o

o

p

p

r

r

z

z

e

e

z

z

n

n

a

a

c

c

z

z

e

e

n

n

i

i

a

a służą głównie do przechowywania wyników

pośrednich, ich zawartości mogą być argumentami większości rozkazów:

A

A

X

X

-

-

a

a

k

k

u

u

m

m

u

u

l

l

a

a

t

t

o

o

r

r -

niektóre rozkazy dotyczące tego rejestru wykonują się szybciej niż

na innych rejestrach ogólnych lub są o 1 bajt krótsze.

B

B

X

X

-

-

r

r

e

e

j

j

e

e

s

s

t

t

r

r

b

b

a

a

z

z

o

o

w

w

y

y -

dodatkowo może być wykorzystany do tzw. adresowania

bazowego - zawiera wówczas przesunięcie (OFFSET) argumentu.

C

C

X

X

-

-

r

r

e

e

j

j

e

e

s

s

t

t

r

r

z

z

l

l

i

i

c

c

z

z

a

a

j

j

ą

ą

c

c

y

y lub

l

l

i

i

c

c

z

z

n

n

i

i

k

k

o

o

w

w

y

y -

może być wykorzystywany w rozkazach jako

licznik wykonań - jest wówczas zmniejszany o 1 za każdym wykonaniem i jego

zawartość podlega badaniu, czy nie uległa wyzerowaniu.

D

D

X

X

-

-

r

r

e

e

j

j

e

e

s

s

t

t

r

r

d

d

a

a

n

n

y

y

c

c

h

h -

jako jedyny może być wykorzystywany do adresowania

obiektów w przestrzeni adresowej wej/wyj (portów) w rozkazach wej/wyj, a także

w rozkazach o argumentach lub wynikach długości większej niż jedno słowo (np.

rozkazy mnożenia lub dzielenia).

R

R

e

e

j

j

e

e

s

s

t

t

r

r

y

y

a

a

d

d

r

r

e

e

s

s

o

o

w

w

e

e

służą głównie do przechowywania adresów względnych

(OFFSET), chociaż mogą być też wykorzystywane jako rejestry robocze :

I

I

P

P

-

-

w

w

s

s

k

k

a

a

ź

ź

n

n

i

i

k

k

r

r

o

o

z

z

k

k

a

a

z

z

u

u

(ang. instruction pointer), zawiera zawsze adres względny

(względem początku segmentu określonego przez zawartość rejestru CS) aktualnie

pobieranego do wykonania rozkazu, rejestr ten stanowi z punktu widzenia

programisty (wraz z rejestrem CS) część licznika rozkazów; rejestr IP nie może

być zmieniany przez program.

S

S

P

P

-

-

w

w

s

s

k

k

a

a

ź

ź

n

n

i

i

k

k

w

w

i

i

e

e

r

r

z

z

c

c

h

h

o

o

ł

ł

k

k

a

a

s

s

t

t

o

o

s

s

u

u -

zwykle zawiera adres względny (względem

początku segmentu określonego przez zawartość rejestru SS) wierzchołek stosu,

tzn. adres ostatniego słowa odłożonego na stosie.

B

B

P

P

-

-

r

r

e

e

j

j

e

e

s

s

t

t

r

r

w

w

s

s

k

k

a

a

ź

ź

n

n

i

i

k

k

a

a

b

b

a

a

z

z

y

y

- zwykle zawiera adres względny (względem początku

segmentu określonego przez zawartość rejestru SS) parametrów odłożonych na

stosie (dla procedur w językach wysoko poziomowych); rejestr BP może być

wykorzystany także do innych celów.

S

S

I

I

-

-

r

r

e

e

j

j

e

e

s

s

t

t

r

r

i

i

n

n

d

d

e

e

k

k

s

s

u

u

ź

ź

r

r

ó

ó

d

d

ł

ł

a

a

(miejsca, z którego pobierane są dane w operacjach

przesyłania danych) - zwykle zawiera adres danych względem początku segmentu

określonego zawartością rejestru DS; rejestr SI wykorzystywany jest do tzw.

adresowania indeksowego oraz w rozkazach łańcuchowych (operacjach na ciągach

znaków).

D

D

I

I

-

-

r

r

e

e

j

j

e

e

s

s

t

t

r

r

i

i

n

n

d

d

e

e

k

k

s

s

u

u

c

c

e

e

l

l

u

u

- zwykle zawiera adres danych względem początku

segmentu określonego zawartością rejestru DS; rejestr DI wykorzystywany jest do

tzw. adresowania indeksowego oraz w rozkazach łańcuchowych - w tym przypadku

jednak zawiera adres względem początku segmentu określonego zawartością

rejestru ES.

R

R

e

e

j

j

e

e

s

s

t

t

r

r

y

y

s

s

e

e

g

g

m

m

e

e

n

n

t

t

o

o

w

w

e

e

służą do przechowywania wartości (SEGMENT)

określających adresy początkowe segmentów:

C

C

S

S

-

-

r

r

e

e

j

j

e

e

s

s

t

t

r

r

s

s

e

e

g

g

m

m

e

e

n

n

t

t

u

u

k

k

o

o

d

d

u

u

programu określa adres początku segmentu używany w

przypadku wszystkich dostępów do pamięci z adresowaniem względnym za

pomocą rejestru IP, tzn. pobierania rozkazów. Z punktu widzenia programisty

rejestr CS razem z rejestrem IP tworzy licznik rozkazów mikroprocesora

(CS:IP).

S

S

S

S

-

-

r

r

e

e

j

j

e

e

s

s

t

t

r

r

s

s

e

e

g

g

m

m

e

e

n

n

t

t

u

u

s

s

t

t

o

o

s

s

u

u

p

p

r

r

o

o

g

g

r

r

a

a

m

m

u

u

określa adres początku segmentu używany

w przypadku wszystkich dostępów do pamięci z adresowaniem względnym za

pomocą rejestru SP lub BP

.

D

D

S

S

-

-

r

r

e

e

j

j

e

e

s

s

t

t

r

r

s

s

e

e

g

g

m

m

e

e

n

n

t

t

u

u

d

d

a

a

n

n

y

y

c

c

h

h

określa adres początku segmentu używany

w przypadku wszystkich dostępów do pamięci danych (np. za pomocą rejestrów

BX, SI, DI lub za pomocą adresu podanego bezpośrednio w rozkazie).

E

E

S

S

-

-

r

r

e

e

j

j

e

e

s

s

t

t

r

r

s

s

e

e

g

g

m

m

e

e

n

n

t

t

u

u

d

d

a

a

n

n

y

y

c

c

h

h

określa adres początku segmentu używany

w przypadku wszystkich dostępów do pamięci danych w rozkazach łańcuchowych.

X X X X OF DF IF TF SF ZF X AF X PF X CF

Nadmiar

(ang. Overflow)

Kierunek

(ang. Direction)

Maska przerwań

(and. Interrupt enable)

Maska przerwań po

każdym rozkazie (ang. Trap enable)

Wskaźnik ujemnego wyniku

(ang. Sign)

Wskaźnik zerowego wyniku

(ang. Zero)

Przeniesienie pomocnicze

(ang. Auxillary curry)

Wskaźnik parzystości (ang. Parity)

Przeniesienie (ang. Curry)

W

W

s

s

k

k

a

a

ź

ź

n

n

i

i

k

k

i

i

o

o

k

k

r

r

e

e

ś

ś

l

l

a

a

j

j

ą

ą

c

c

e

e

s

s

p

p

o

o

s

s

ó

ó

b

b

d

d

z

z

i

i

a

a

ł

ł

a

a

n

n

i

i

a

a

k

k

o

o

m

m

p

p

u

u

t

t

e

e

r

r

a

a

TF – ustawienie na 1 powoduje przerwania nr 3, z jednoczesnym zgaszeniem TF,

po wykonaniu jednego rozkazu (wykorzystywany głównie przez debugery);

IF – ustawienie na wartość 1 zezwala na przyjmowanie przerwań zewnętrznych,

ustawienie na 0 powoduje zablokowanie przyjmowania przerwań

zewnętrznych za wyjątkiem przerwania NMI;

DF – ustawienie na 1 powoduje, że zawartość rejestrów DI oraz SI przy

wykonywaniu rozkazów łańcuchowych będzie zmniejszana, natomiast dla

DF=0 będzie zwiększana.

W

W

s

s

k

k

a

a

ź

ź

n

n

i

i

k

k

i

i

u

u

s

s

t

t

a

a

w

w

i

i

a

a

n

n

e

e

w

w

w

w

y

y

n

n

i

i

k

k

u

u

w

w

y

y

k

k

o

o

n

n

a

a

n

n

i

i

a

a

r

r

ó

ó

ż

ż

n

n

y

y

c

c

h

h

r

r

o

o

z

z

k

k

a

a

z

z

ó

ó

w

w

CF – wskaźnik przeniesienia globalnego, zmieniany rozkazami arytmetycznymi

i przesunięć, zerowany rozkazami logicznymi;

OF – wskaźnik nadmiaru, zmieniany rozkazami arytmetycznymi i zerowany

rozkazami logicznymi; flaga ta jest zmieniana również rozkazami

przesunięć, których drugi argument jest równy 1;

SF – wskaźnik znaku (ujemnego wyniku), zmieniany rozkazami arytmetycznymi

i logicznymi;

ZF – wskaźnik zerowego wyniku, zmieniany rozkazami arytmetycznymi

i logicznymi;

PF – wskaźnik parzystej liczby jedynek w zapisie binarnym wyniku, zmieniany

rozkazami arytmetycznymi i logicznymi;

AF – wskaźnik przeniesienia pomocniczego (z bitu 3 na 4) ustawiany przy

wykonywaniu rozkazów arytmetyki dziesiętnej.

O

O

r

r

g

g

a

a

n

n

i

i

z

z

a

a

c

c

j

j

a

a

p

p

a

a

m

m

i

i

ę

ę

c

c

i

i

64 KB

Segment

kodu

XXXX0h

Największy adres

fizyczny

FFFFFh

64 KB

Segment

stosu

64 KB

Segment

danych

64 KB

Segment

dodatkowy

MSB

LSB

1234h

1235h

Segment kodu (CS)

Segment stosu (SS)

Segment danych (DS)

Segment dodatkowy (ES)

+ SP lub BP

+ IP

00000h

8 bitów

CS

0

IP

0

Wektor 0

IP

3FE

IP

3FC

Wektor 255

U

U

k

k

ł

ł

a

a

d

d

y

y

w

w

e

e

j

j

/

/

w

w

y

y

j

j

w

w

s

s

p

p

ó

ó

ł

ł

p

p

r

r

a

a

c

c

u

u

j

j

ą

ą

c

c

e

e

z

z

m

m

i

i

k

k

r

r

o

o

p

p

r

r

o

o

c

c

e

e

s

s

o

o

r

r

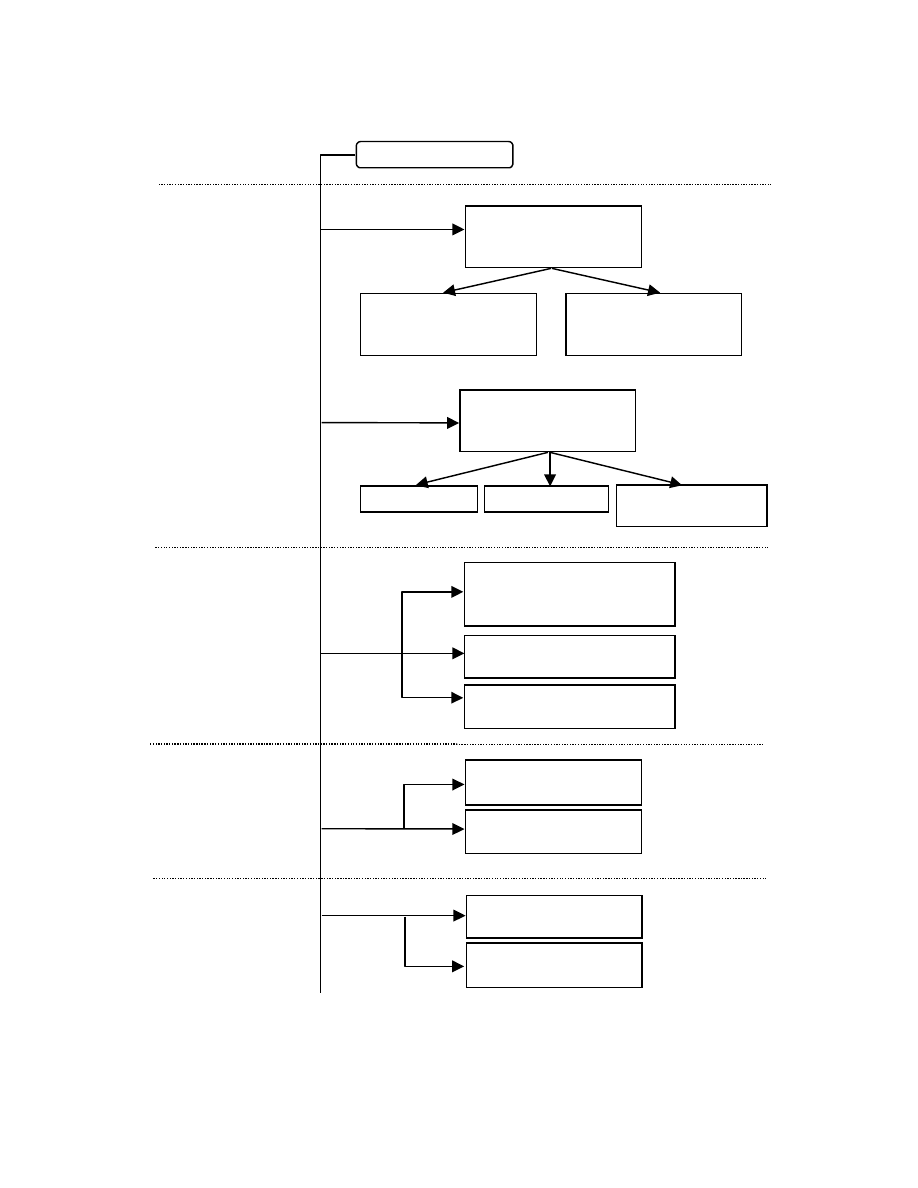

e

e

m

m

Układy wej / wyj

Układy współpracujące

z klawiaturami

i wskaźnikami

Układy sterujące

monitory ekranowe

Układy sterujące

dyski elastyczne

Programowane układy

sterowania przerwań

Układy sterowania

kanału DMA

Programowane

liczniki

Układy

wielofunkcyjne

Układy służące do

równoległego

przesyłania informacji

Programowane

układy wej / wyj

Proste układy typu:

- rejestr zatrzaskowy;

- bufor.

Układy służące do

szeregowego

przesyłania informacji

Synchroniczne Asynchroniczne Synchroniczne

i asynchroniczne

Podstawowe

uniwersalne

układy wej / wyj

Specjalizowane

układy wej / wyj

Układy

sterujące

Inne

układy

A

A

d

d

r

r

e

e

s

s

o

o

w

w

a

a

n

n

i

i

e

e

p

p

a

a

m

m

i

i

ę

ę

c

c

i

i

i

i

u

u

k

k

ł

ł

a

a

d

d

ó

ó

w

w

w

w

e

e

j

j

/

/

w

w

y

y

j

j

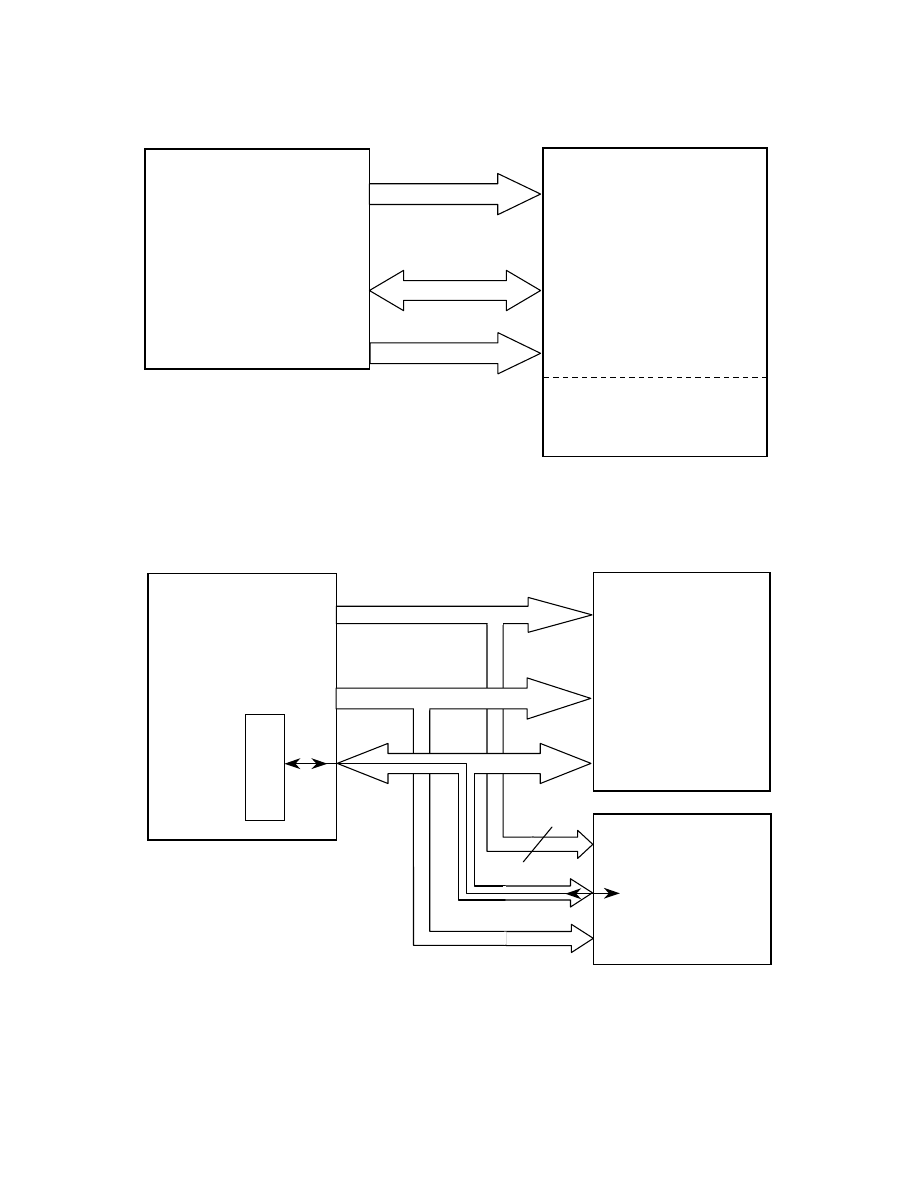

J

J

e

e

d

d

n

n

o

o

l

l

i

i

t

t

e

e

R

R

o

o

z

z

d

d

z

z

i

i

e

e

l

l

o

o

n

n

e

e

MIKROPROCESOR

Pamięć

Układy

wej/wyj

Szyna adresowa

Szyna sterująca

Szyna danych

MIKROPROCESOR

Pamięć

Układy

wej/wyj

Szyna adresowa

Szyna sterująca

Sz

yn

a

dany

ch

16

A

kum

ul

ato

r

P

P

o

o

d

d

s

s

t

t

a

a

w

w

o

o

w

w

e

e

s

s

p

p

o

o

s

s

o

o

b

b

y

y

o

o

b

b

s

s

ł

ł

u

u

g

g

i

i

u

u

k

k

ł

ł

a

a

d

d

ó

ó

w

w

w

w

e

e

j

j

ś

ś

c

c

i

i

a

a

-

-

w

w

y

y

j

j

ś

ś

c

c

i

i

a

a

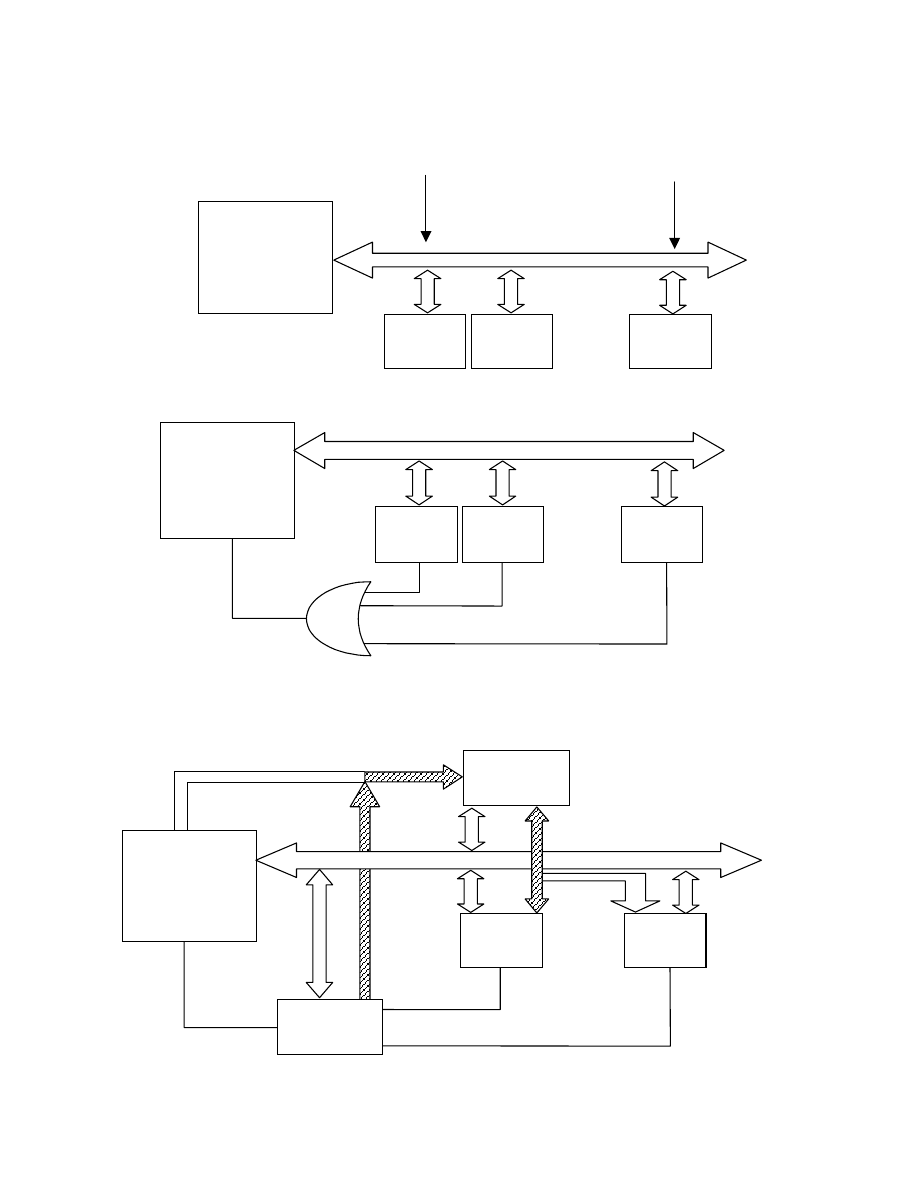

O

O

b

b

s

s

ł

ł

u

u

g

g

a

a

p

p

r

r

o

o

g

g

r

r

a

a

m

m

o

o

w

w

a

a

Z

Z

g

g

ł

ł

o

o

s

s

z

z

e

e

n

n

i

i

e

e

p

p

r

r

z

z

e

e

r

r

w

w

a

a

n

n

i

i

a

a

Bezpośredni dostęp do pamięci

Mikroprocesor

Układ

wej/wyj 2

Układ

wej/wyj n

. . .

Przerwanie

Układ

wej/wyj 1

...

Żądanie

przerwania

INTR

Mikroprocesor

Układ

wej/wyj 1

Układ

wej/wyj 2

Układ

wej/wyj n

. . .

Czy układ

wej/wyj 1

żąda obsługi?

Czy układ

wej/wyj n

żąda obsługi?

. . .

Mikroprocesor

Układ

wej/wyj

Układ

wej/wyj

. . .

Przerwanie

...

HOLD

Pamięć

DMAC

DRQ

Szyna adresowa

Szyna danych

P

P

r

r

z

z

e

e

r

r

w

w

a

a

n

n

i

i

a

a

J

J

e

e

d

d

n

n

o

o

p

p

o

o

z

z

i

i

o

o

m

m

o

o

w

w

a

a

s

s

t

t

r

r

u

u

k

k

t

t

u

u

r

r

a

a

p

p

r

r

z

z

e

e

r

r

w

w

a

a

ń

ń

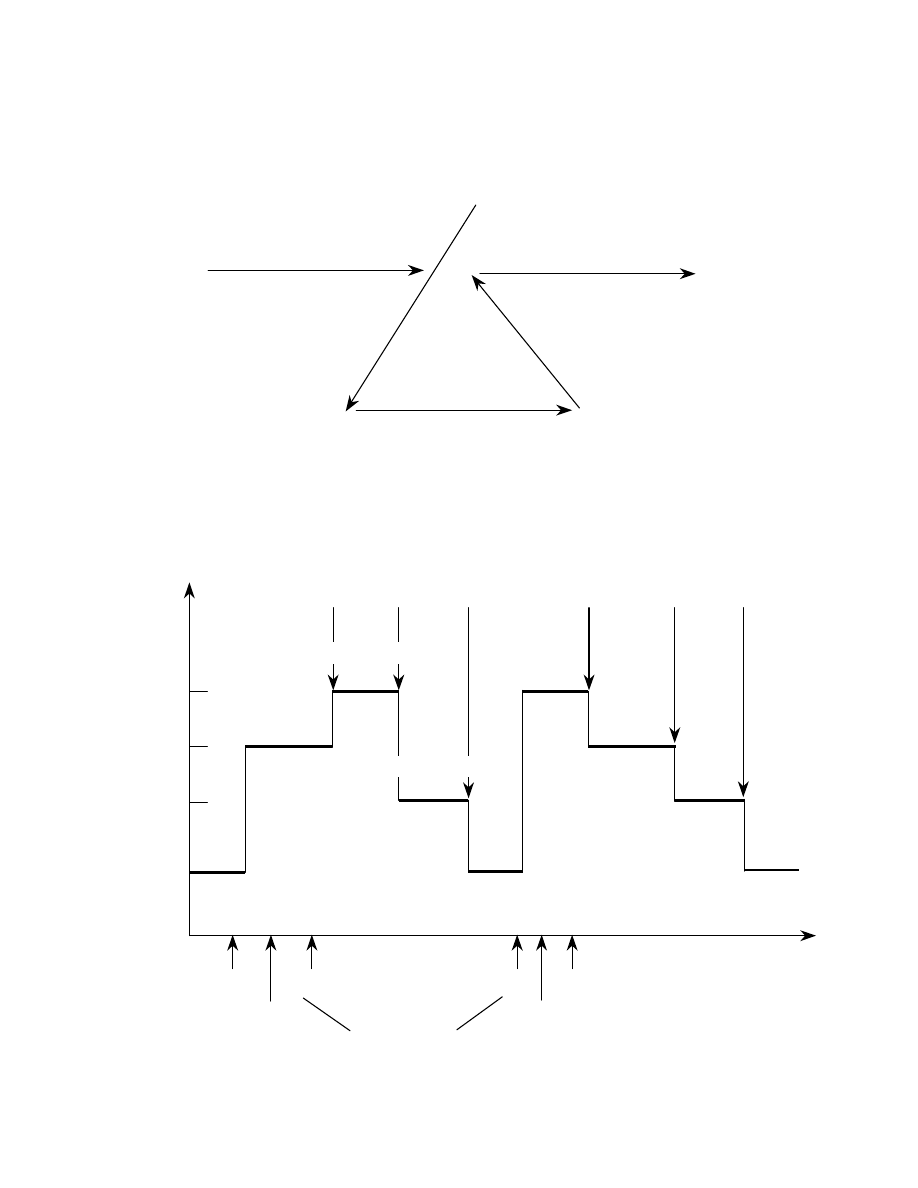

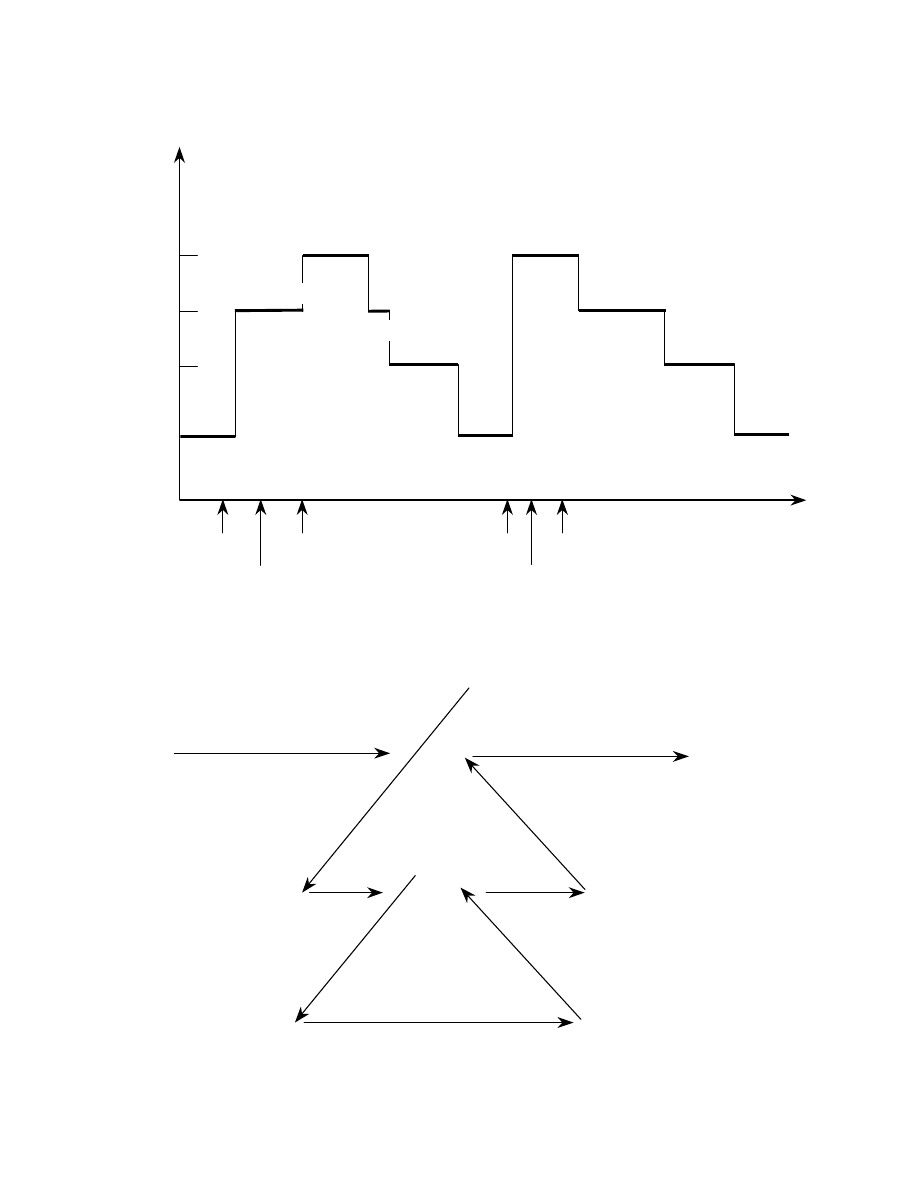

Realizacja

programu głównego

Kontynuacja

programu głównego

Sygnał żądania

przerwania

Skok do podprogramu

obsługi przerwania

Realizacja podprogramu

obsługi przerwania

Powrót do programu

głównego

Priorytet

Program

główny

IREQ1

IREQ2

IREQ3

IREQ2

IREQ1

IREQ3

IREQ3

IREQ1

IREQ2

Czas

Chwile odblokowania wejść sygnału żądania przerwania

Chwile pojawienia się sygnałów żądania przerwania

Podprogram 2

Podprogram 3

Podprogram 1

Podprogram główny

W

W

i

i

e

e

l

l

o

o

p

p

o

o

z

z

i

i

o

o

m

m

o

o

w

w

a

a

s

s

t

t

r

r

u

u

k

k

t

t

u

u

r

r

a

a

p

p

r

r

z

z

e

e

r

r

w

w

a

a

ń

ń

Program główny

Kontynuacja

programu głównego

Przerwanie z drugiego

urządzenia zewnętrznego

Podprogramu obsługi drugiego

urządzenia zewnętrznego

Przerwanie z trzeciego

urządzenia zewnętrznego

Podprogramu obsługi trzeciego

urządzenia zewnętrznego

Kontynuacja podprogramu

obsługi drugiego urządzenia

zewnętrznego

Priorytet

Program

główny

IREQ1

IREQ2

IREQ3

IREQ2

IREQ1

IREQ3

IREQ3

IREQ1

IREQ2

Czas

Podprogram 2

Podprogram 3

Podprogram 1

Podprogram główny

F

F

a

a

z

z

y

y

o

o

b

b

s

s

ł

ł

u

u

g

g

i

i

p

p

r

r

z

z

e

e

r

r

w

w

a

a

n

n

i

i

a

a

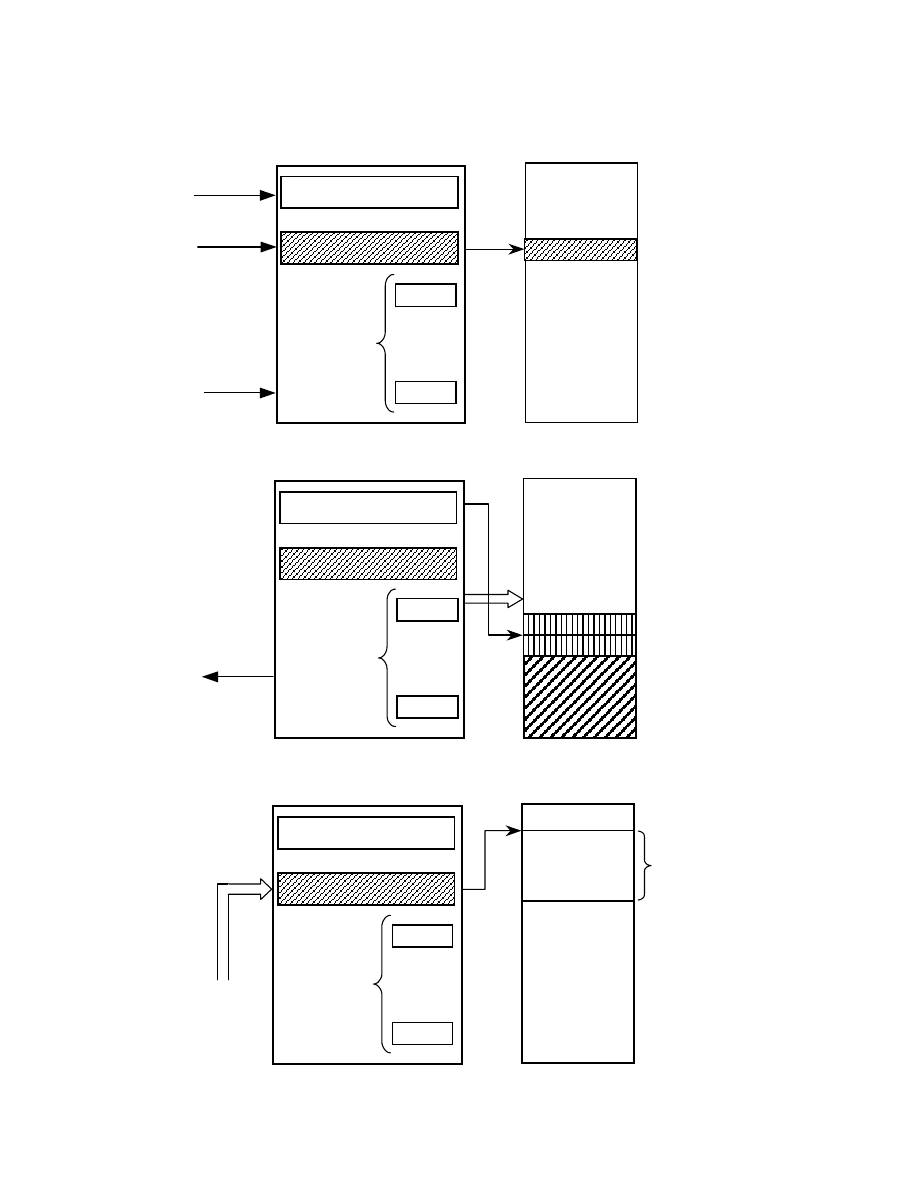

Rejestry

ogólnego

przeznaczenia

.

.

.

Wskaźnik

stosu

Licznik

rozkazów

Żądanie

przerwania

Pamięć

Mikroprocesor

Potwierdzenie

przyjęcia

przerwania

Pamięć

Mikroprocesor

Zawartości licznika

rozkazów, rejestrów

ogólnego przeznaczenia

oraz słowa stanu

procesora zostają

przeniesiona na stos.

Rejestry

ogólnego

przeznaczenia

.

.

.

Rejestry

ogólnego

przeznaczenia

.

.

.

Podprogram

obsługi

przerwania

(Adres podprogramu

obsługi przerwania

zostaje wprowadzony do

licznika rozkazów)

Wektor

Pamięć

Mikroprocesor

Ź

Ź

r

r

ó

ó

d

d

ł

ł

a

a

p

p

r

r

z

z

e

e

r

r

w

w

a

a

ń

ń

w

w

m

m

i

i

k

k

r

r

o

o

p

p

r

r

o

o

c

c

e

e

s

s

o

o

r

r

z

z

e

e

P

P

r

r

i

i

o

o

r

r

y

y

t

t

e

e

t

t

y

y

p

p

r

r

z

z

e

e

r

r

w

w

a

a

ń

ń

Priorytet Rodzaj

przerwania

Najwyższy

Najniższy

Wewnętrzne

NMI

INTR

Dla pracy krokowej

INT n - przerwanie programowe występujące bezpośrednio po zakończeniu wykonywania

2-bajtowego rozkazu INT n umieszczonego w programie. Parametr n wskazuje numer

wektora adresu przerwania w tablicy przerwań.

INT0 - przerwanie programowe występujące gdy znacznik OF=1 (wystąpiło przepełnienie

w operacjach poprzedzających wykonanie rozkazu INT0). Przerwanie to ma stały wektor n

= 4.

Przerwanie przy błędzie dzielenia przez - jest generowane jeżeli wartość wyliczonego ilorazu

przekracza dopuszczalny zakres (np. przy próbie dzielenia przez zero). Przerwanie to ma

stały wektor n = 0.

Przerwanie dla pracy krokowej - jest generowane po zakończeniu każdego rozkazu o ile

znacznik TF=1. Przerwanie to ma stały wektor n = 1. Dla TF=0 przerwanie jest

zablokowane.

NMI - przerwanie to nie może być programowo zablokowane. Jego wystąpienie jest

zapamiętywane w wewnętrznych układzie przerwań i zawsze akceptowane przez

mikroprocesor po zakończeniu wykonywania bieżącego rozkazu (o ile nie wystąpiło

przerwanie wewnętrzne o wyższym priorytecie. Przerwanie to ma stały wektor n = 2.

INTR - przerwanie zewnętrzne, maskowalne wprowadzane do mikroprocesora przez wejście

INTR . Może być ono zablokowane programowo rozkazem CLI, który zeruje znacznik

przerwania IF.

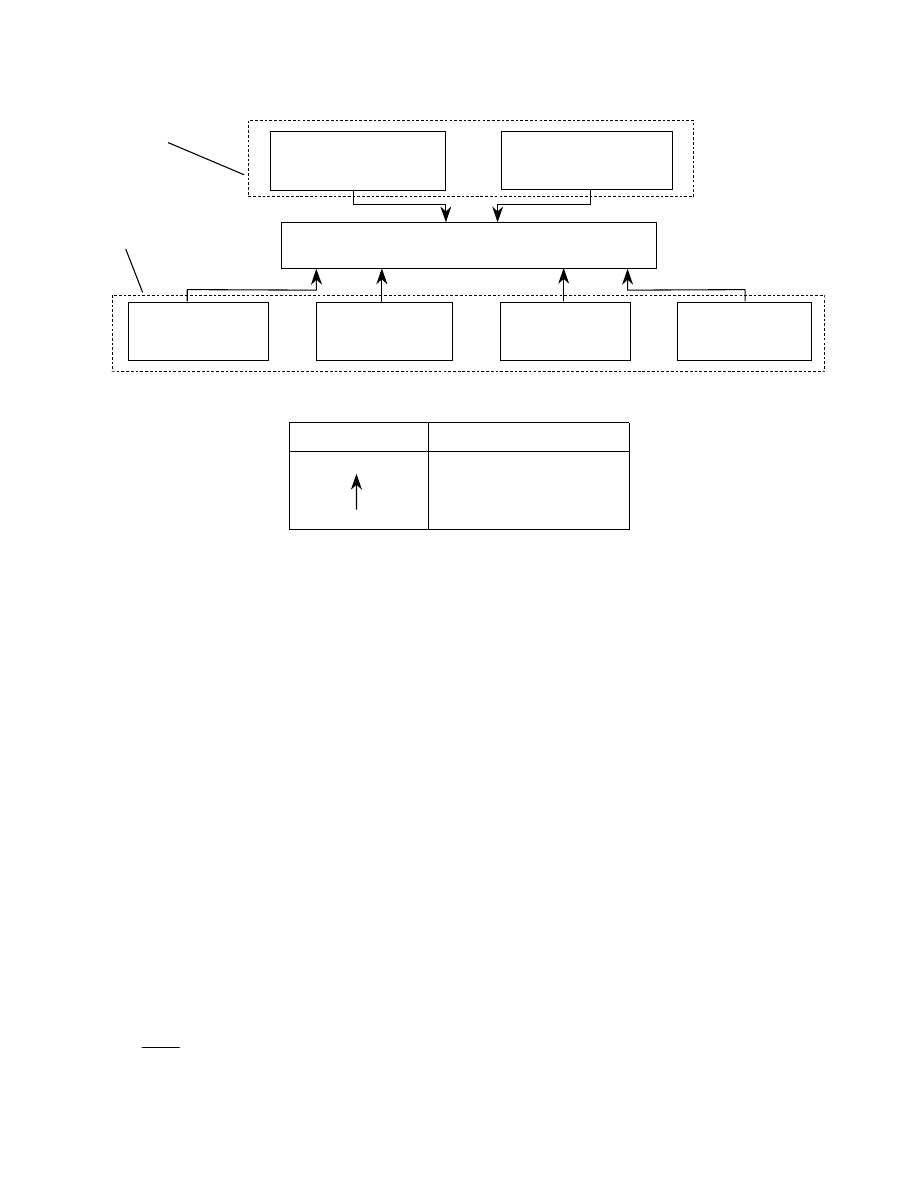

Wewnętrzny układ sterownia przerwań

Żądanie przerwania

maskowalnego

INTR

Żądanie przerwania

niemaskowalnego

NMI

Przerwanie przy

błędzie dzielenia

Przerwanie przy

nadmiarze INTO

(OF=1)

Przerwanie

programowe

INT n

Przerwanie dla

pracy krokowej

(TF=1)

Przerwanie

wewnętrzne

Przerwanie

zewnętrzne

Wyszukiwarka

Podobne podstrony:

architektura komputera klasy ibm pc, Pomoce Naukowe, Informatyka

Cały twój PC na pendrivie

D Hanulanka, Sklepienia gwiaździste w architekturze późnego gotyku na Śląsku

Transport pojecia wstępne podział i klasyfikacje na slajdy prgot, Transport pollub, Systemy transpor

Przeglad chipsetow w plytach glownych komputerow IBM PC

odp z pc na zal cw

Cały twój PC na pendrivie

Przenoszenie ulubionych zakładek z PC na Maka

Instalacja programów z PC na telefon poprzez kabel USB

Przeglad magistral w komputerach IBM PC(1)

PN B 01029 Zasady wymiarowania na rysunkach architektoniczno budowlanych

PN 70 B 01025 Oznaczenia graficzne na rysunkach architektoni

Sposoby na wilgotność powietrza wokół roślin, Architektura krajobrazu(28)

PDF Jak przenieść dane z pliku ISO na płytę CD, pc 10s075ok

więcej podobnych podstron