Magistrale systemowe

Dariusz Chaberski

Magistrale systemowe

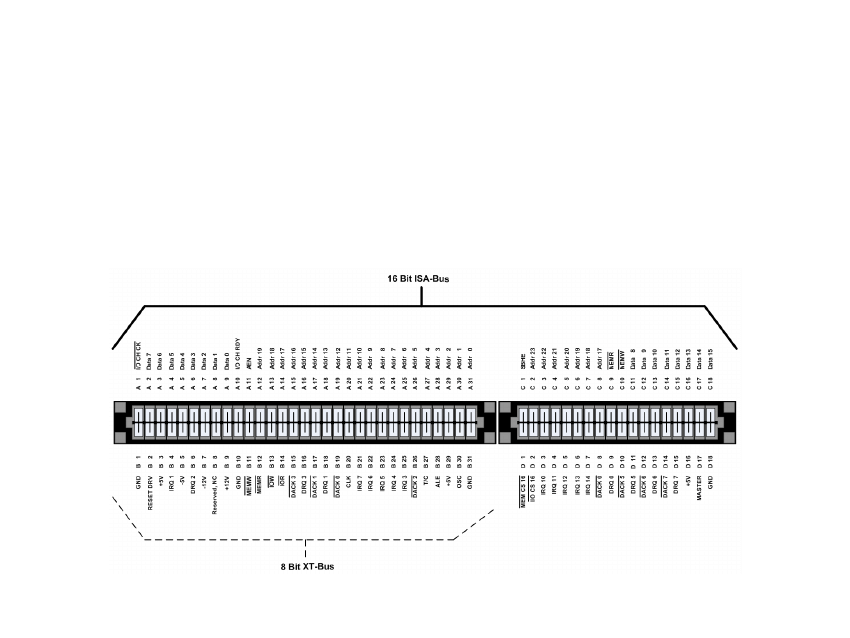

§ ISA (ang. Industry Standard Architecture)

+ rodzaje

3 8 bitów - komputery klasy IBM XT

3 16 bitów - komputery klasy IBM AT

2

Magistrale systemowe

§ ISA - patametry

+ 8 bitowa

3 szerokość szyny - 8 bitów

· ilość kontaktów 62

· napięcia zasilające - +5 V, -5 V, +12 V, -12 V

· częstotliwość pracy 4.77 MHz (1 MB/s)

3 16 bitowa

· kompatybilna z magistralną ISA 8 bitową

· szerokość szyny 16 bitów

· ilość kontaktów 98

· napięcia zasilające - +5 V, -5 V, +12 V, -12 V

· częstotliwość pracy 8.33 MHz (2 MB/s)

3

Magistrale systemowe

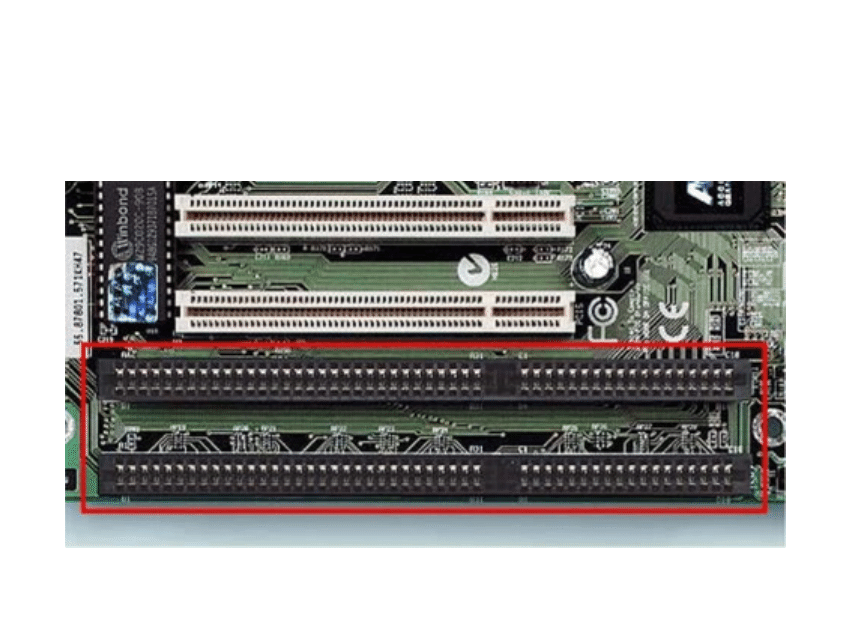

§ magistrala ISA na tle magistrali PCI

4

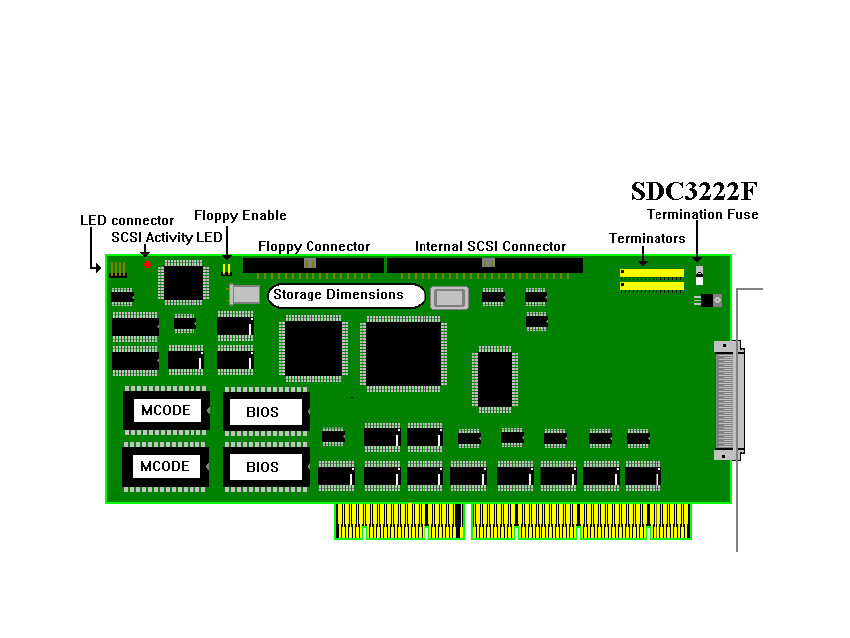

Magistrale systemowe

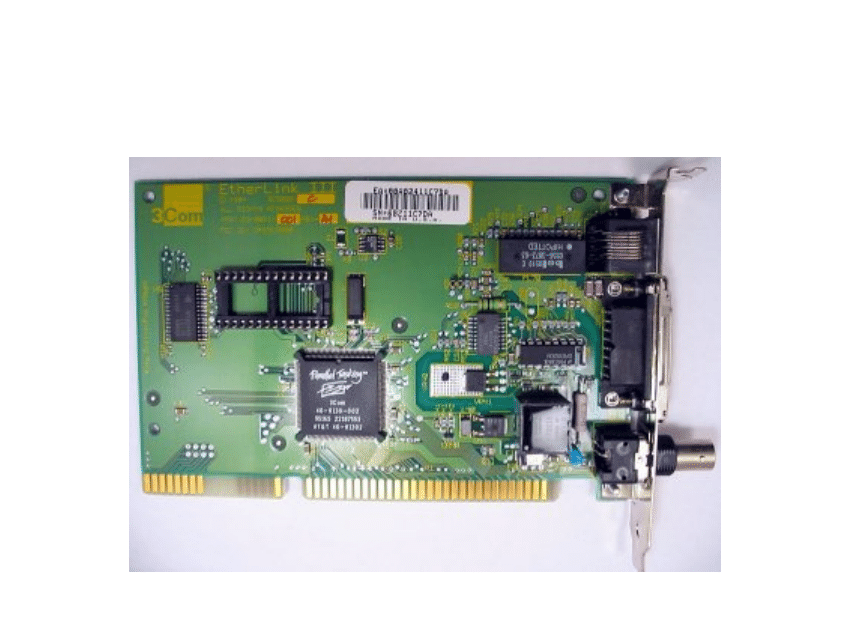

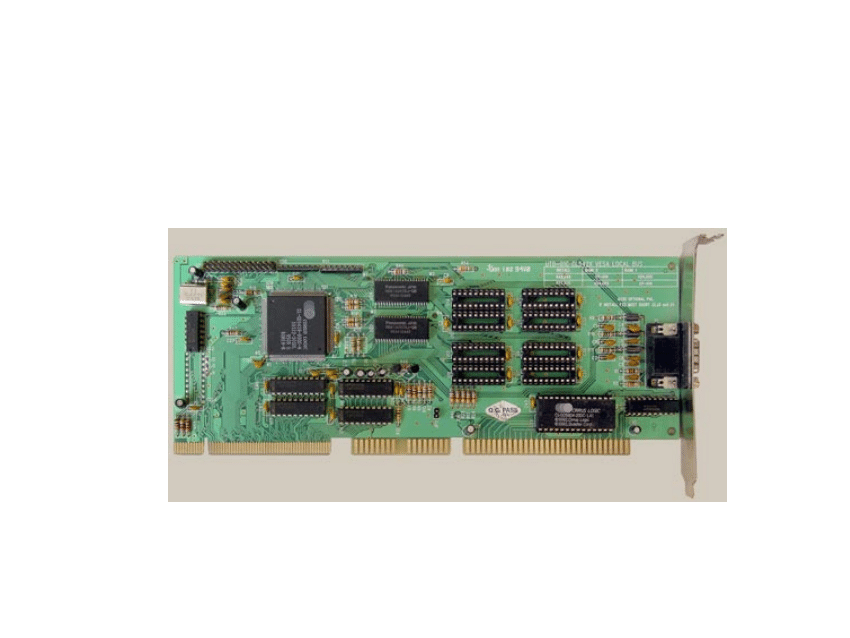

§ przykład karty rozszerzeń wykorzystującej magistarlę ISA 16-to bitową

5

Magistrale systemowe

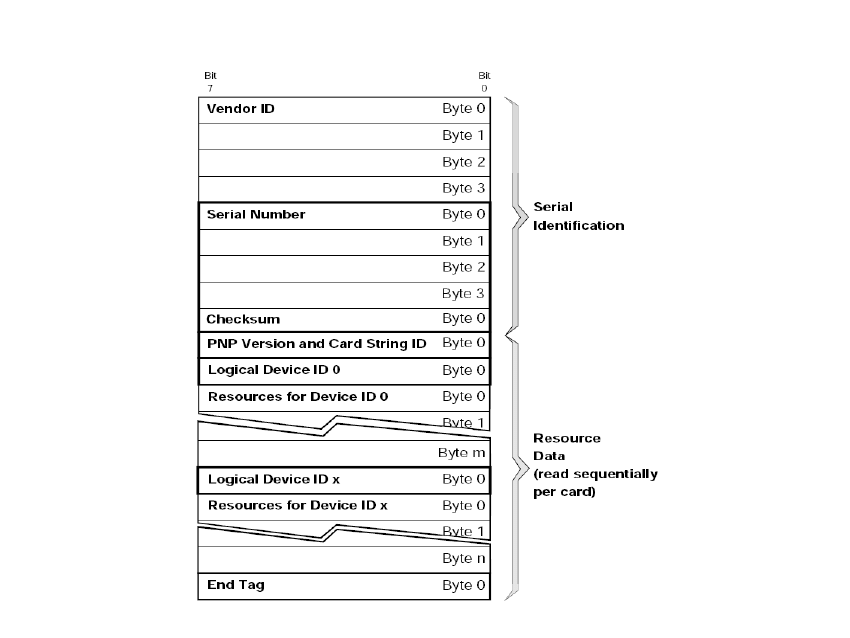

§ EISA (Extended ISA) - charakterystyka

+ zaprojektowana dla 32 bitowych komputerów 386 (DX)

+ prędkość tarnsmisji do 33 MB/s

+ częstotliwość pracy taka jak ISA (8.33 MHz, kompatybilność)

+ szerokość magistrali danych 32 bity

+ obsługa standardu Plug & Play

6

ISA - PNP

7

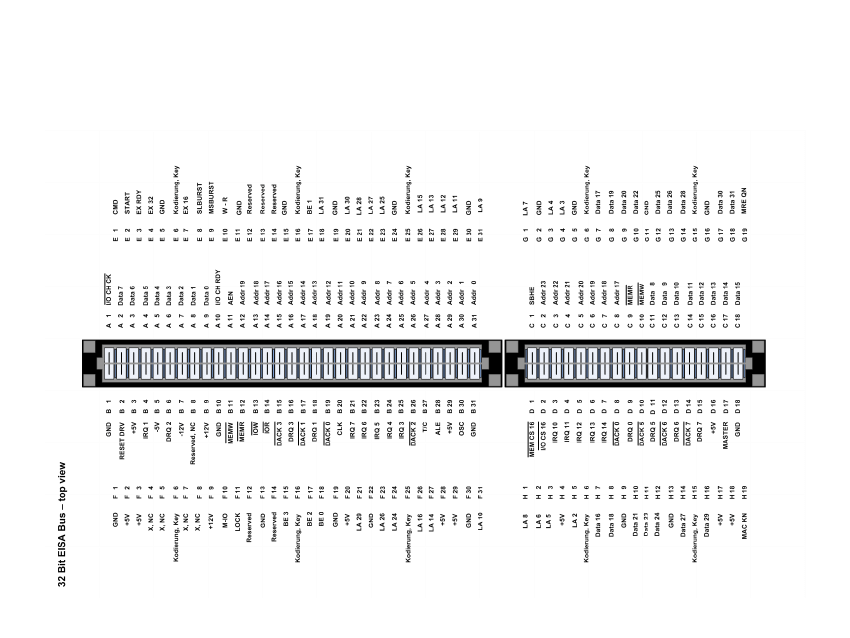

Magistrale systemowe

§ EISA - złącze

8

Magistrale systemowe

§ EISA - złącze

9

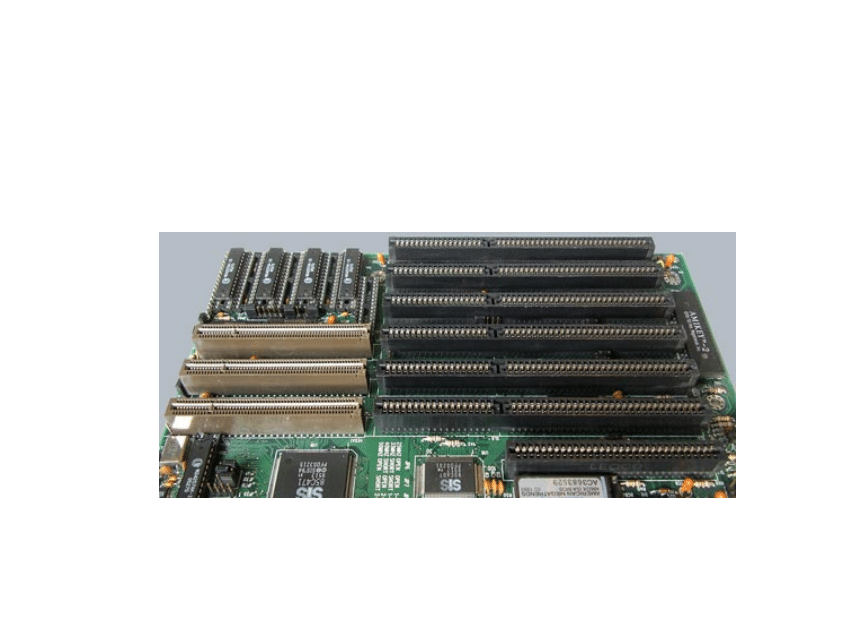

Magistrale systemowe

§ VESA (ang. Video Electronics Standards Association) Local Bus, rok 1992

+ 32 bitowa szyna danych

+ rozszerzenie magistrali ISA w postaci dodatkowego złącza

+ główne zastosowanie karty graficzne i kontrolery wejścia/wyjścia

+ częstotliwość pracy równa jest częstotliwości pracy procesora (wada)

10

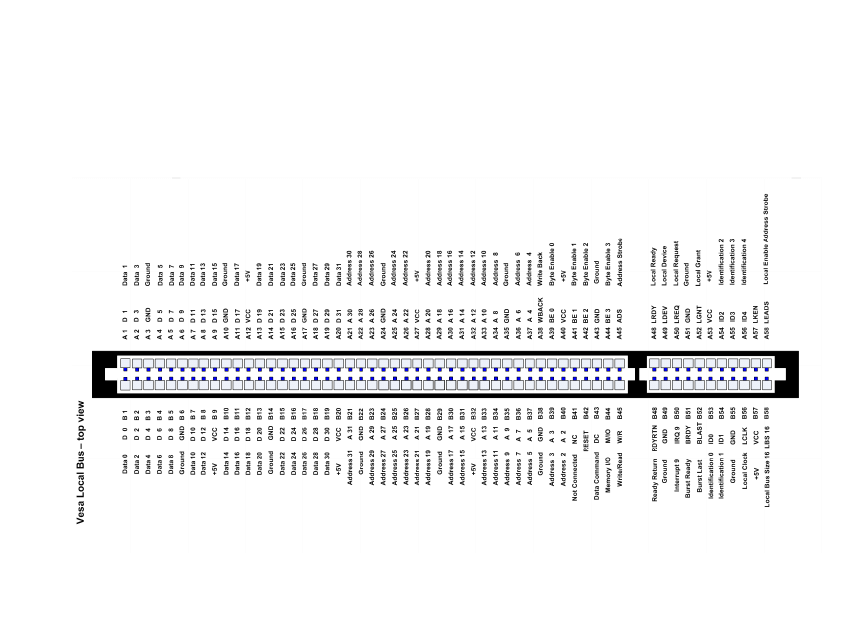

Magistrale systemowe

§ VESA - dodatkowe złącze

11

Magistrale systemowe

§ VESA - widok złącza

12

Magistrale systemowe

§ VESA - karta graficzna wykorzystująca złącze VESA

13

Magistrale systemowe

§ PCI (ang. Peripheral Component Interconnect)

+ PCI 2.0 - rok 1993, 32 bity, 33 MHz, 133 MB/s, 5 V (12 V, -12 V, -5 V)

+ PCI 2.1 - rok 1994, 64 bity, 66 MHz, 533 MB/s, 5 V (12 V, -12 V, -5 V)

+ PCI 2.2 - rok 1999, 64 bity, 66 MHz, 533 MB/s, 5/3.3 V (12 V, -12 V, -5/3.3 V)

+ PCI 2.2 - rok 1999, 64 bity, 66 MHz, 533 MB/s, 3.3 V (12 V, -12 V, -3.3 V)

14

Magistrale systemowe

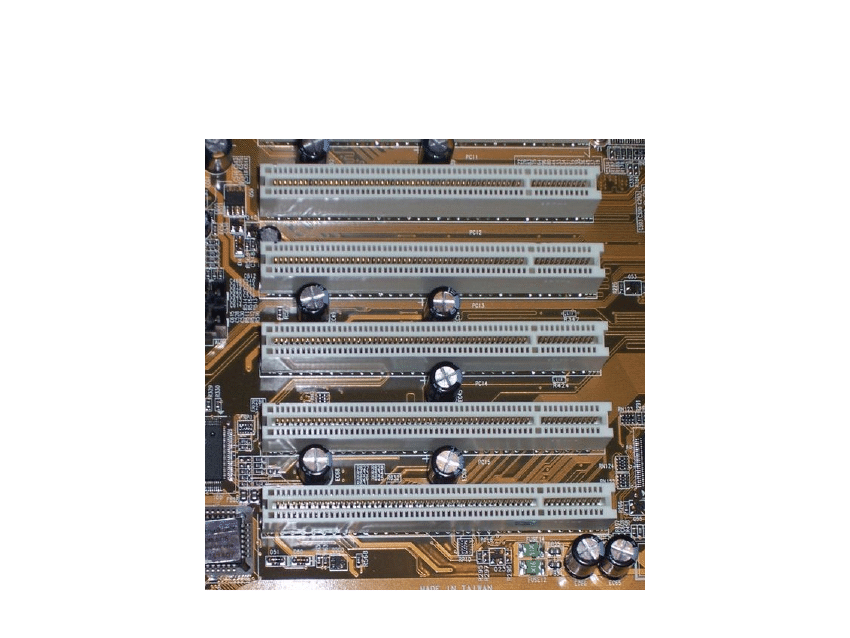

§ złącza magistrali PCI

15

Magistrale systemowe

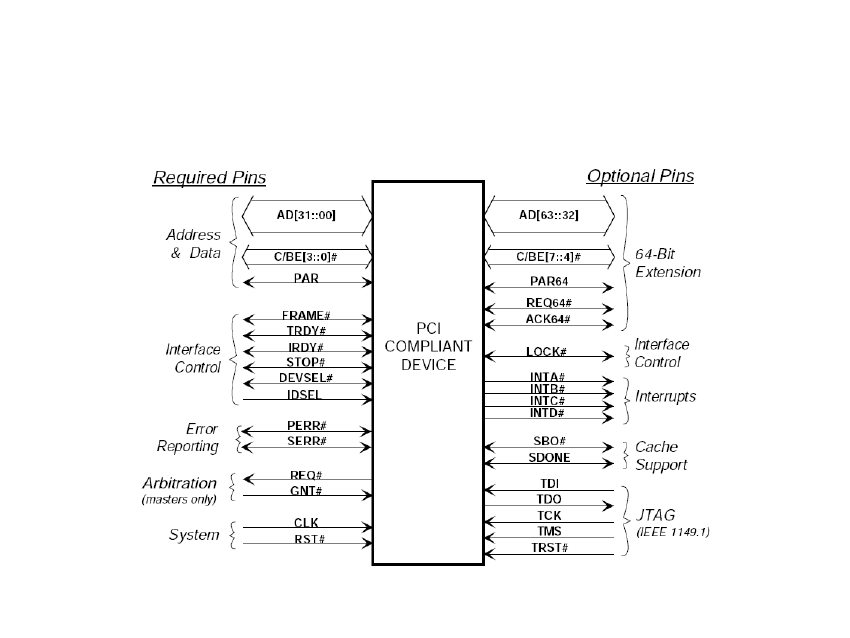

§ sygnały magistrali PCI

16

Magistrale systemowe

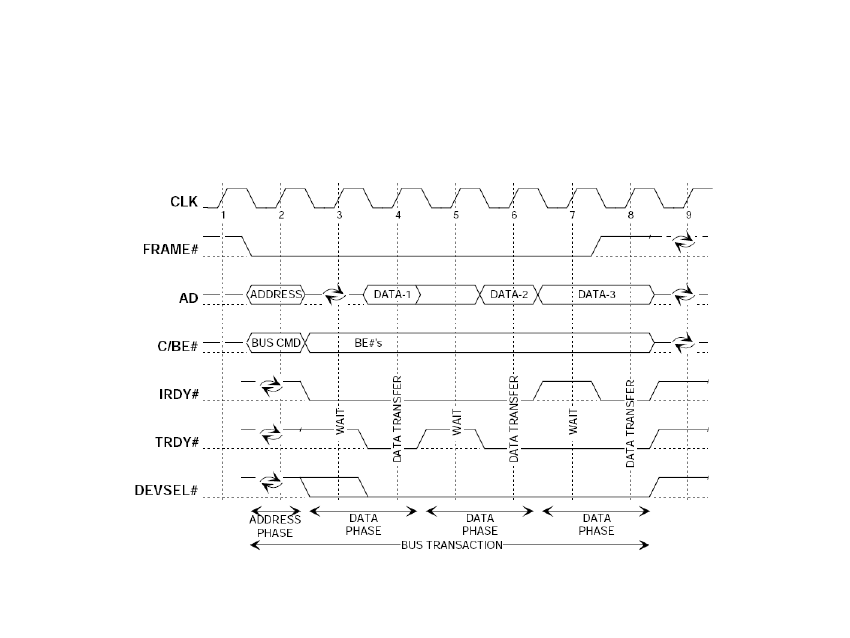

§ przykład operacji odczytu na magistrali PCI

17

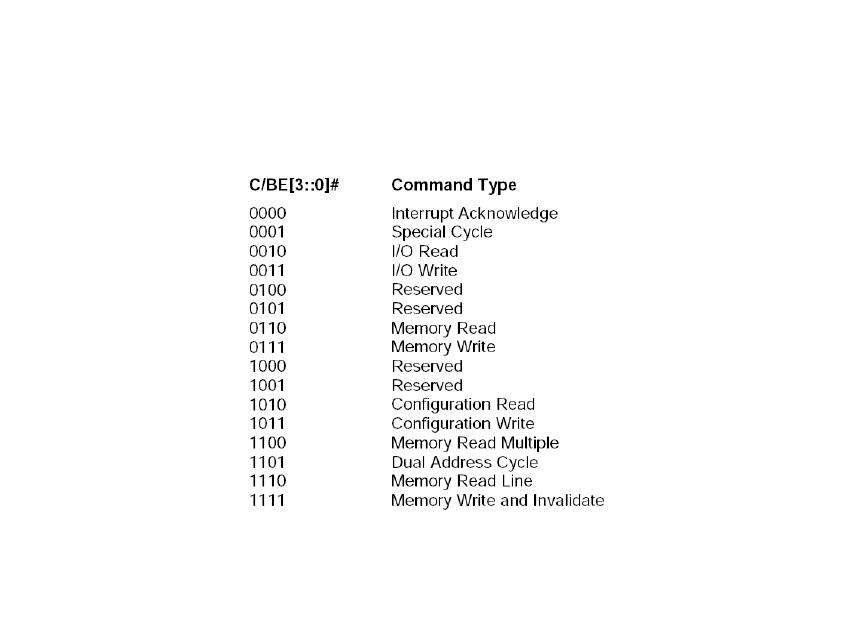

Komendy magistrali

18

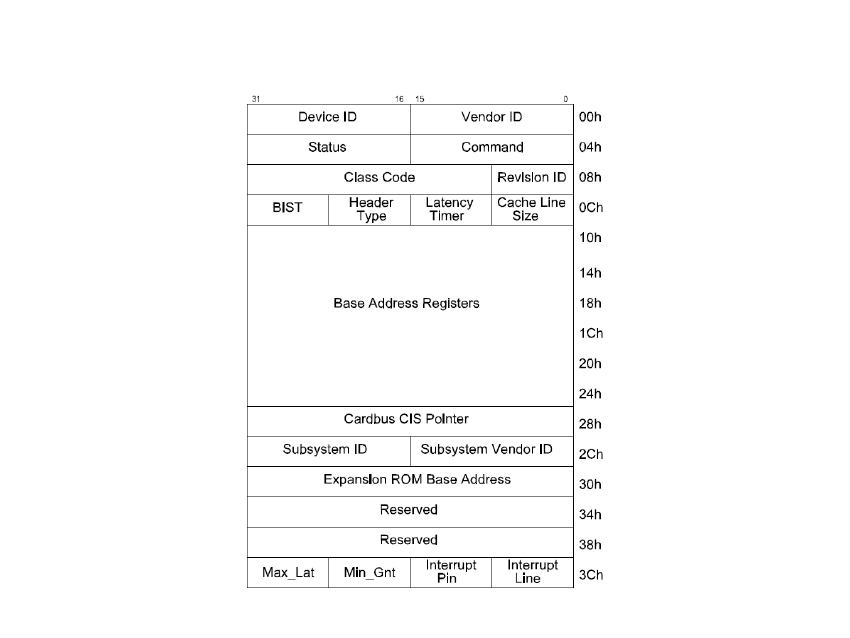

Przestrzeń konfiguracyjna

19

Magistrale systemowe

§ AGP (ang. Accelerated/Advanced Graphics Port)

+ zoptymalizowana magistrala PCI zaprojektowana do przesyłania dużych ilości danych pomiędzy

pamięcią komputera a pamięcią karty graficznej

+ z punktu widzenia programu dodatkowa magistrala PCI

+ rodzaje

3 AGP 1x - 32 bity, 66 MHz, 266 MB/s, 5/3.3 V

3 AGP 2x - 32 bity, 66 MHz, 533 MB/s, 5/3.3 V, (podwójna przepływność - dwa przesłania

na okres zegara taktującego)

3 AGP 4x - 32 bity, 66 MHz, 1066 MB/s, 1.5 V

3 AGP 8x - 32 bity, 66 MHz, 2133 MB/s, 0.8 V

20

Magistrale systemowe

§ PCI-X (ang. PCI eXtended)

+ rozszerzenie magistrali PCI o dodatkowe złącze

+ magistrala 64 bitowa

+ rodzaje

3 PCI-X 1.0 - rok 1999, 64 bity, 133 MHz, 1066 MB/s, 3.3 V

3 PCI-X 2.0 - rok 2002, 64 bity, 533 MHz, 4.26 GB/s, 3.3/1.5 V

3 PCI-X 3.0 - rok 2003, 64 bity, 1066 MHz, 7.95 GB/s, 3.3/1.5 V

21

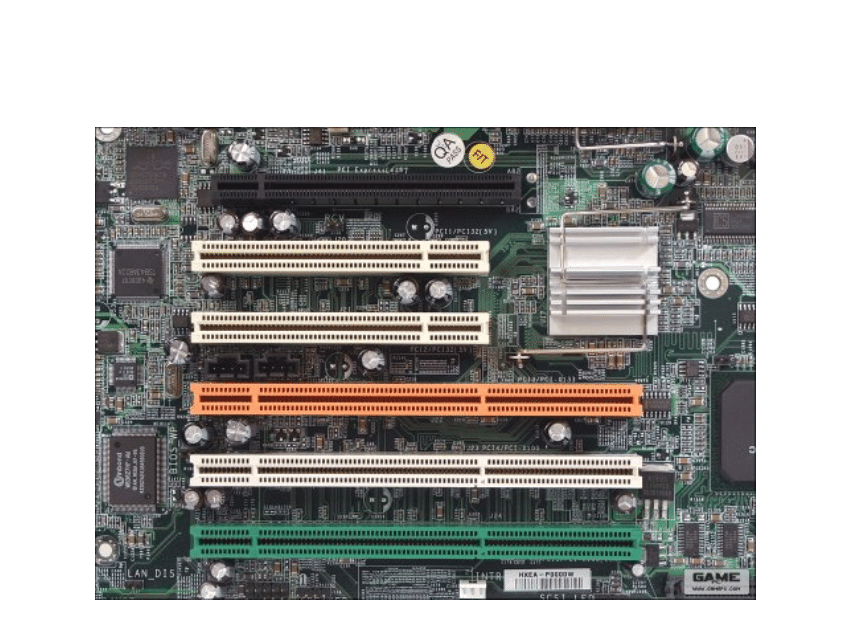

Magistrale systemowe

§ magistrale (od góry) AGP, PCI, PCI-X

22

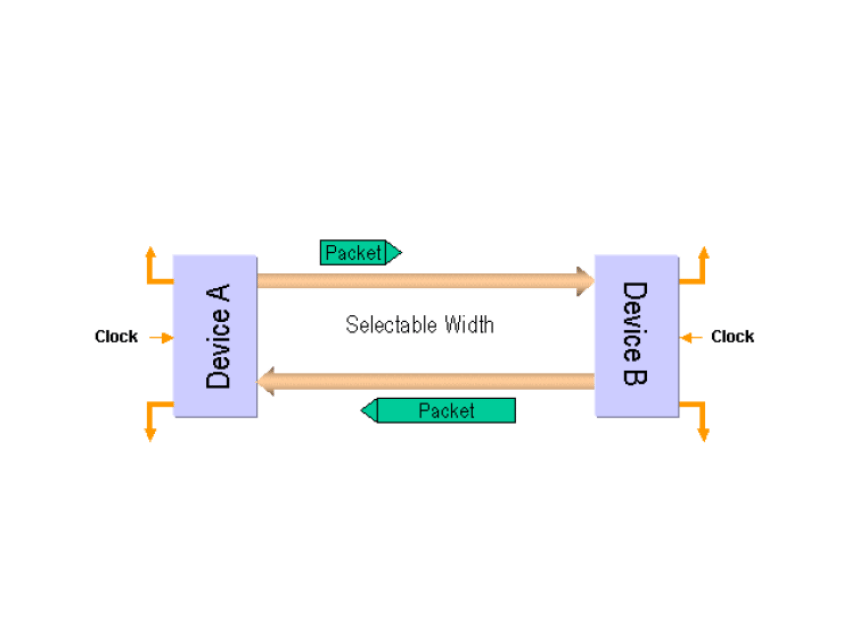

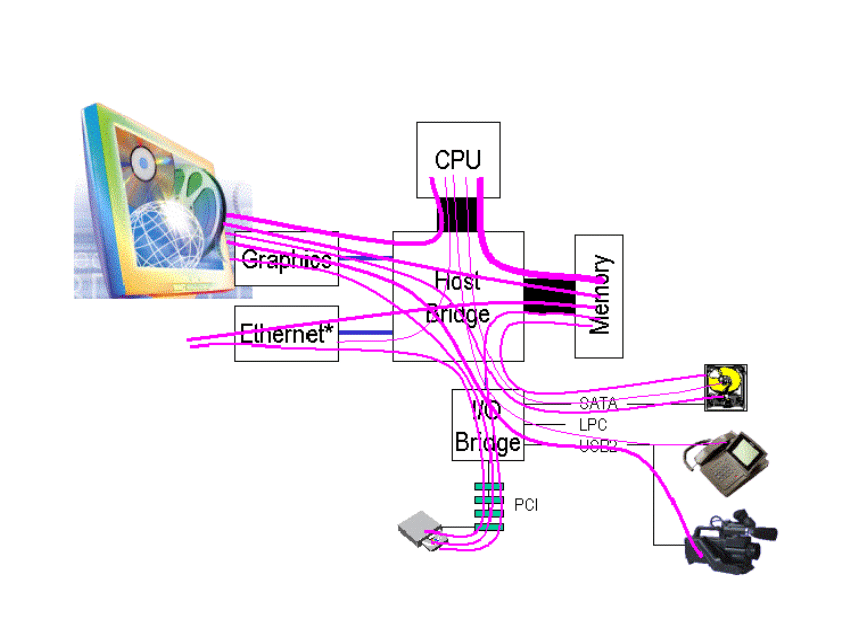

PCI-Express - 3GIO (ang. 3rd Generation I/O)

§ magistrala szeregowa

§ cel: zastąpić PCI oraz AGP

§ każde urządzenie jest podłączone bezpośrednio do kontrolera - urządzenia nie współdzielą zasobów

(pinów)

§ częstotliwośc pracy 2.5 GHz

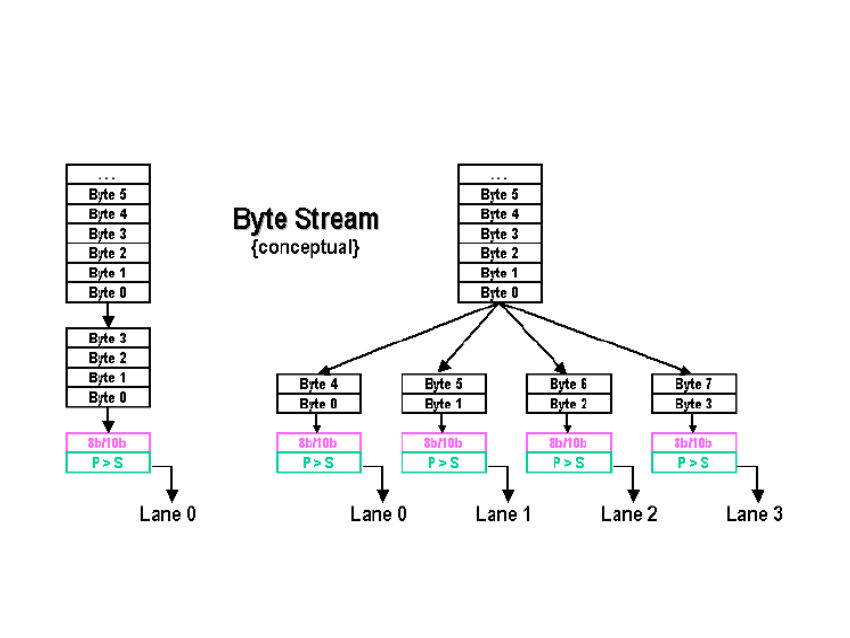

§ możliwość przesyłania równolegle kilkoma kanałami dla zwiększenia przepustowości

§ przepustowość 250 MB/s (1 kanał), ..., (32 kanały - 8 GB/s)

§ transmisja full-duplex

23

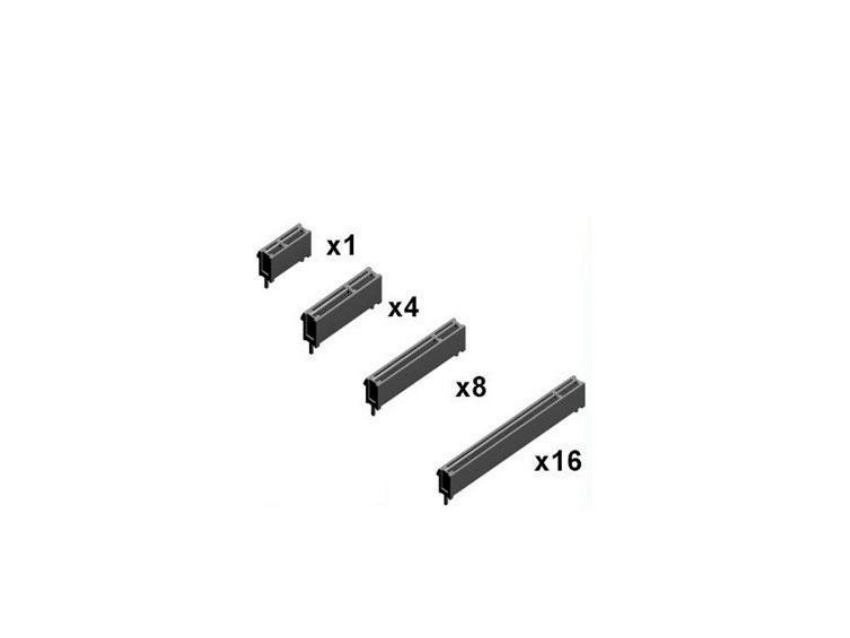

PCI-Express - koncepcja skalowalności

§ PCI-Express x1 - 18 wyprowadzeń, ..., x16 - 82 wyprowadzenia

24

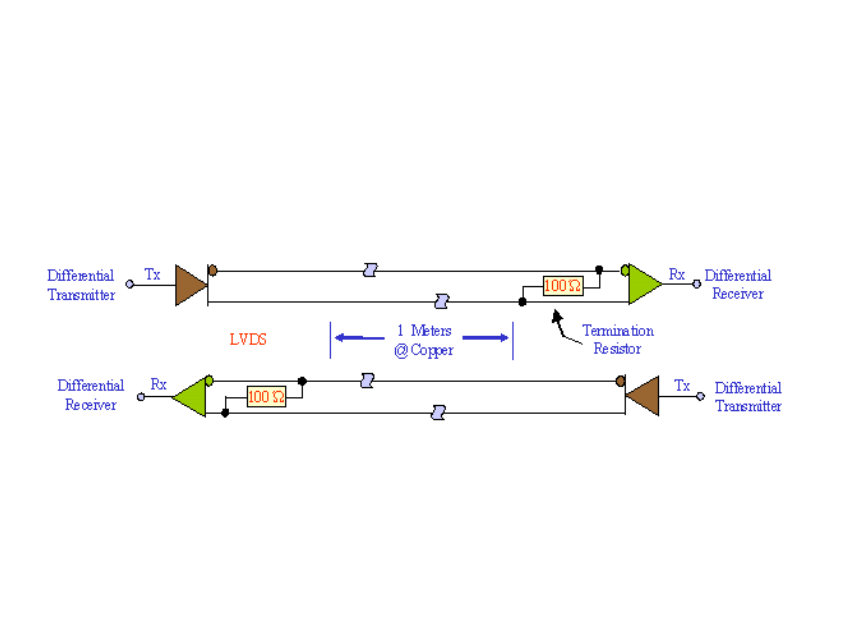

Pojedyncze połączenie LVDS

25

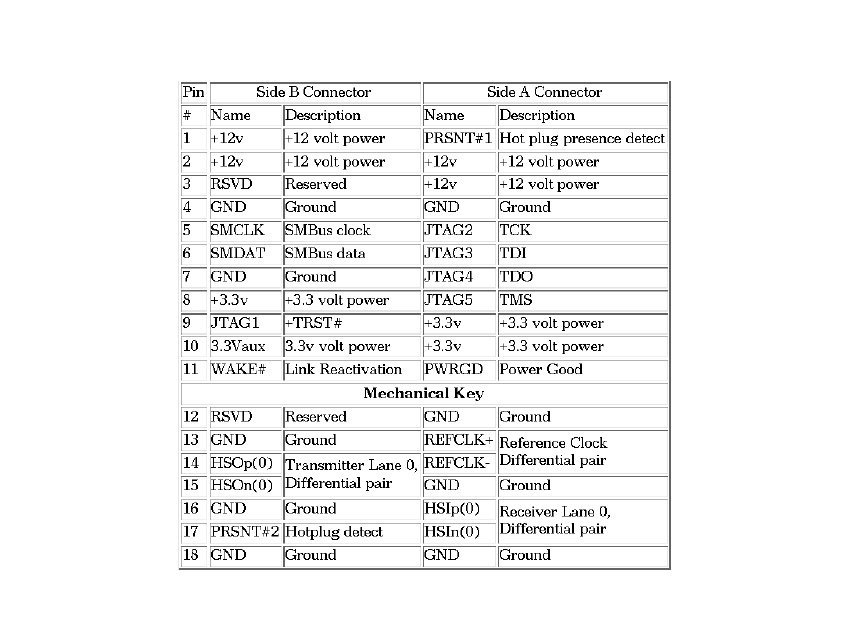

Wyprowadzenia 1x

SMCLK, SMDAT - System Management Bus

26

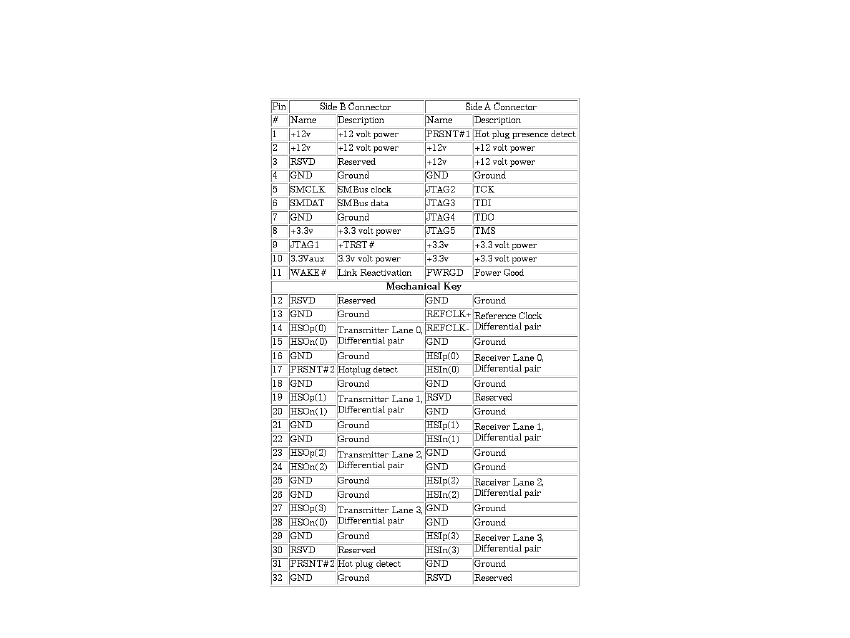

Wyprowadzenia 4x

27

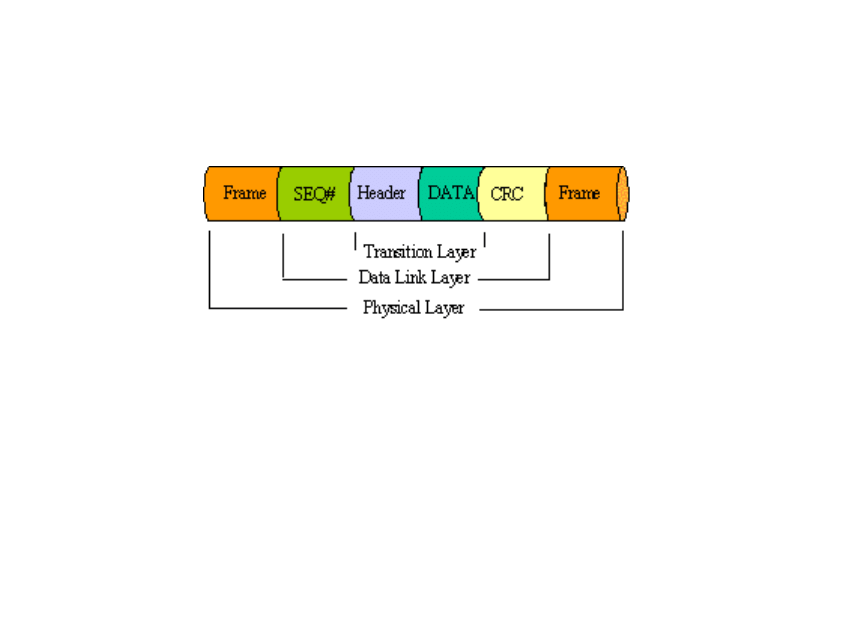

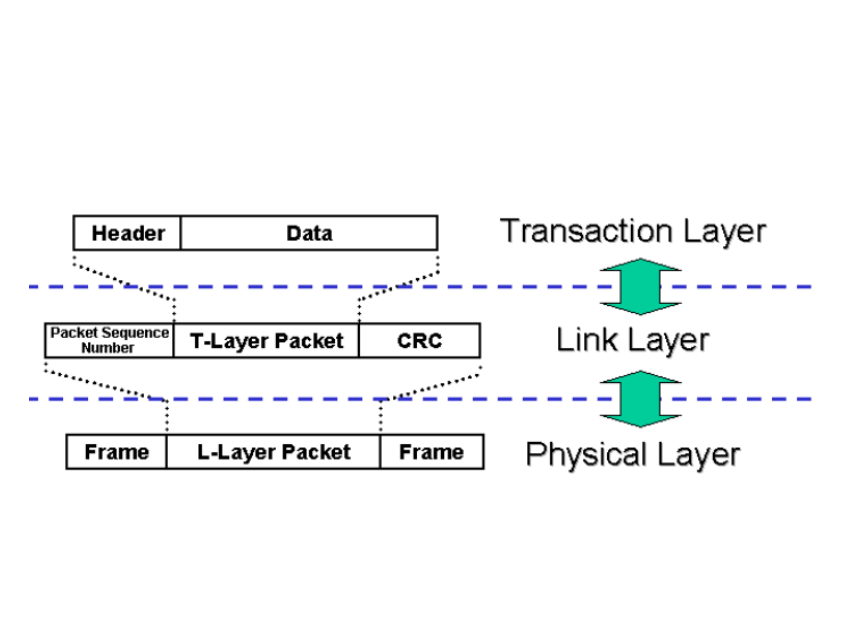

Protokół transmisyjny

1-byte Start-of-Frame

2-byte Sequence Number

16 or 20-byte Header

0 to 4096-byte Data field

0 to 4-byte ECRC field - End-to-end Cyclic Redundancy Check (32 bity)

4-byte LCRC - Local Cyclic Redundancy Check (32 bity)

1-byte End-of Frame

28

Warstwy

29

Physical Layer

30

Zrównoleglenie przesyłania danych

31

Idea

32

Wyszukiwarka

Podobne podstrony:

19 Liberalny system władzy w Europie

LINUX, SZKOLNE PLIKI-mega zbiory (od podstawówki do magisterki), Systemy operacyjne

08 magistrale systemowe

Podstawy informatyki, Magistrale systemowe komputera PC, Magistrale systemowe komputera PC

system polityczny(1), WPiA Administracja, Magisterka, System polityczny państwa

Magistrale systemowe

SPP, WPiA Administracja, Magisterka, System polityczny państwa

spp0, WPiA Administracja, Magisterka, System polityczny państwa

Pytanie 19, Magisterka materiały, Farmakologia

08 magistrale systemoweid 7441

[19]Zabezpieczenie systemu operacyjnego 1 2

SOP UE-II 19[1].12.2009, Dokumenty STUDIA SKANY TEXT TESTY, ADMINISTRACJA UNIWEREK WROCŁAW MAGISTER,

19 zapis binarny systemow analogowych

SYSTEM OCHRON PRAWNEJ Wykla 17[1].10.2009, Dokumenty STUDIA SKANY TEXT TESTY, ADMINISTRACJA UNIWEREK

więcej podobnych podstron