Architektura komputerów

Tydzień 8

Magistrale systemowe

Magistrala

●

Układy składające się na komputer

(procesor, pamięć, układy we/wy)

muszą się ze sobą komunikować, czyli

być połączone.

●

Układy łączymy ze sobą ścieżkami

zapewniającymi przesyłanie danych

między nimi.

●

Magistrala to zestaw ścieżek łączących

różne układy. Jest ona wspólna dla

wszystkich lub części układów.

Struktura magistrali

●

Magistrala systemowa składa się z

kilkudziesięciu lub nawet kilkuset

oddzielnych linii.

●

Linie te dzielimy na trzy zasadnicze

grupy:

–

danych – ścieżki do przesyłania danych

–

adresowe – określają źródło lub

przeznaczenie dla danych (adres pamięci

lub urządzenie wejścia/wyjścia)

–

sterowania – regulują dostęp do magistrali

Linie sterowania

–

Zapis w pamięci

–

Odczyt z pamięci

–

Zapis do wyjścia

–

Odczyt z wejścia

–

Potwierdzenie przesłania

–

Zapotrzebowanie na magistralę

–

Rezygnacja z magistrali

–

Żądanie przerwania

–

Potwierdzenie przerwania

–

Zegar

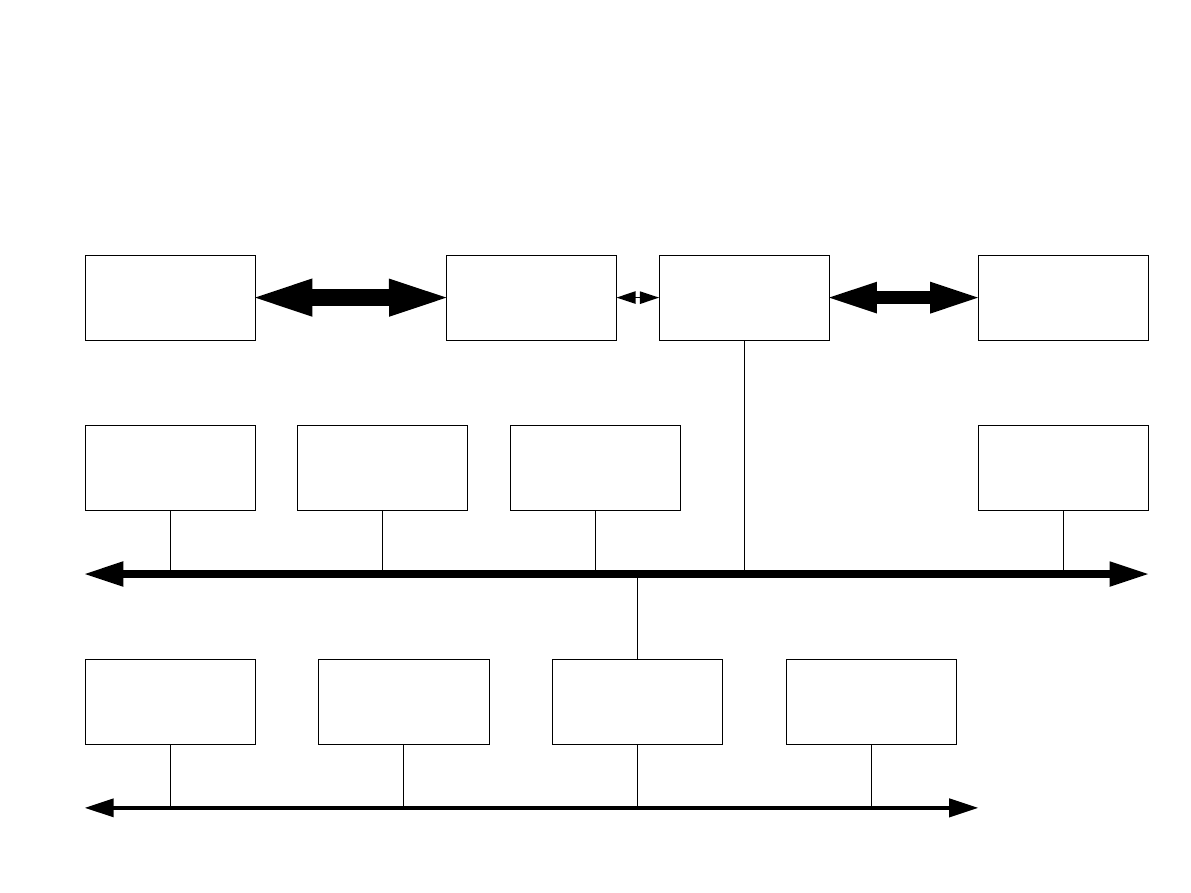

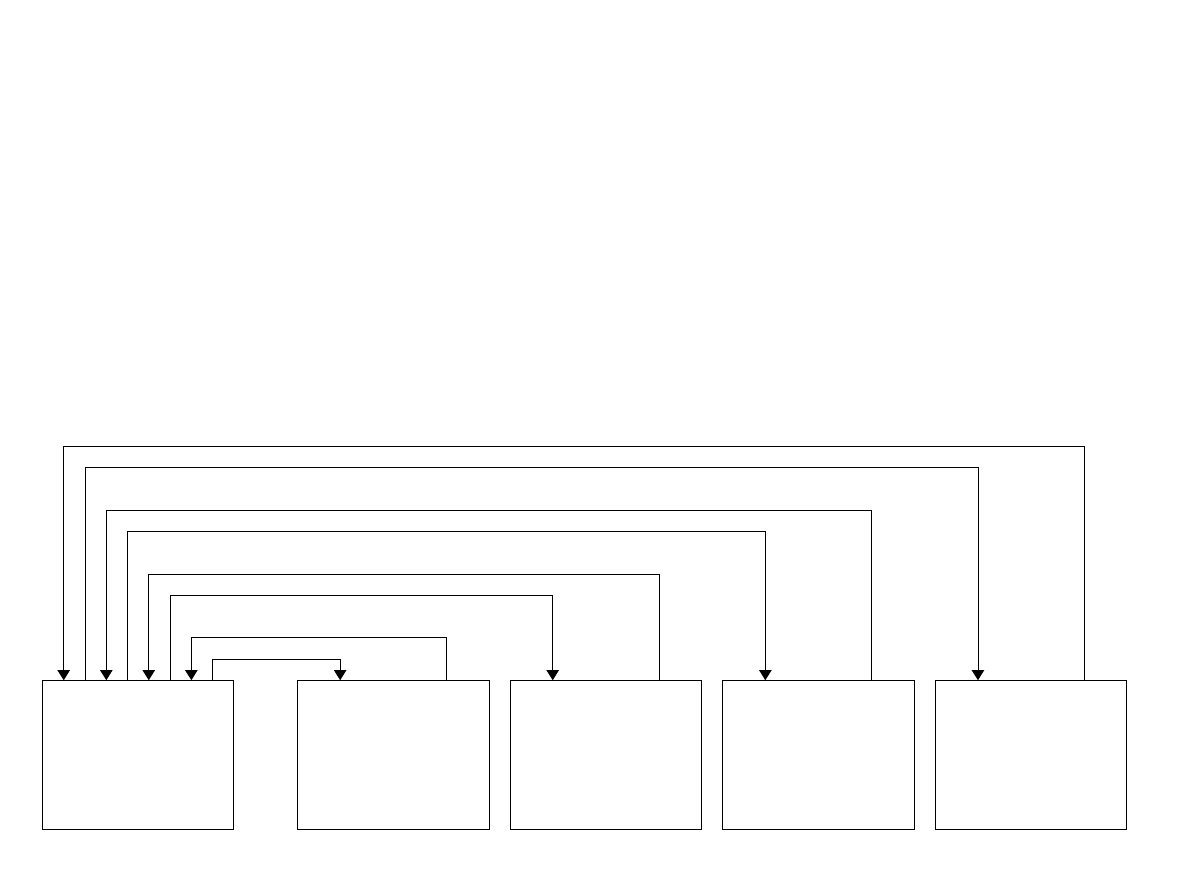

Hierarchiczne struktury

wielomagistralowe

●

Im więcej urządzeń dołączonych do

magistrali, tym większe opóźnienia

propagacji, co może zauważalnie

zmniejszyć wydajność.

●

Jeśli zapotrzebowanie na przesyłanie

danych jest bliskie pojemności

magistrali, staje się ona wąskim

gardłem – wprowadza opóźnienia.

●

Rozwiązaniem jest stosowanie wielu

magistral odpowiednio połączonych.

Szybkie magistrale

hierarchiczne

Procesor

Pamięć

podręczna

Sterownik

pamięci

Pamięć

główna

SCSI

IEEE 1394

Grafika

LAN

Porty

szeregowe

Porty

równoległe

Interfejs

szyny

Porty

PS/2

Magistrala

lokalna

Magistrala

systemowa

Magistrala szybkiego przesyłania

Szyna rozszerzeń

Rodzaje magistral

●

Linie magistrali można podzielić na dwa

rodzaje:

–

specjalizowane

–

multipleksowane

●

Linie specjalizowane są przeznaczine

do realizowania jednej, wyznaczonej

funkcji, np. linia adresowa lub danych.

●

Linie multipleksowane mogą spełniać

różne role, np. podanie adresu w jednej

jednostce czasu, a w następnej danych.

Arbitraż

●

Jeśli do magistrali może być

przyłączonych więcej niż dwa układy

musi istnieć sterownik zwany arbitrem.

●

Arbiter przydziela czas magistrali

poszczególnym układom zgłaszającym

zapotrzebowanie na przesłanie danych.

●

Czas przydzielony może być

koordynowany asynchronicznie lub

synchronicznie.

Magistrala PCI

●

PCI to skrót od Peripheral Component

Interconnect

●

Magistrala PCI może mieć 32 lub 64 linie

danych.

●

Może pracować z częstotliwością 33 lub

66 MHz.

●

Magistrala PCI jest zestandaryzowana i

może być używana w komputerach o

różnych architekturach (Intel x86,

PowerPC i innych).

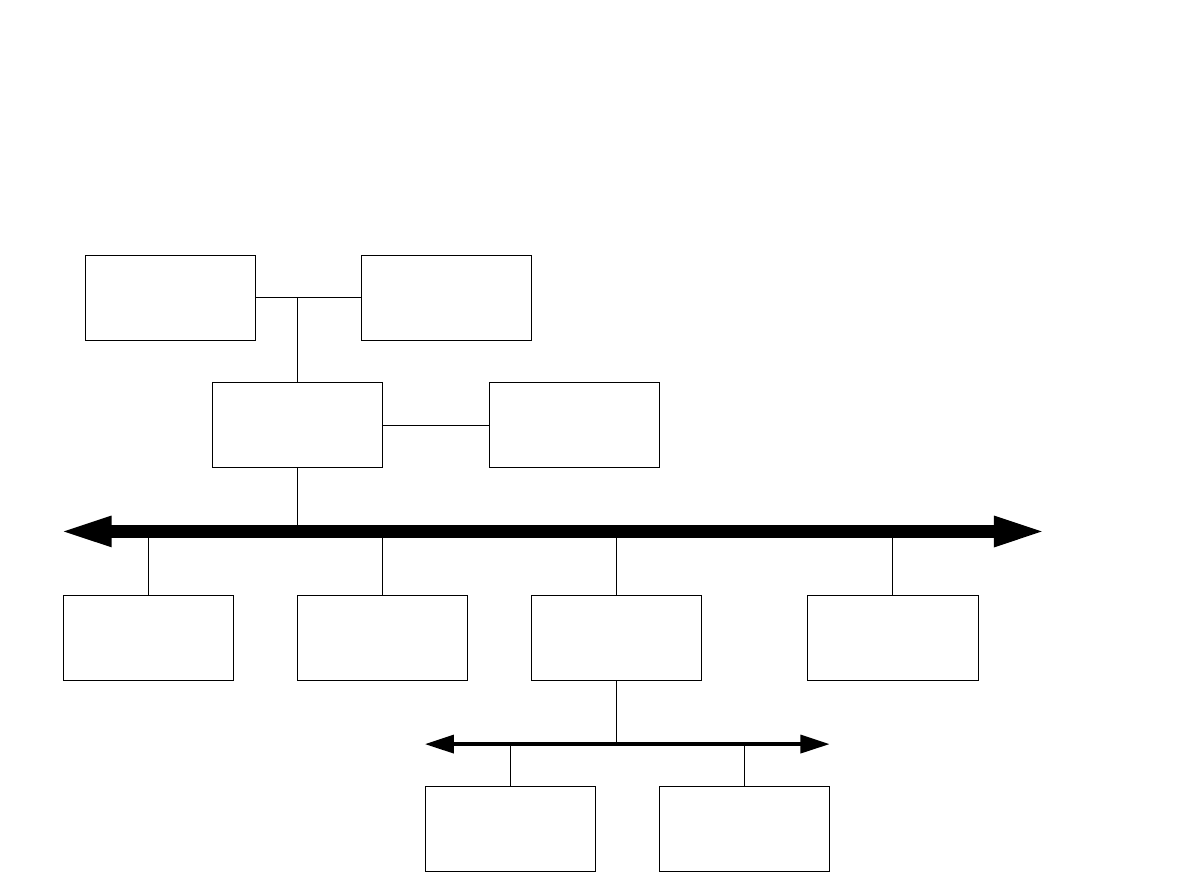

PCI w komputerach biurowych

Procesor

Pamięć

podręczna

Sterownik

pamięci

Pamięć

główna

LAN

IDE

Most szyny

rozszerzeń

Porty

szeregowe

Port

równoległy

Grafika

Magistrala PCI

Magistrala rozszerzeń

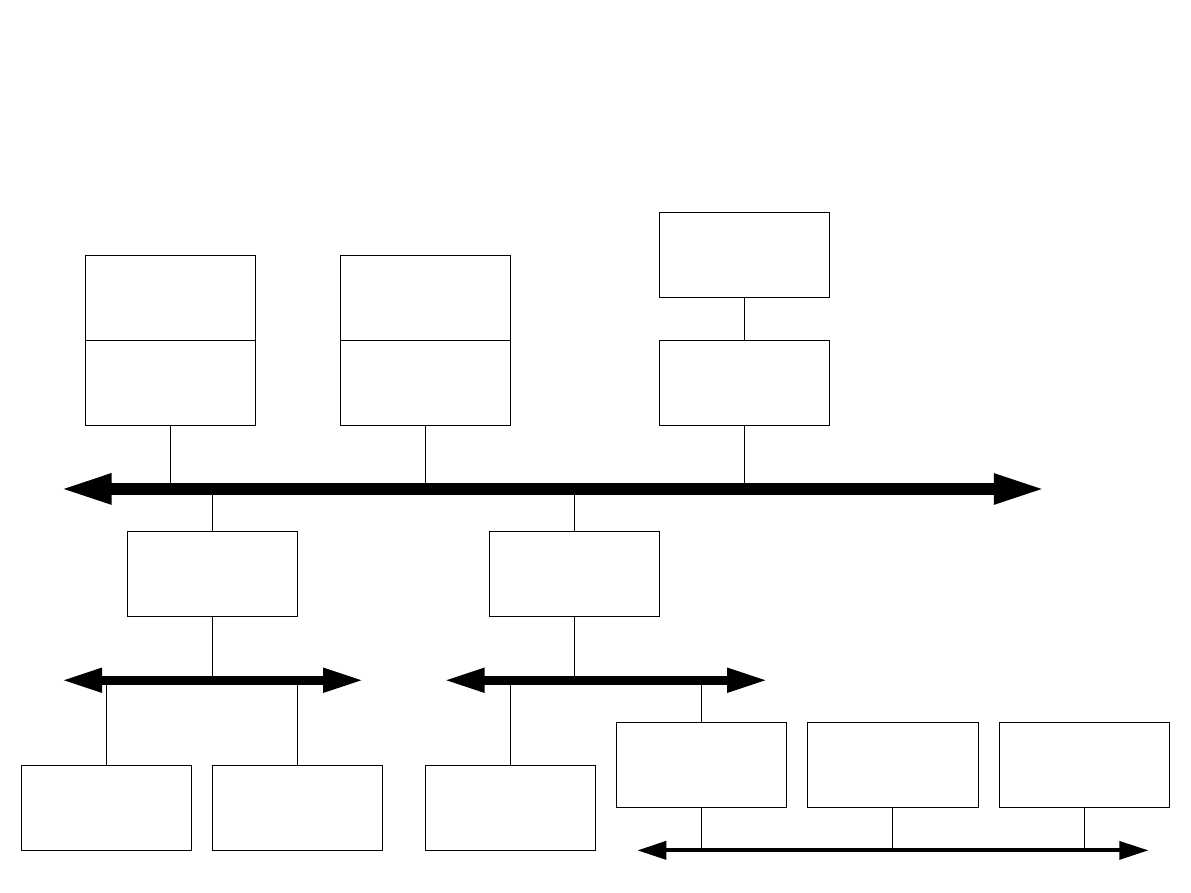

PCI w serwerach

Procesor 0

Pamięć

podręczna

Sterownik

pamięci

Pamięć

główna

LAN

SCSI

Most szyny

rozszerzeń

Porty

szeregowe

Port

równoległy

Grafika

Magistrala PCI

Magistrala rozszerzeń

Procesor 1

Pamięć

podręczna

Most PCI

Most PCI

Magistrala PCI

Magistrala systemowa

Struktura magistrali PCI

●

Linie magistrali PCI można podzielić na

następujące grupy:

–

systemowe (zegar, zerowanie)

–

adresu i danych (32 multipleksowane linie

dla adresów i danych)

–

sterowania interfejsu

–

arbitrażowe

–

informacje o błędach

–

opcjonalne linie przerwań

–

opcjonalne rozszerzenia 64 bitowe

(dodatkowe 32 multipleksowane linie

adresów i danych)

–

opcjonalne obsługi pamięci podręcznej

–

opcjonalne testowania

Działanie magistrali PCI

●

Przesyłanie danych odbywa się w formie

transakcji między inicjatorem

transmisji a celem.

●

Inicjator domagając się sterowania

magistralą określa typ transakcji do

przeprowadzenia wysyłając jeden z

rozkazów PCI.

●

Każde przesłanie danych to jedna

transakcja składająca się z jednego

cyklu adresowego i jednego lub więcej

faz przesyłania danych.

Rozkazy PCI

–

potwierdzenie przerwania

–

cykl specjalny

–

odczyt wejścia-wyjścia

–

zapis wejścia-wyjścia

–

odczyt pamięci

–

linia odczytu pamięci

–

zwielokrotniony odczyt pamięci

–

zapis w pamięci

–

zapis w pamięci i unieważnienie

–

odczyt konfiguracji

–

zapis konfiguracji

–

cykl podwójnego adresu

Arbitraż PCI

●

Każdy moduł ma przypisane oddzielne

sygnały zapotrzebowania (REQ) i

udostępniania (GNT) do arbitra.

Arbiter

PCI

GNT REQ

Urządzenie

PCI

GNT REQ

Urządzenie

PCI

GNT REQ

Urządzenie

PCI

GNT REQ

Urządzenie

PCI

Wyszukiwarka

Podobne podstrony:

08 magistrale systemowe

08 fuel system

LINUX, SZKOLNE PLIKI-mega zbiory (od podstawówki do magisterki), Systemy operacyjne

Kolokwium Zal Pr Strukturalne 2007-08, Studia, Systemy operacyjne

C.W.iS. - lab.3, Studia - IŚ - materiały, Semestr 08 (1) (magisterka), Chemia wody i ścieków - lab

C.W.iS. - lab.2, Studia - IŚ - materiały, Semestr 08 (1) (magisterka), Chemia wody i ścieków - lab

C.W.iS. - lab.5, Studia - IŚ - materiały, Semestr 08 (1) (magisterka), Chemia wody i ścieków - lab

C.W.iS. - lab.4, Studia - IŚ - materiały, Semestr 08 (1) (magisterka), Chemia wody i ścieków - lab

Podstawy informatyki, Magistrale systemowe komputera PC, Magistrale systemowe komputera PC

system polityczny(1), WPiA Administracja, Magisterka, System polityczny państwa

Stosunki polska Bia-oru- 90-08', magisterka, magisterka

C.W.iS. - lab.1, Studia - IŚ - materiały, Semestr 08 (1) (magisterka), Chemia wody i ścieków - lab

Magistrale systemowe

SPP, WPiA Administracja, Magisterka, System polityczny państwa

spp0, WPiA Administracja, Magisterka, System polityczny państwa

praca-magisterska-wa-c-7441, Dokumenty(2)

CW 08 B Magistrala

więcej podobnych podstron