AK

Ćw. 8

Magistrala systemu komputerowego

Cel ćwiczenia: Zapoznanie się z magistralą systemu komputerowego na przykładzie prostego systemu z procesorem

8-bitowym.

Sprzęt i oprogramowanie: System CA80, komputer PC z systemem Windows, analizator stanów logicznych,

program sterujący do analizatora

Materiały pomocnicze: Tabela kodów procesora 8080 (dostępne w pliku pdf), instrukcja analizatora (w j.

angielskim)

Magistrala systemu komputerowego składa

się miedzy innymi z następujących linii:

A0-A15

adres

D0-D7 dane

MR~

czytaj z pami

ę

ci

MW~

pisz do pami

ę

ci

I/OR~ czytaj z wej

ś

cia/wyj

ś

cia

I/OW~ pisz do wej

ś

cia/wyj

ś

cia

Polecenia:

1.

Podłącz analizator do magistrali zestawu CA80

2.

Skopiuj plik 8080Mag_0.LPF do katalogu w którym masz prawo zapisywać.

3.

Uruchom aplikację LogicPort i otwórz plik 8080Mag_0.LPF

Plik ten te konfiguruje analizator w następujący sposób:

Wejścia 0-15

ADR15-ADR0

Adres

Wejścia 16-23

DATA7-DATA0

Dane

Wejście 24

CLK

Zegar

Wejście 25

MR/

Czytaj z pamięci

Wejście 26

MW/

Pisz do pamięci

Wejście 27

IOR/

Czytaj z wejścia-wyjścia

Wejście 28

IOW/

Pisz do wejścia-wyjścia

Wyzwalanie opadającym zboczem MR/ gdy na liniach adresowych jest 8000H.( Jeżeli nasz program zaczyna się od

adresu 8000H to wyzwolenie nastąpi w momencie pobierania pierwszego rozkazu.)

Pre-Trigger Buffer (bufor przed wyzwoleniem) 1% . 99% pojemności bufora przeznaczymy na zarejestrowanie, co

działo się po wyzwoleniu analizatora, a 1% na zarejestrowanie co się działo przed wyzwoleniem.

Sample Rate 50 MHz.( Częstotliwość próbkowania).

4.

Napisz programy i zaobserwuj ich działanie korzystając z analizatora:

a.

Wysyłający Twoje inicjały do portu 83H.

b.

Wywołujący podprogram.

c.

Zapisujący na stosie: znaczniki, rejestr A oraz rejestry B i C

5. Zaprojektuj 4 bitowy

układ wyjścia podłączany do magistrali. Ogólną strukturę układu pokazano

na rysunku1.

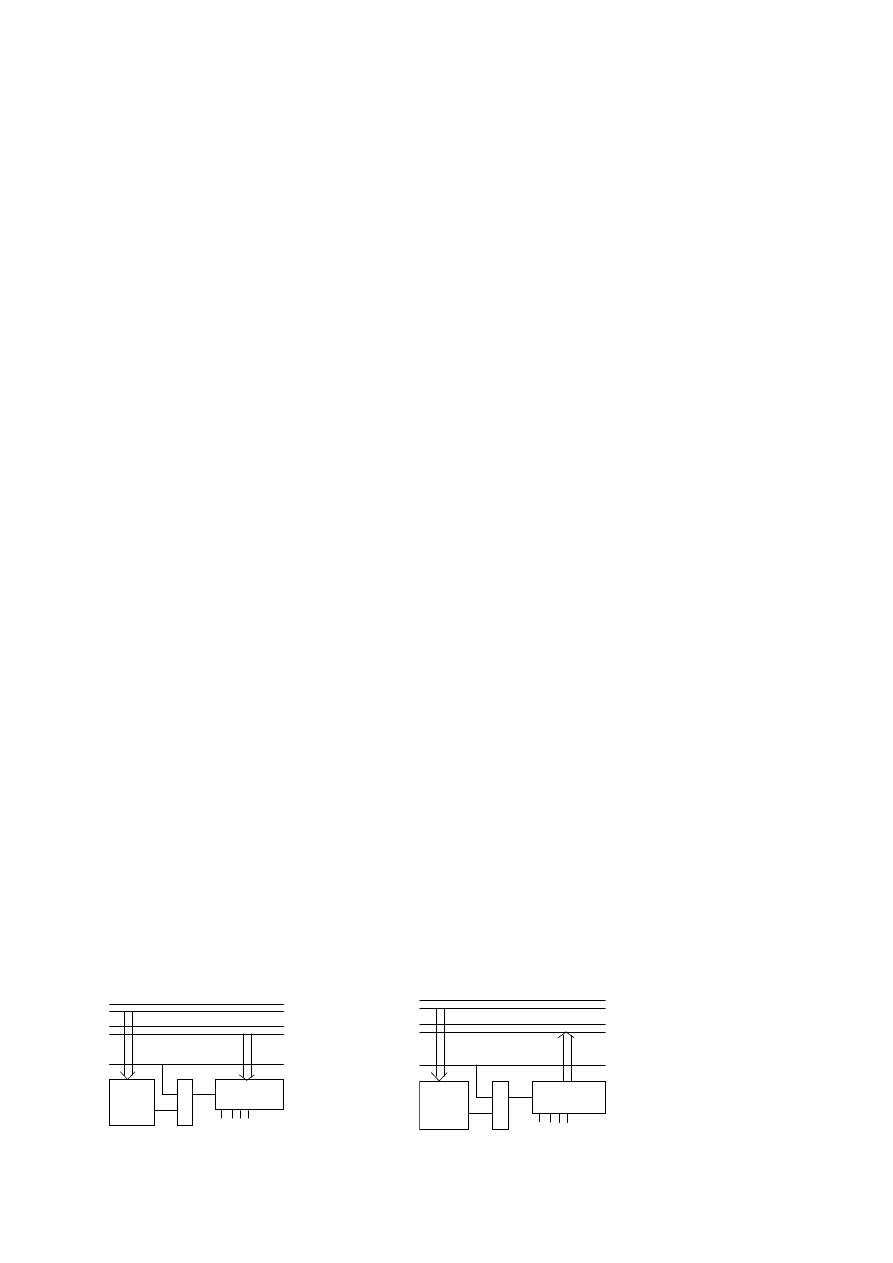

Rys. 1. Układ Wyjścia. 1-dekoder adresu,

Rys. 2. Układ wejścia.

1-dekoder adresu, 2-sterowanie wpisem,3-rejestr 1-dekoder adresu, 2-ster.buforem, 3 -bufor trójstanowy

Adres

IOW~

Dane

1

2

3

Adres

IOR~

Dane

1

2

3

Zaprojektuj elementy 1, 2 i 3 dla podanego adresu. Wykorzystaj dostępne bramki i przerzutniki

6. Zaprojektuj 4-bitowy układ wejścia podłączany do magistrali. Ogólną strukturę układu pokazano na rysunku2.

Wykorzystaj dostępne bramki

Wyszukiwarka

Podobne podstrony:

1272 PE cw 08 prezentacja

Cw 08 SVD

cad 1 I Cw 08 2014

Cw 08 10 Badania epidemiologiczne

II D+W Nowy Świat wyk+ćw 08-09, Archeo, ARCHEOLOGIA NOWEGO ŚWIATA

CW 08 id 122562 Nieznany

08 magistrale systemowe

ĆW 08 10 Obsługa Oscyloskopu

ćw 08 03, 15 03

Cw 08 filtr z ujemna pojemnoscia

MD cw 08 id 290129 Nieznany

ĆW 08

Ćw 08

TEORIA WYCHOWANIA ćw 08.10.08, pedagogika, semestr I, teoria wychowania

C.W.iS. - lab.3, Studia - IŚ - materiały, Semestr 08 (1) (magisterka), Chemia wody i ścieków - lab

C.W.iS. - lab.2, Studia - IŚ - materiały, Semestr 08 (1) (magisterka), Chemia wody i ścieków - lab

C.W.iS. - lab.5, Studia - IŚ - materiały, Semestr 08 (1) (magisterka), Chemia wody i ścieków - lab

C.W.iS. - lab.4, Studia - IŚ - materiały, Semestr 08 (1) (magisterka), Chemia wody i ścieków - lab

więcej podobnych podstron