Historia rozwoju

Historia rozwoju

Historia rozwoju

Historia rozwoju

H stor a rozwoju

H stor a rozwoju

elektroniki

elektroniki

H stor a rozwoju

H stor a rozwoju

elektroniki

elektroniki

elektroniki

elektroniki

elektroniki

elektroniki

6 marca 2011

Wojciech Kucewicz

3

Kilka dat z historii

Kilka dat z historii

Kilka dat z historii

Kilka dat z historii

1850

1850 -- George Boole opracował zasady algebry Boole'a, czyli operacji na

George Boole opracował zasady algebry Boole'a, czyli operacji na

wart ściach l icznych "prawda" i "fałsz" (l iczna 1 i 0)

wart ściach l icznych "prawda" i "fałsz" (l iczna 1 i 0)

wartościach logicznych "prawda" i "fałsz" (logiczna 1 i 0).

wartościach logicznych "prawda" i "fałsz" (logiczna 1 i 0).

1874

1874 -- Emil Baudot skonstuował telegraf z klawiaturą alfanumeryczną. Każdy

Emil Baudot skonstuował telegraf z klawiaturą alfanumeryczną. Każdy

znak był zakodowany jako kombinacja pięciu elementów

znak był zakodowany jako kombinacja pięciu elementów -- dodatnich i

dodatnich i

znak był zakodowany jako kombinacja pięciu elementów

znak był zakodowany jako kombinacja pięciu elementów -- dodatnich i

dodatnich i

ujemnych impulsów prądu w linii. "Pięciobitowy" alfabet Baudota składał się z

ujemnych impulsów prądu w linii. "Pięciobitowy" alfabet Baudota składał się z

32 znaków. Na cześć Baudota jednostkę prędkości transmisji

32 znaków. Na cześć Baudota jednostkę prędkości transmisji -- jeden

jeden

element (bit) na sekundę

element (bit) na sekundę -- nazwano bodem (ang baud)

nazwano bodem (ang baud)

element (bit) na sekundę

element (bit) na sekundę nazwano bodem (ang. baud).

nazwano bodem (ang. baud).

Nawiasem mówiąc, największy hołd świat złożył Baudotowi gdy w roku 1880

Nawiasem mówiąc, największy hołd świat złożył Baudotowi gdy w roku 1880

jego pięcioelementowe znaki przyjęto jako międzynarodowy alfabet

jego pięcioelementowe znaki przyjęto jako międzynarodowy alfabet

telegraficzny ITA 1 (International Telegraph Alphabet nr. 1). Nieco

telegraficzny ITA 1 (International Telegraph Alphabet nr. 1). Nieco

g

y

(

g p

p

)

g

y

(

g p

p

)

ulepszony alfabet Baudota, oznaczony ITA

ulepszony alfabet Baudota, oznaczony ITA--2, gdzieniegdzie nadal jest w

2, gdzieniegdzie nadal jest w

użyciu.

użyciu.

6 marca 2011

Wojciech Kucewicz

4

Kilka dat z historii

Kilka dat z historii

Kilka dat z historii

Kilka dat z historii

1946

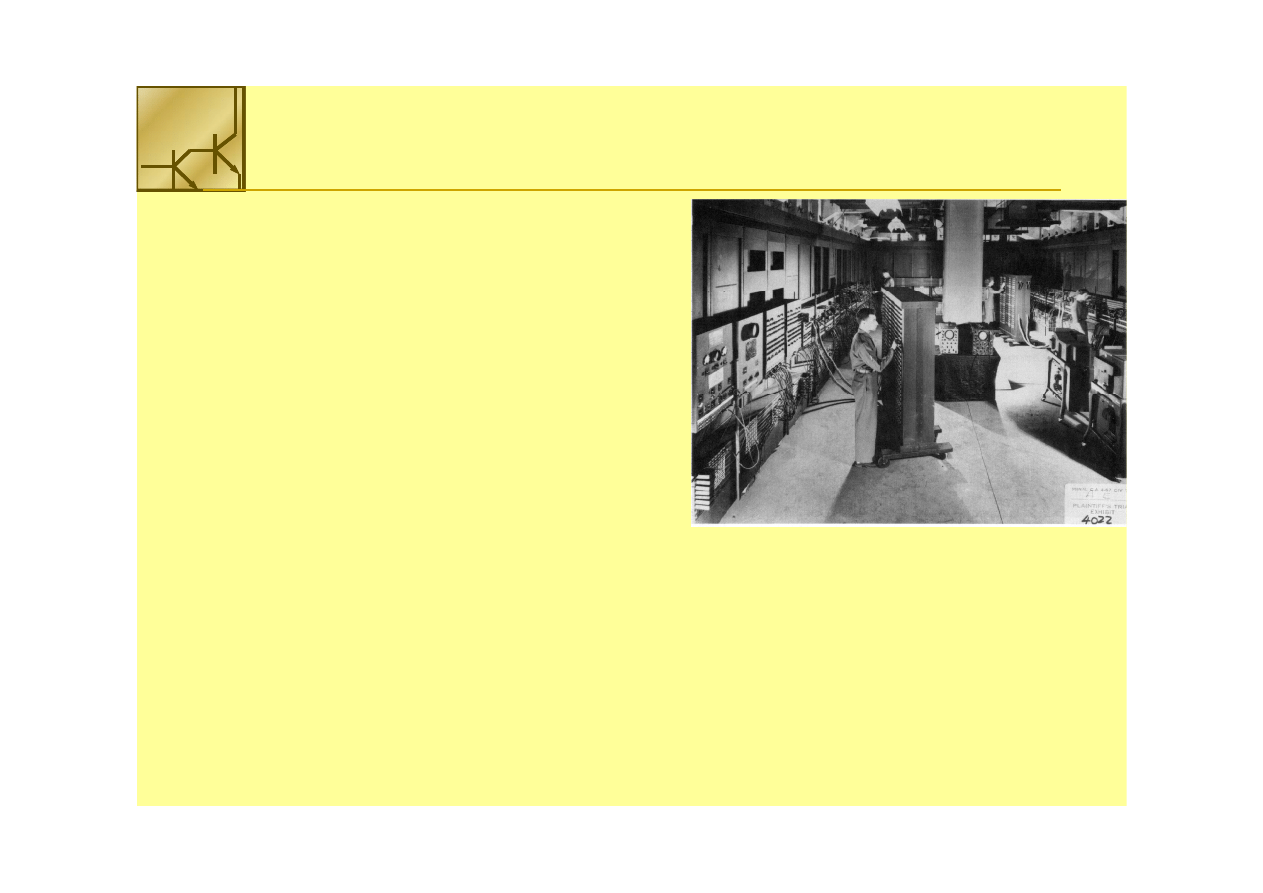

1946 -- Powstał słynny ENIAC (Electronic

Powstał słynny ENIAC (Electronic

Numerical

Numerical Integrator and Computer).

Integrator and Computer).

Komputer zajmował pomieszczenie o

Komputer zajmował pomieszczenie o

p

j

p

p

j

p

wymiarach 12 na 6 m

wymiarach 12 na 6 m

22

. Składał się z 42

. Składał się z 42

szaf z blachy stalowej

szaf z blachy stalowej -- każda miała 3 m

każda miała 3 m

wysokości, 60 cm szerokości i 30 cm

wysokości, 60 cm szerokości i 30 cm

głębokości. Całkowicie lampowy ENIAC

głębokości. Całkowicie lampowy ENIAC

(19000 lamp) mógł wykonywać do 100 000

(19000 lamp) mógł wykonywać do 100 000

operacji na sekundę. Program był

operacji na sekundę. Program był

k d

t i d ł

h t bli

k d

t i d ł

h t bli

P d t

j

d i i ł b ć

dl B lli ti R

h L b

t

P d t

j

d i i ł b ć

dl B lli ti R

h L b

t

kodowany w postaci dołączanych tablic

kodowany w postaci dołączanych tablic

funkcyjnych.

funkcyjnych.

Podstawowym jego zadaniem miała być praca dla Ballistic Research Laboratory:

Podstawowym jego zadaniem miała być praca dla Ballistic Research Laboratory:

obliczanie tablic dla artylerii, podających parametry trajektorii pocisku w zmiennych

obliczanie tablic dla artylerii, podających parametry trajektorii pocisku w zmiennych

warunkach. Później ENIAC był wykorzystywany między innymi do obliczeń związanych

warunkach. Później ENIAC był wykorzystywany między innymi do obliczeń związanych

z programem budowy bomby wodorowej, projektowania tuneli aerodynamicznych, a

z programem budowy bomby wodorowej, projektowania tuneli aerodynamicznych, a

6 marca 2011

Wojciech Kucewicz

5

p g

y

y

j, p j

y

y ,

p g

y

y

j, p j

y

y ,

nawet do obliczenia wartości liczby pi z dokładnością do tysiąca miejsc po przecinku.

nawet do obliczenia wartości liczby pi z dokładnością do tysiąca miejsc po przecinku.

Tranzystor bipolarny

Tranzystor bipolarny

Tranzystor bipolarny

Tranzystor bipolarny

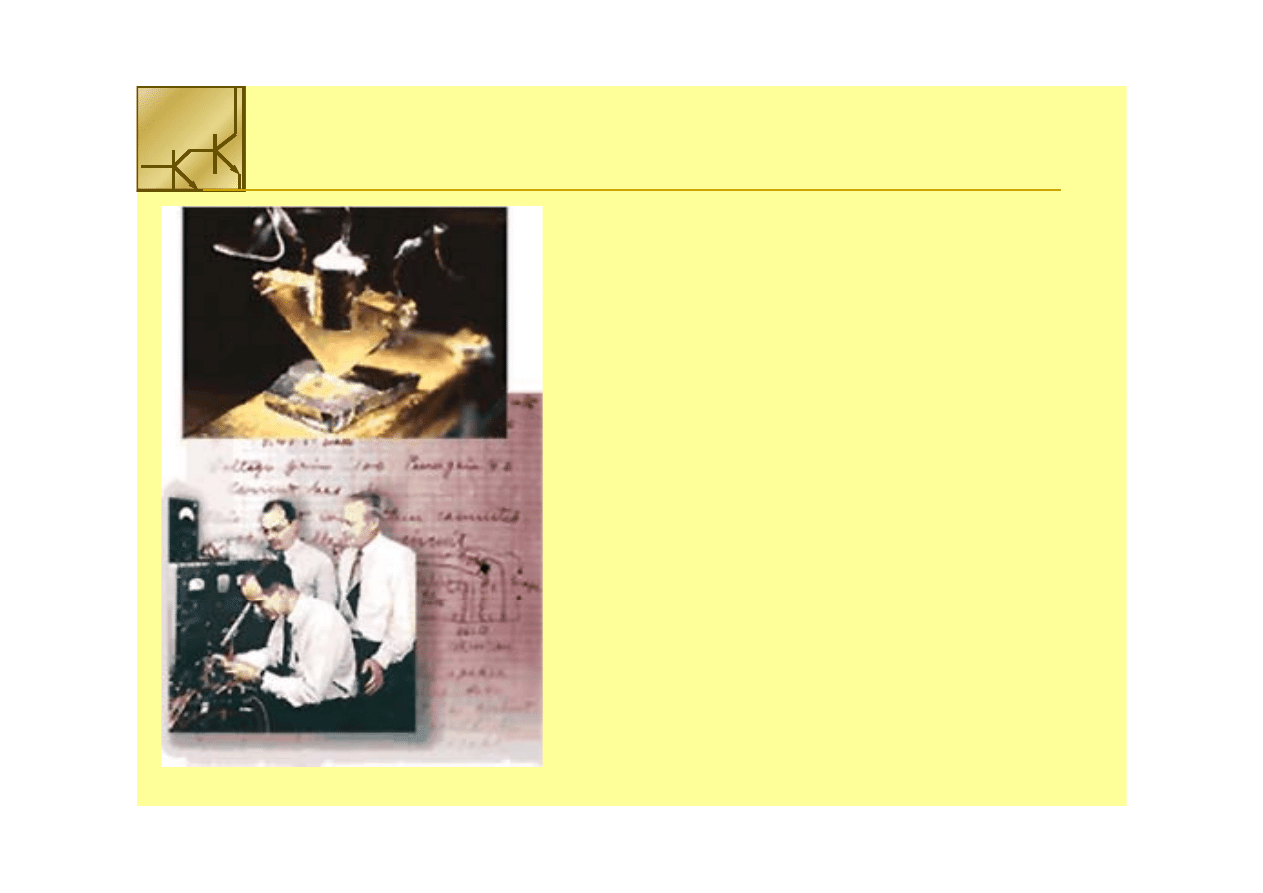

Tranzystor został wynaleziony w roku

Tranzystor został wynaleziony w roku

1947 w Laboratorium Bella (USA)

1947 w Laboratorium Bella (USA)

przez zespół:

przez zespół: John Bardeen, Walter

John Bardeen, Walter

przez zespół

przez zespół John Bardeen, Walter

John Bardeen, Walter

Brattain, and William Shockley

Brattain, and William Shockley. W roku

. W roku

1956 otrzymali Nagrodę Nobla.

1956 otrzymali Nagrodę Nobla.

J. Bardeen otrzymał również Nagrodę Nobla w roku

J. Bardeen otrzymał również Nagrodę Nobla w roku

1972 za wyjaśnienie zjawiska nadprzewodnictwa.

1972 za wyjaśnienie zjawiska nadprzewodnictwa.

6 marca 2011

Wojciech Kucewicz

6

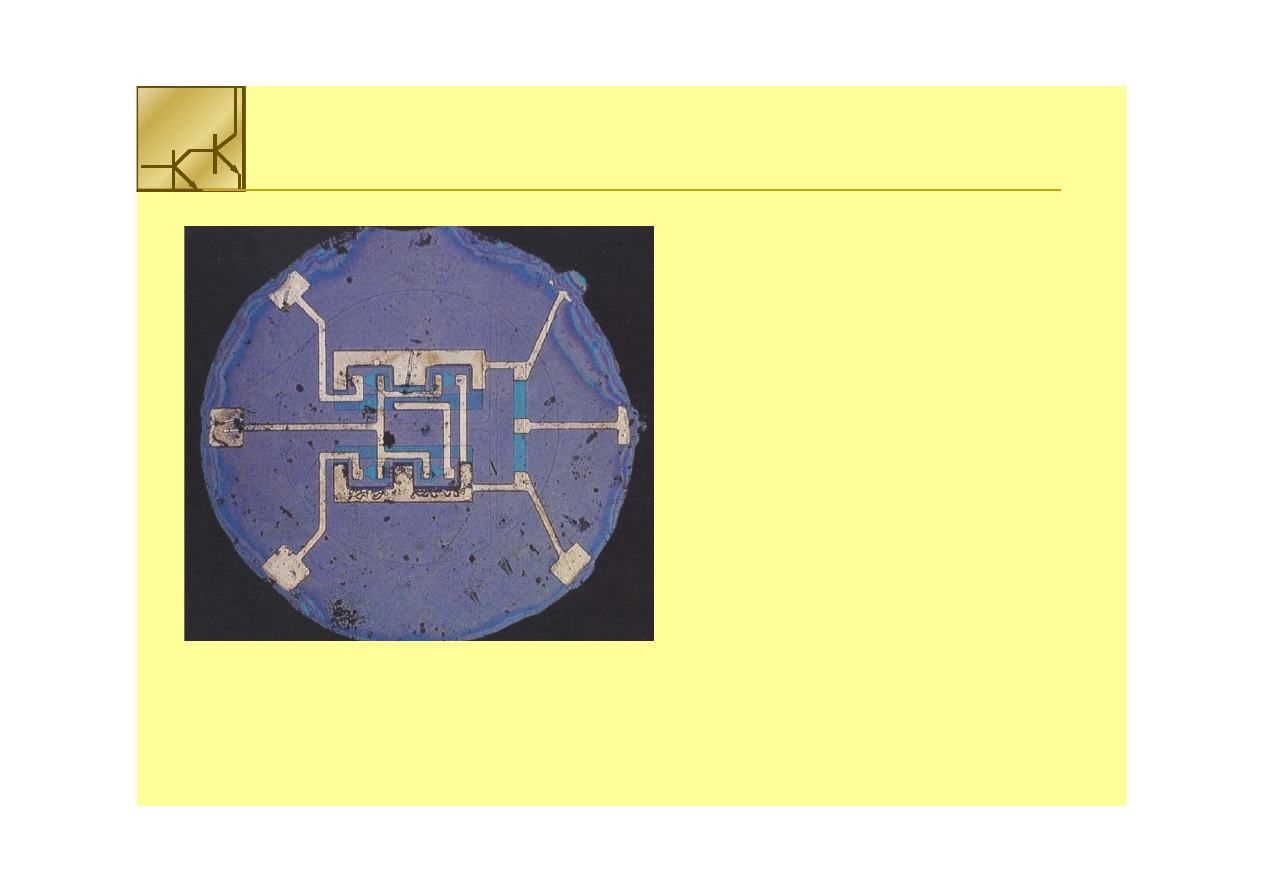

1958:

1958: Wynalezienie układu scalonego

Wynalezienie układu scalonego

1958:

1958: Wynalezienie układu scalonego

Wynalezienie układu scalonego

Z t ó

ukł du s l n

u ż

Z t ó

ukł du s l n

u ż

Za twórcę układu scalonego uważa

Za twórcę układu scalonego uważa

się Jack’a Kilby z Texas

się Jack’a Kilby z Texas

Instruments, który otrzymał za

Instruments, który otrzymał za

y

y

y

y

swój pomysł w roku 2000 Nagrodę

swój pomysł w roku 2000 Nagrodę

Nobla

Nobla

6 marca 2011

Wojciech Kucewicz

7

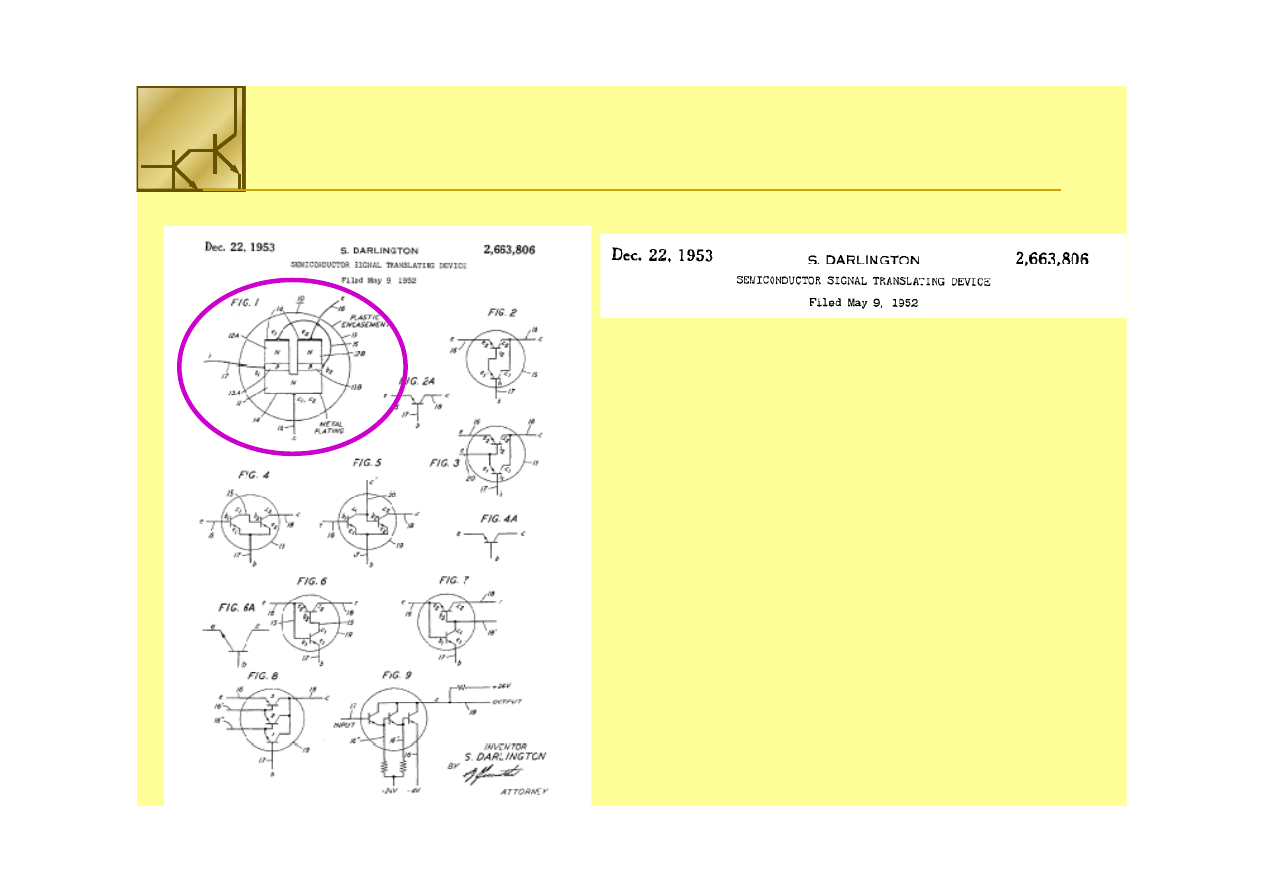

195

19533:

: Darlington Patent

Darlington Patent

195

19533:

: Darlington Patent

Darlington Patent

“Just after the transistor was invented at Bell Labs, Sidney

checked out for the weekend two of the few existing

transistors from the head of Bell Labs. Transistors were

not generally available and the head of the Labs kept the

few that had been made in his desk. Sidney played with

them at home on the weekend and discovered/invented

the Darlington pair. He realized that they could be put

in one package (“on one chip”), and that in fact any

number of transistors could be put in one package. The

next week he was encouraged to have the lawyers draw

next week he was encouraged to have the lawyers draw

up the patent application. He said it should be written

for any number in one package, but the lawyers only

wanted to do it for two—which is what was applied for.

As it turned out, if it had not been restricted to two

As it turned out, if it had not been restricted to two

transistors, Bell Labs and Dr. Darlington would receive

transistors, Bell Labs and Dr. Darlington would receive a

a

,

L

D . D

g

,

L

D . D

g

royalty on every IC chip made today

royalty on every IC chip made today

! Anyway, that’s

the story he tells.”

IEEE TRANSACTIONS ON CIRCUITS AND SYSTEMS—I: FUNDAMENTAL

THEORY AND APPLICATIONS, VOL. 46, NO. 1, JANUARY 1999

Darlington’s Contributions to Transistor Circuit Design

6 marca 2011

Wojciech Kucewicz

8

Darlington s Contributions to Transistor Circuit Design

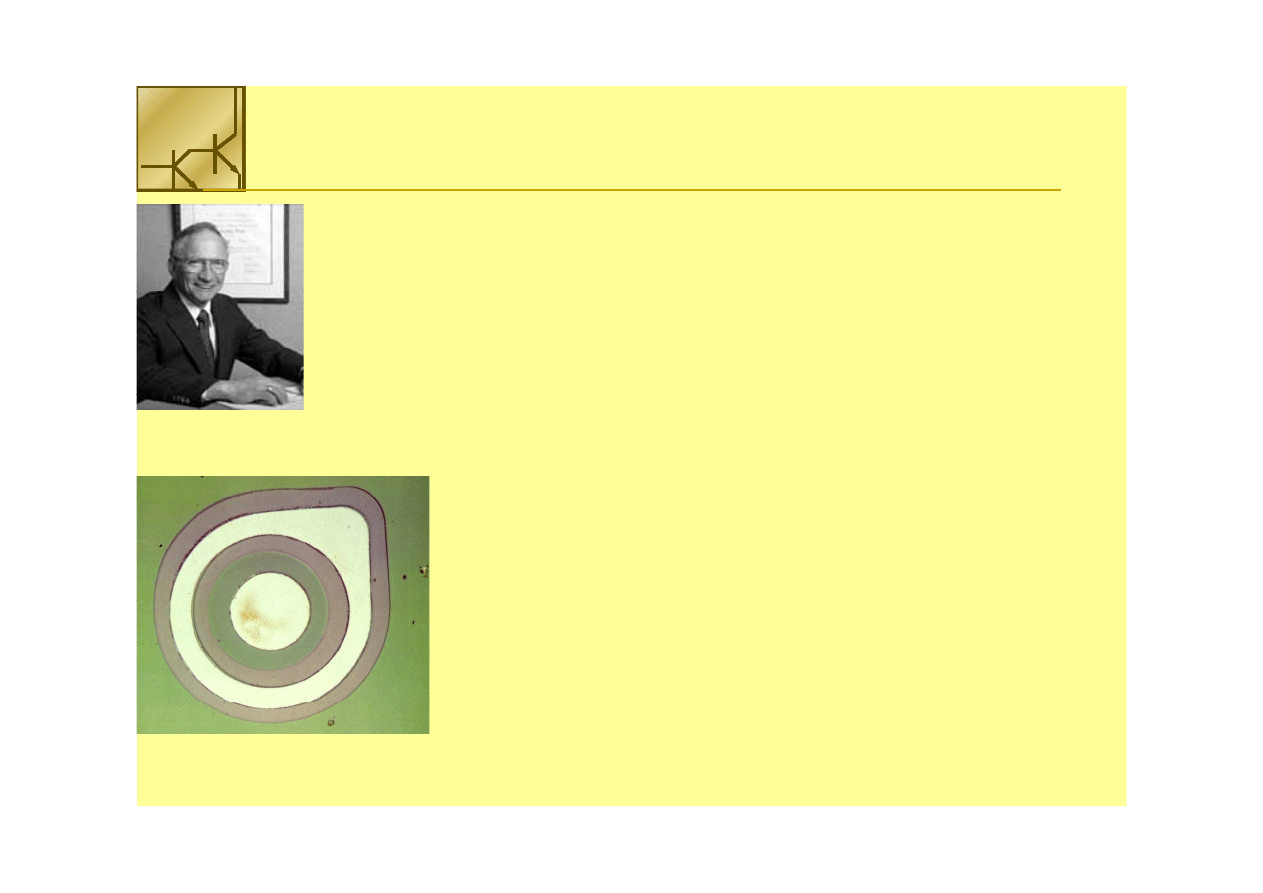

David A. Hodges,

Fellow, IEEE

Invention of the Integrated Circuit

Invention of the Integrated Circuit

Invention of the Integrated Circuit

Invention of the Integrated Circuit

1953

1953

1953

1953

Robert

Robert Noyce

Noyce get

get his

his PhD

PhD at

at MIT

MIT where

where „„few

few peaple

peaple

had

had even

even heardabout

heardabout the

the transistor

transistor””

1955

1955

1955

1955

He arriving to Shockley’s Lab

He arriving to Shockley’s Lab

1957

1957

1957

1957

He left Shockley’s and forms Fairchild

He left Shockley’s and forms Fairchild

Semiconductor with Jean Hoerni and Gordon

Semiconductor with Jean Hoerni and Gordon

Moore

Moore

1958

1958

1958

1958

Hoerni invents technique for diffusion impurities

Hoerni invents technique for diffusion impurities

into Silicon to build planar transistor and then using

into Silicon to build planar transistor and then using

SiO

SiO as insulator

as insulator

SiO

SiO

2

2

as insulator

as insulator

1959

1959

1959

1959

Noyce develops first true IC using planar

Noyce develops first true IC using planar

transistor diode

transistor diode--isolated silicon resistor SiO

isolated silicon resistor SiO

22

6 marca 2011

Wojciech Kucewicz

9

1959

1959

1959

1959

transistor, diode

transistor, diode isolated silicon resistor, SiO

isolated silicon resistor, SiO

22

insulation and evaporated metal wiring

insulation and evaporated metal wiring

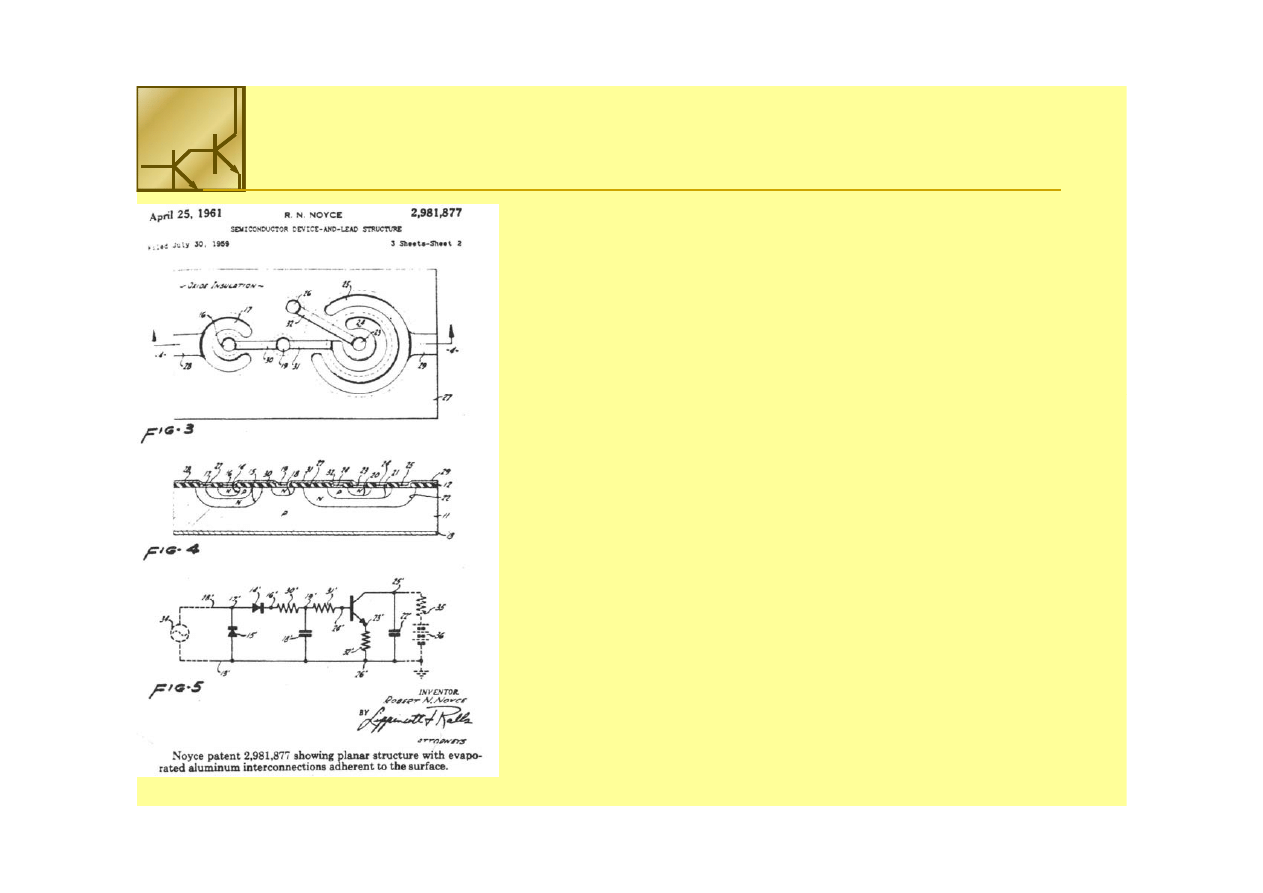

1959: Invention of the Integrated

1959: Invention of the Integrated

Circuit

Circuit

1959: Invention of the Integrated

1959: Invention of the Integrated

Circuit

Circuit

Noyce

Noyce develops

develops first

first true

true IC

IC

•• using

using

•• planar

planar transistor

transistor, ,

pp

•• diode

diode--isolated

isolated silicon

silicon resistor

resistor, ,

•• SiO

SiO

22

insulation

insulation

•• and

and evaporated

evaporated metal

metal wiring

wiring

and

and evaporated

evaporated metal

metal wiring

wiring

6 marca 2011

Wojciech Kucewicz

10

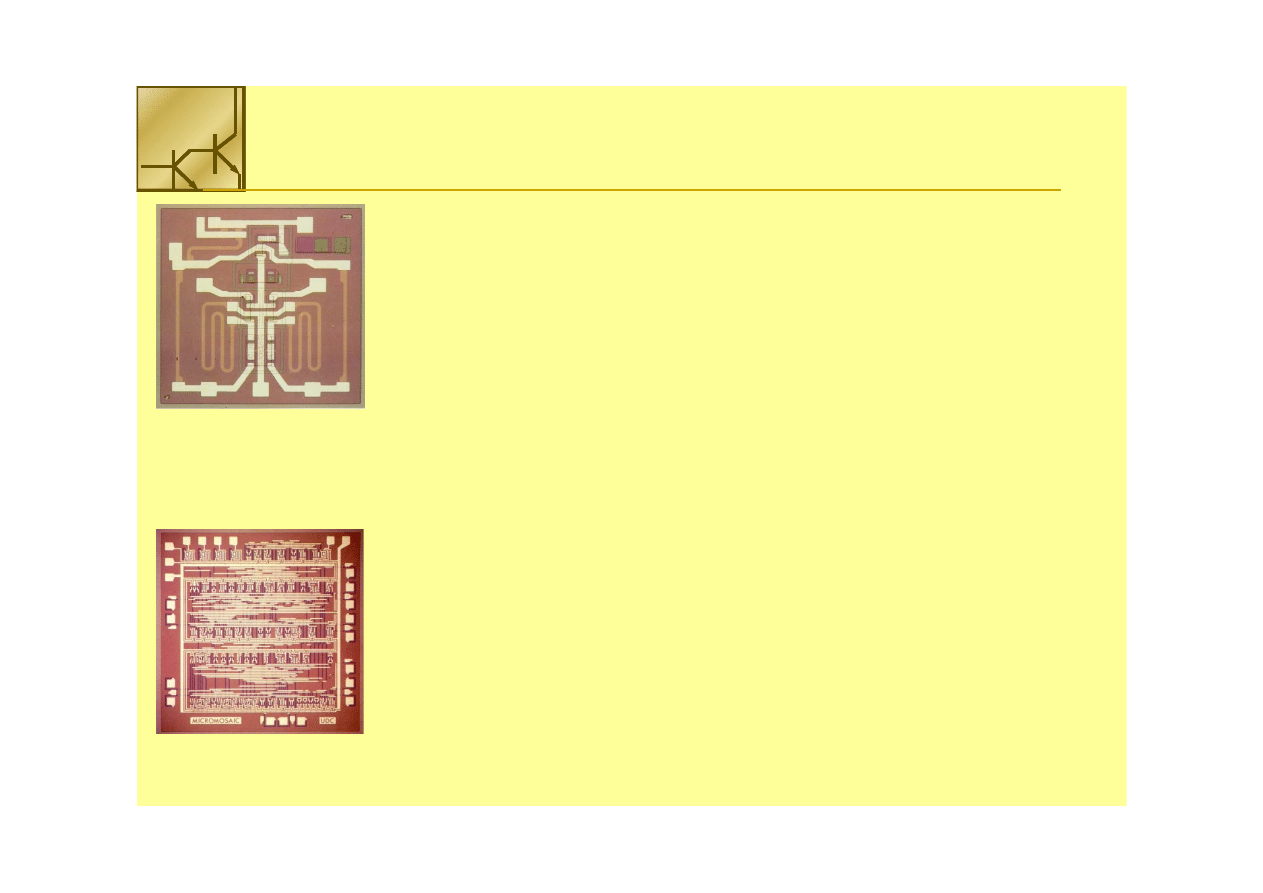

First Commercial Planar IC

First Commercial Planar IC 1961

1961

First Commercial Planar IC

First Commercial Planar IC 1961

1961

Fairchild

Fairchild ––

Dual

Dual flip

flip--flop

flop Chip

Chip

4 Transistors and 5 Resistors

4 Transistors and 5 Resistors

START OF SMALL SCALE

START OF SMALL SCALE

INTEGRATION

INTEGRATION

TECHNOLOGY

TECHNOLOGY

6 marca 2011

Wojciech Kucewicz

11

First Linear IC

First Linear IC

First Linear IC

First Linear IC

1964

1964

1964

1964

Fairchild

Fairchild

1964

1964

1964

1964

Fairchild

Fairchild

First

First Linear

Linear IC

IC The

The μμA

A 702 OPAMP

702 OPAMP

1967

1967

1967

1967

Fairchild

Fairchild

First

First IC

IC μμMOSAIC

MOSAIC -- ccreated

reated with

with

1967

1967

1967

1967

First

First IC

IC μμMOSAIC

MOSAIC ccreated

reated with

with

Computer

Computer--Aided Design

Aided Design..

Transistors (organized in

Transistors (organized in columns) could be

columns) could be

easily rewired using a

easily rewired using a two

two--layer

layer

6 marca 2011

Wojciech Kucewicz

12

y

g

y

g

yy

interconnect to create different

interconnect to create different circuits.

circuits.

This circuit

This circuit contains ~150 logic

contains ~150 logic gates.

gates.

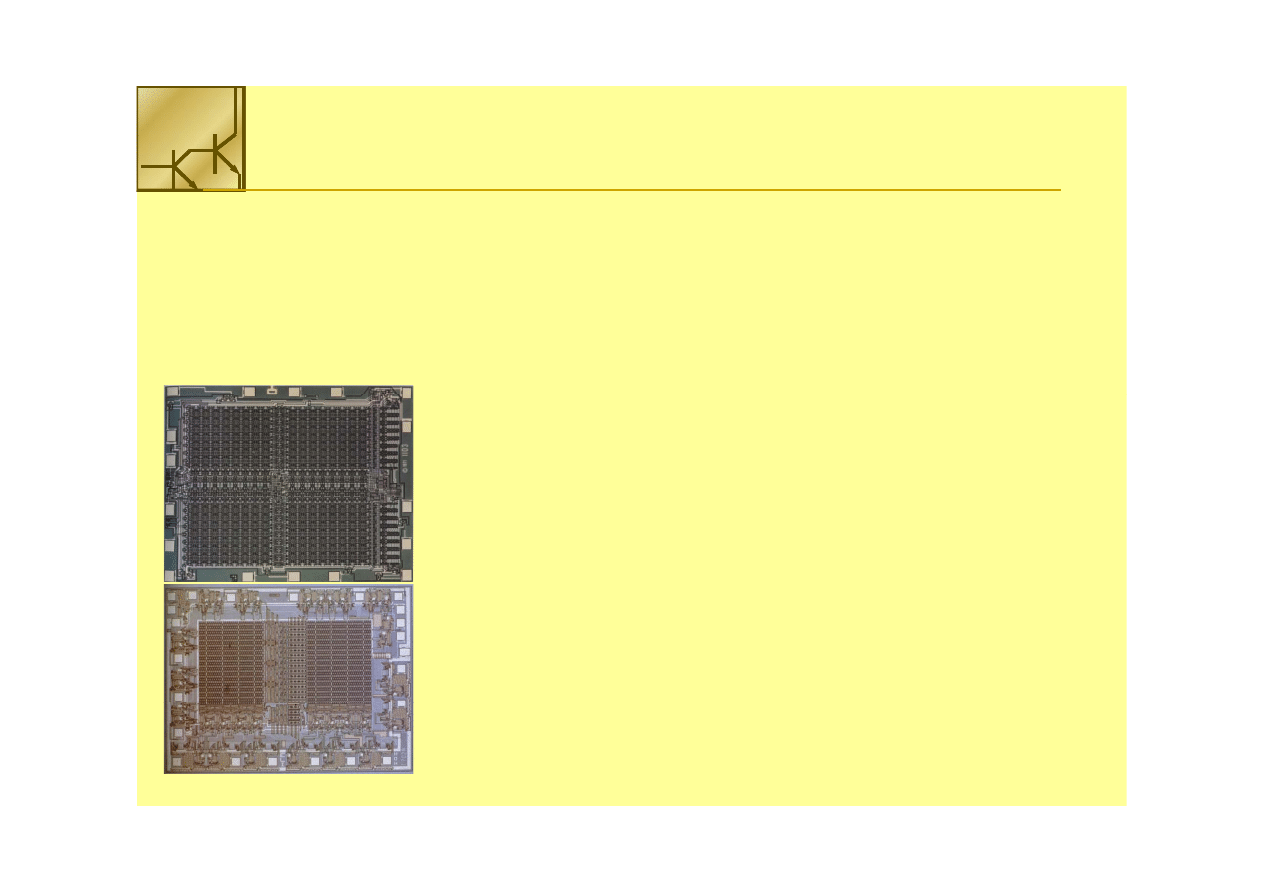

1K bit RAM

1K bit RAM

1K bit RAM

1K bit RAM

1968

1968

1968

1968

Noyce

Noyce and Moore

and Moore leave

leave Fairchild

Fairchild and

and found

found

Intel

Intel

..

No

No business plan, just a promise

business plan, just a promise to specialize in memory chips.

to specialize in memory chips.

Th is $3M in t d s

Th is $3M in t d s nd m

t S nt Cl

B

nd m

t S nt Cl

B

1968

1968

1968

1968

They raise $3M in two days

They raise $3M in two days and move to Santa Clara. By

and move to Santa Clara. By

1971 Intel had 500 employees;

1971 Intel had 500 employees; by 1983 it had 21,500

by 1983 it had 21,500

employees and $1100M in sales.

employees and $1100M in sales.

1970

1970

1970

1970

Intel

Intel

starts selling a 1K bit RAM the 1103

970

970

970

970

starts selling a 1K bit RAM, the 1103.

1971

1971

1971

1971

Intel

Intel

starts selling a first EPROM the 1702

6 marca 2011

Wojciech Kucewicz

13

97

97

97

97

starts selling a first EPROM, the 1702.

Microprocessor Intel 4004 (1971)

Microprocessor Intel 4004 (1971)

Microprocessor Intel 4004 (1971)

Microprocessor Intel 4004 (1971)

2300 t

i t

2300 t

i t

hi

hi

2300 transistors

2300 transistors on one chip

on one chip

Freq.

Freq. --108 kHz

108 kHz

Technology

Technology ––

10

10μμ

It was 1/8" by 1/16"

It was 1/8" by 1/16" and

and it was

it was

as powerful as

as powerful as ENIAC

ENIAC

pperform

erforming

ing about 60 000

about 60 000

pperform

erforming

ing about 60,000

about 60,000

calculations in a second.

calculations in a second.

f l E

f l E

6 marca 2011

Wojciech Kucewicz

14

It was as powerful as ENIAC but was

It was as powerful as ENIAC but was

eclipsed by its more capable brothers

eclipsed by its more capable brothers

Ted Hoff’s invention

Ted Hoff’s invention

Microprocessor Intel

Microprocessor Intel 8800

0088

Microprocessor Intel

Microprocessor Intel 8800

0088

1972

1972

1972

1972

Intel

Intel -- The microprocessor 8008

It had 3,500 transistors supporting a byte-wide data path.

D spit its limit ti ns th 8008 s th fi st

Despite its limitations, the 8008 was the first

microprocessor capable of playing the role of computer CPU

1974

1974

1974

1974

Intel

Intel -- The microprocessor 8008

the 8080 had 6,000 transistors fabricateded in a

6µm process. The clock rate was 2MHz, more than

µ p

,

enough to ignite the personal computer industry. At

least Paul Allen and his partner thought so when

they wrote a BASIC interpreter for the 8080 in

1975

1975.

6 marca 2011

Wojciech Kucewicz

15

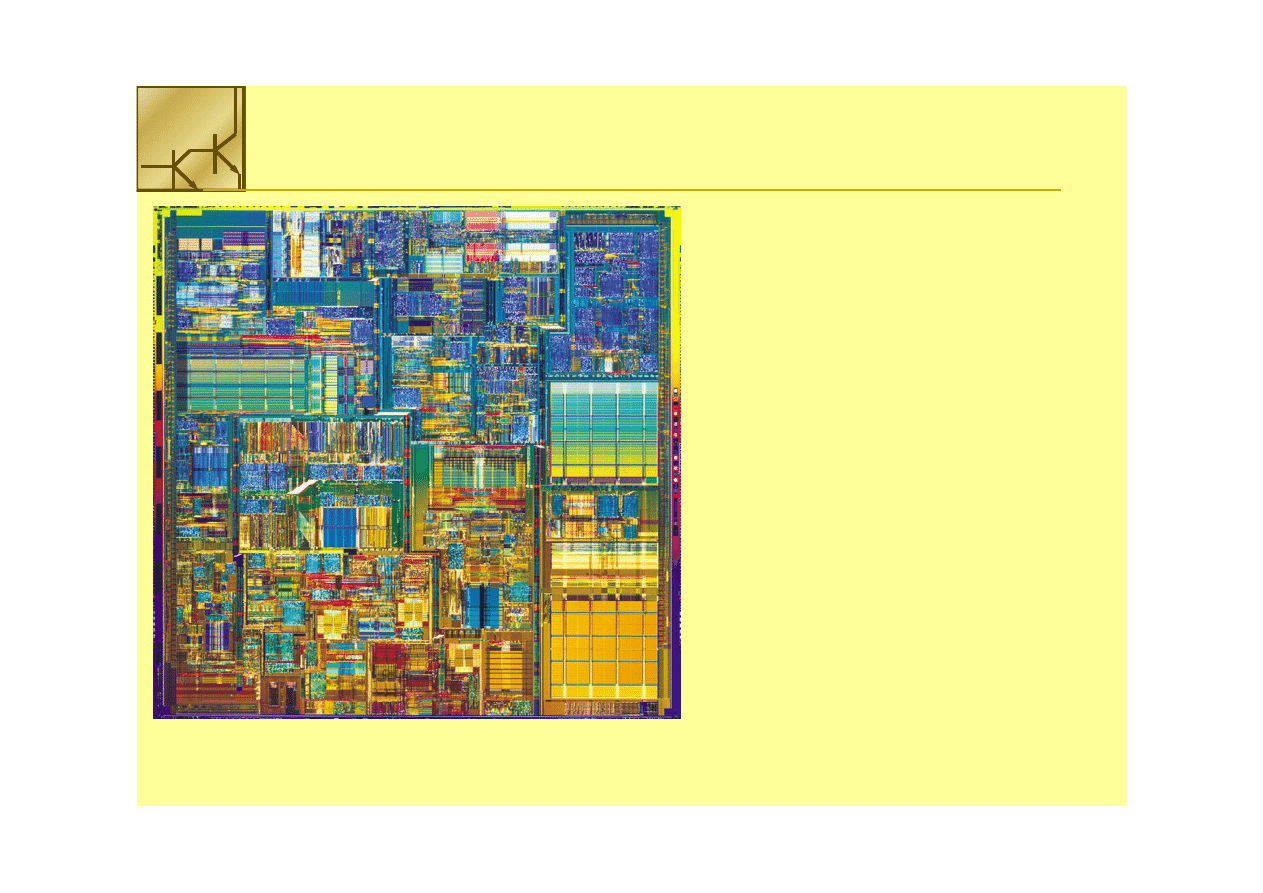

Mi

Mikkroprocesor Intel Pentium

roprocesor Intel Pentium 44 ((200

20011))

Mi

Mikkroprocesor Intel Pentium

roprocesor Intel Pentium 44 ((200

20011))

42 mln

42 mln tranzystorów

tranzystorów

42 mln

42 mln tranzystorów

tranzystorów

(40 tranzystorów zmieściłoby się

na przekroju włosa)

Częstotliwość

Częstotliwość --1,5 GHz

1,5 GHz

Technologia

Technologia––

0,18

0,18μμm

m

10

10

99

operacji na sekundę

operacji na sekundę

6 marca 2011

Wojciech Kucewicz

16

P

d k ji

P

d k ji

P

d k ji

P

d k ji

Progres w produkcji

Progres w produkcji

k

ó l

h

k

ó l

h

Progres w produkcji

Progres w produkcji

k

ó l

h

k

ó l

h

układów scalonych

układów scalonych

układów scalonych

układów scalonych

6 marca 2011

Wojciech Kucewicz

17

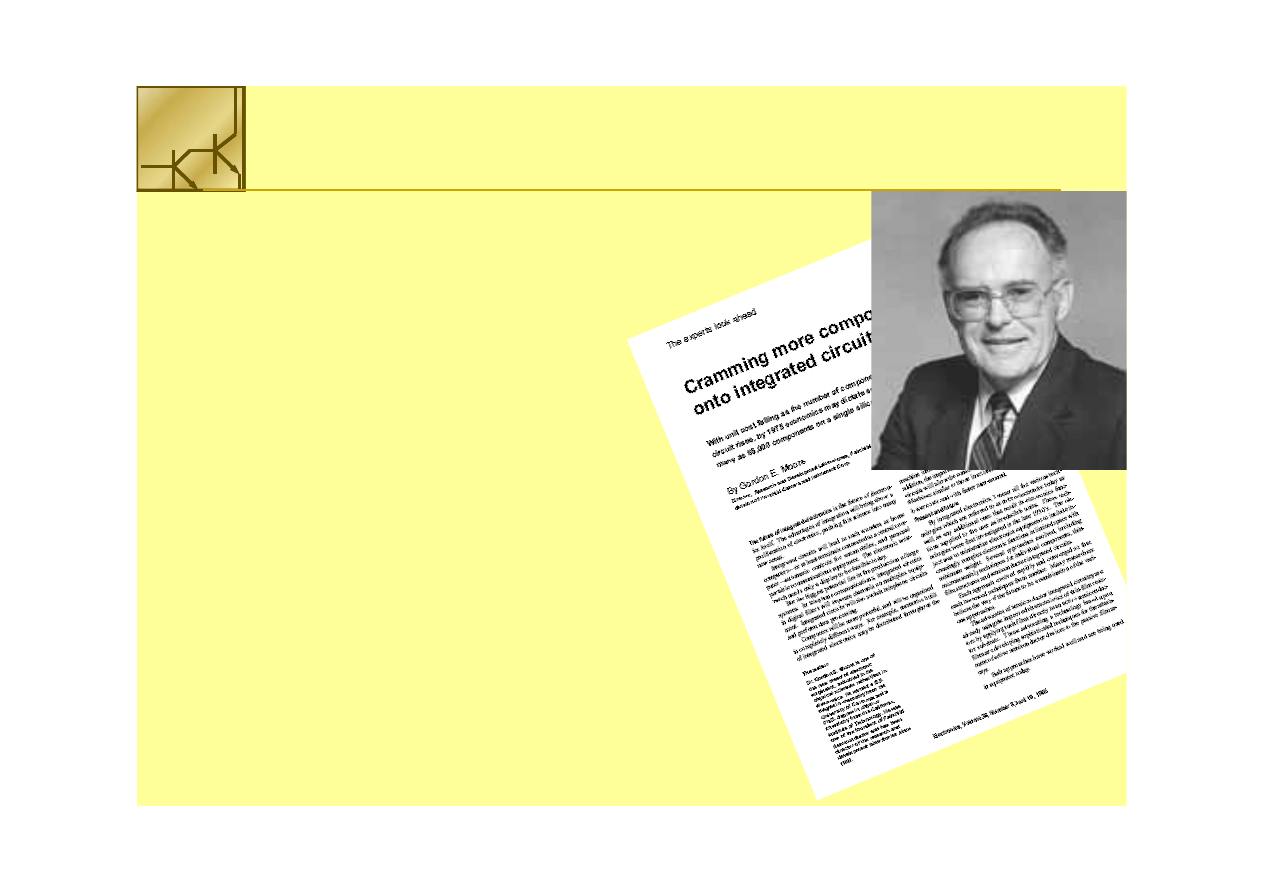

Prawo Moore’a

Prawo Moore’a

Prawo Moore’a

Prawo Moore’a

W roku 1965 Gordoon Moore

W roku 1965 Gordoon Moore

(założyciel firm Fairchild i Intel)

(założyciel firm Fairchild i Intel)

id i ł ż li b t

t ó

id i ł ż li b t

t ó

przewidział, że liczba tranzystorów

przewidział, że liczba tranzystorów

w układzie scalonym będzie

w układzie scalonym będzie

zwiększała się eksponencjalnie w

zwiększała się eksponencjalnie w

funkcji czasu

funkcji czasu..

W latach 80

W latach 80--tych przekroczono barierę

tych przekroczono barierę

1 miliona tranzystorów upakowanych w

1 miliona tranzystorów upakowanych w

y

p

y

y

p

y

jednej strukturze

jednej strukturze

•• 2300 transistors (Intel 4004)

2300 transistors (Intel 4004) –

– 1971

1971

6 marca 2011

Wojciech Kucewicz

18

•• 42 Million (Intel P4)

42 Million (Intel P4) -- 2001

2001

Postęp w produkcji układów scalonych

Postęp w produkcji układów scalonych

Postęp w produkcji układów scalonych

Postęp w produkcji układów scalonych

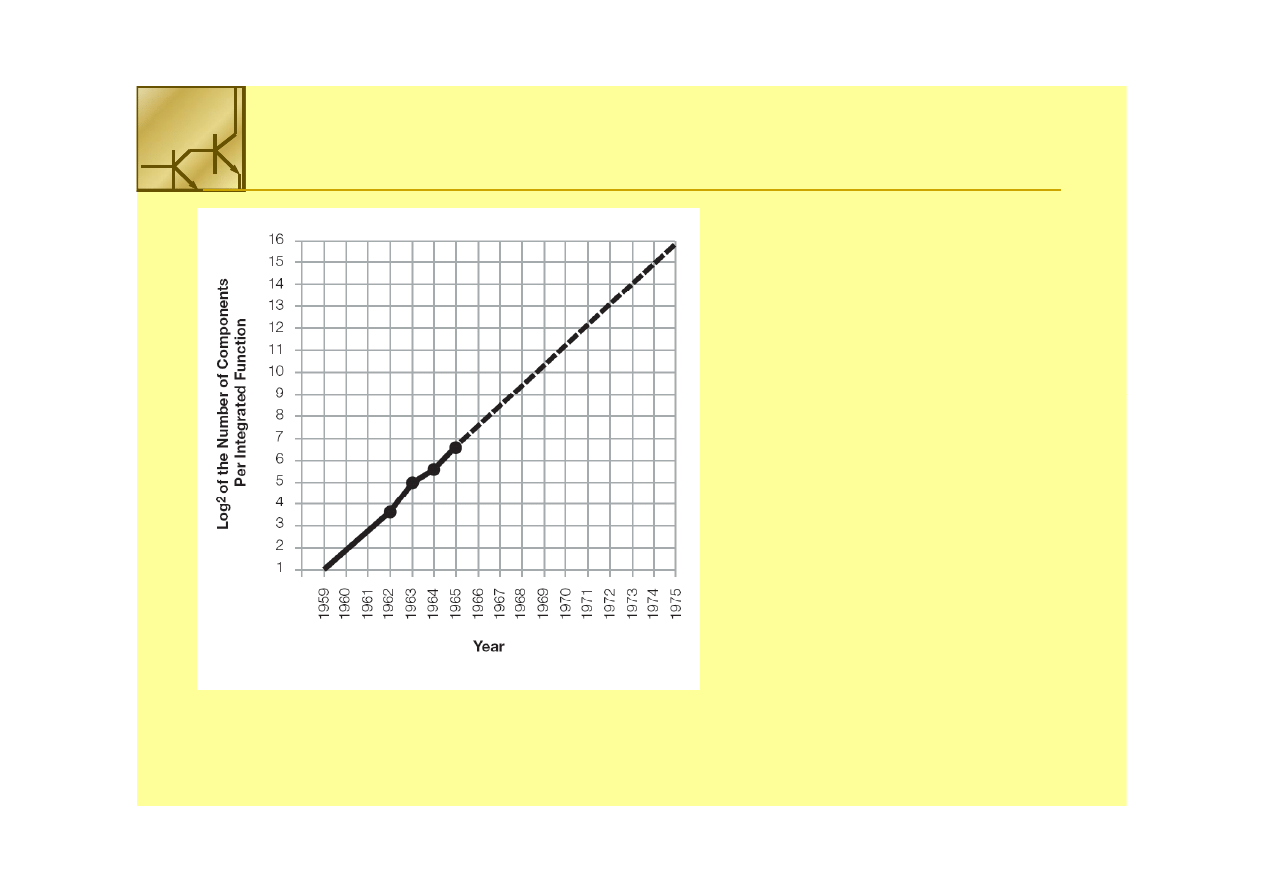

G.Moore - Cramming more

G.Moore Cramming more

components onto integrated

circuits - Electronics, Volume 38,

Number 8, April 19, 1965

ść

ó

ść

ó

ść

ó

ść

ó

6 marca 2011

Wojciech Kucewicz

19

Ilość tranzystorów w układzie scalonym podwaja się

Ilość tranzystorów w układzie scalonym podwaja się

w

w ciagu

ciagu roku

roku

Ilość tranzystorów w układzie scalonym podwaja się

Ilość tranzystorów w układzie scalonym podwaja się

w

w ciagu

ciagu roku

roku

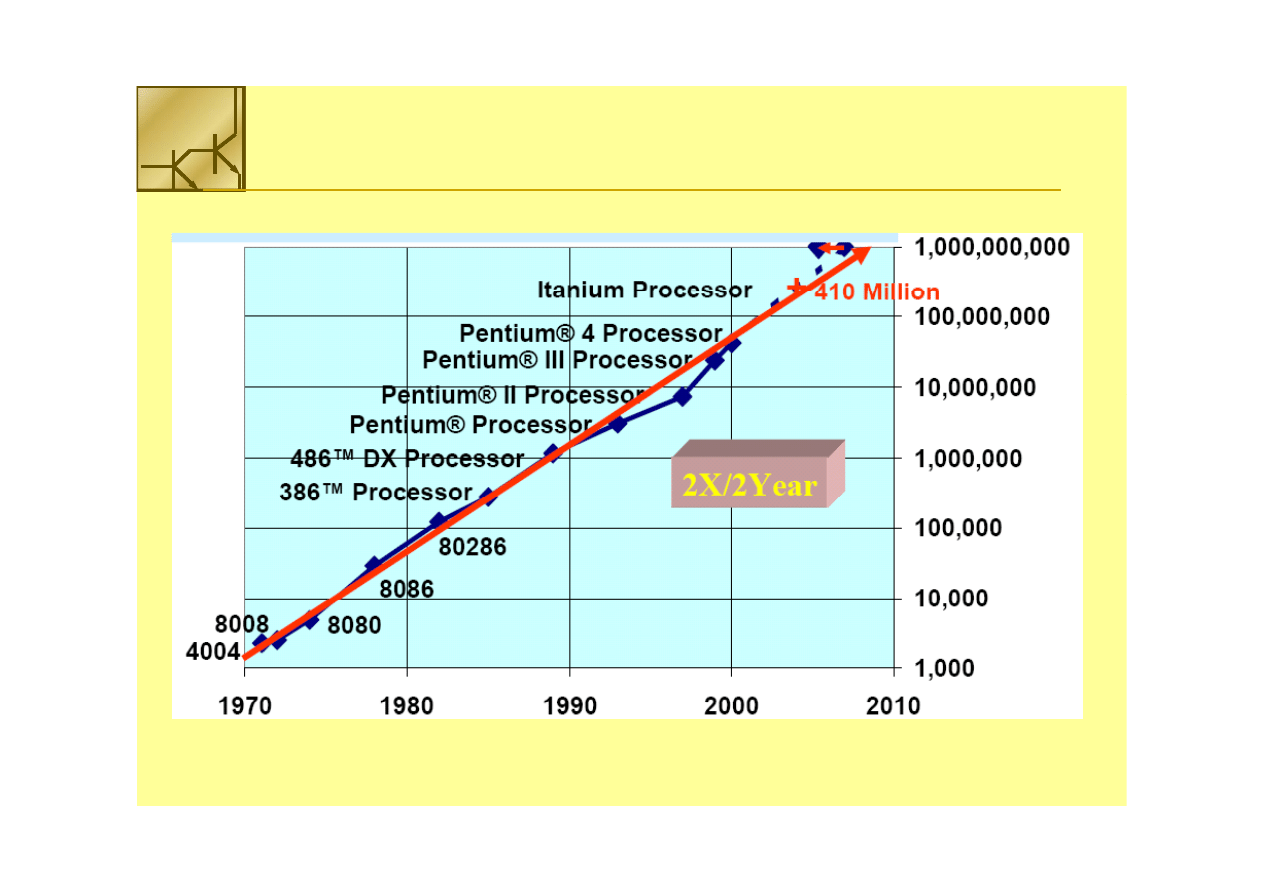

Postęp w produkcji procesorów

Postęp w produkcji procesorów

Postęp w produkcji procesorów

Postęp w produkcji procesorów

P. Gargini – Sailing with the ITRS into nanotechnology - 2004

6 marca 2011

Wojciech Kucewicz

20

Ilość tranzystorów w układzie podwaja się w ciagu 2 lat

Ilość tranzystorów w układzie podwaja się w ciagu 2 lat

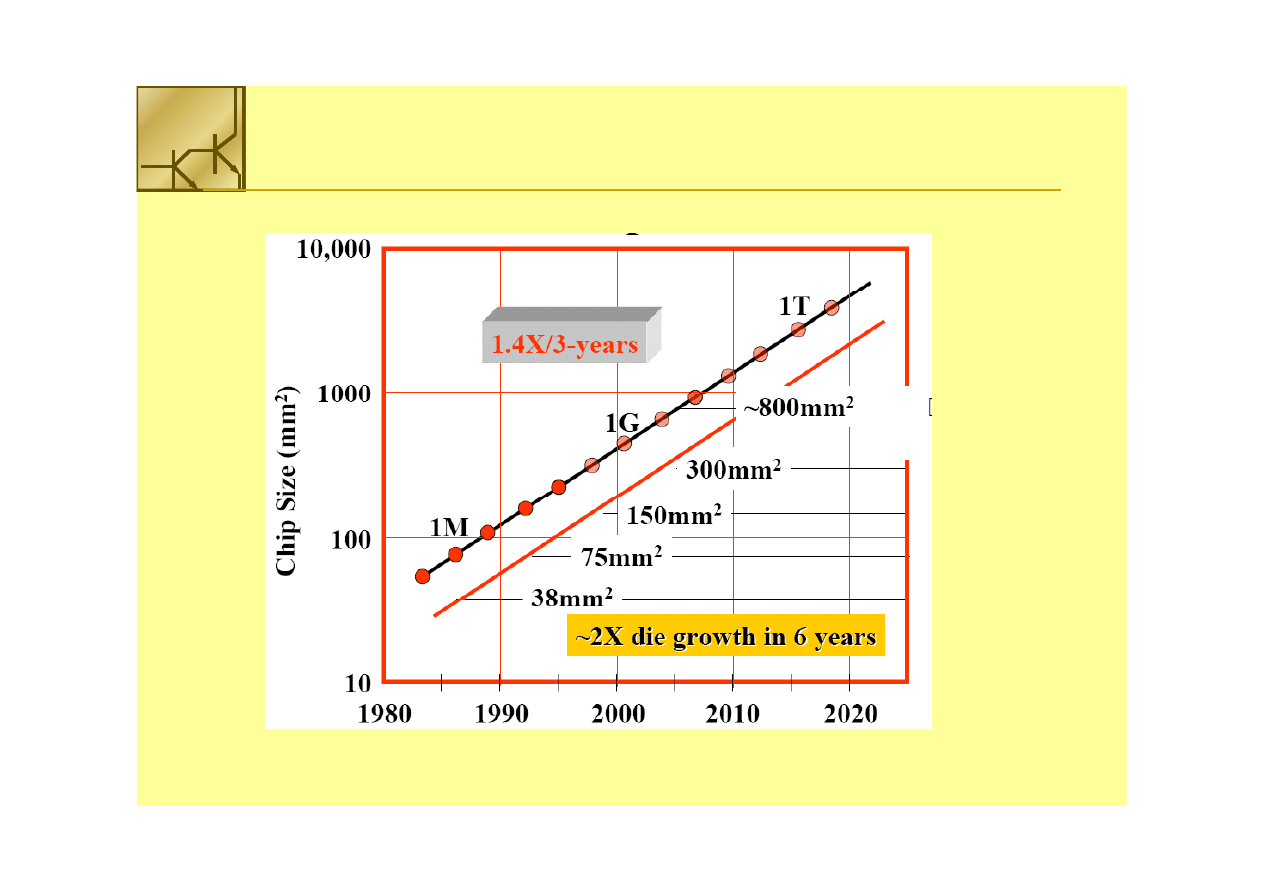

Postęp w produkcji procesorów

Postęp w produkcji procesorów

Postęp w produkcji procesorów

Postęp w produkcji procesorów

P. Gargini – Sailing with the ITRS into nanotechnology - 2004

6 marca 2011

Wojciech Kucewicz

21

Powierzchnia układu scalonego podwaja się w ciagu 6 lat

Powierzchnia układu scalonego podwaja się w ciagu 6 lat

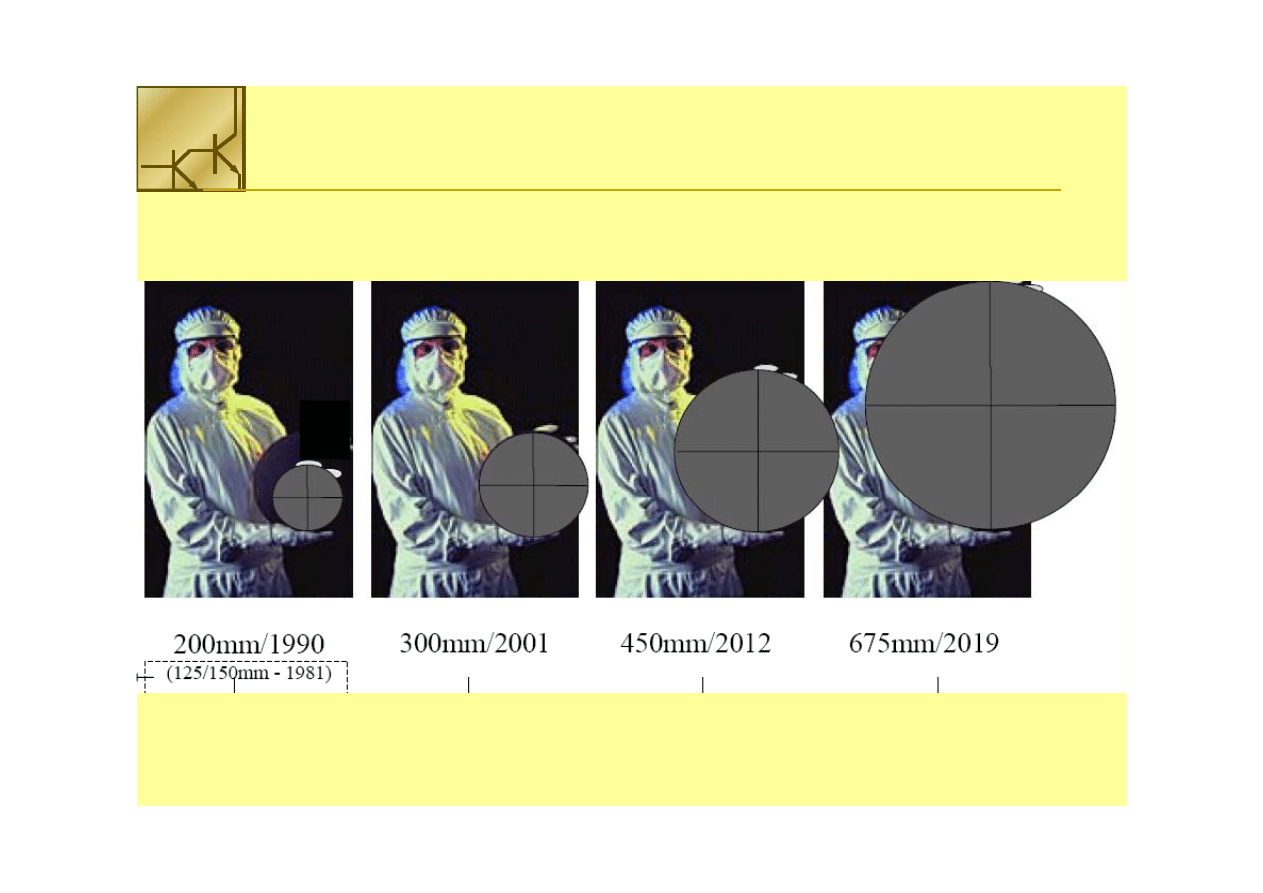

Postęp w produkcji płytek krzemowych

Postęp w produkcji płytek krzemowych

Postęp w produkcji płytek krzemowych

Postęp w produkcji płytek krzemowych

P. Gargini – Sailing with the ITRS into nanotechnology - 2004

6 marca 2011

Wojciech Kucewicz

22

Powierzchnia płytki krzemowej podwaja się w ciagu 8 lat

Powierzchnia płytki krzemowej podwaja się w ciagu 8 lat

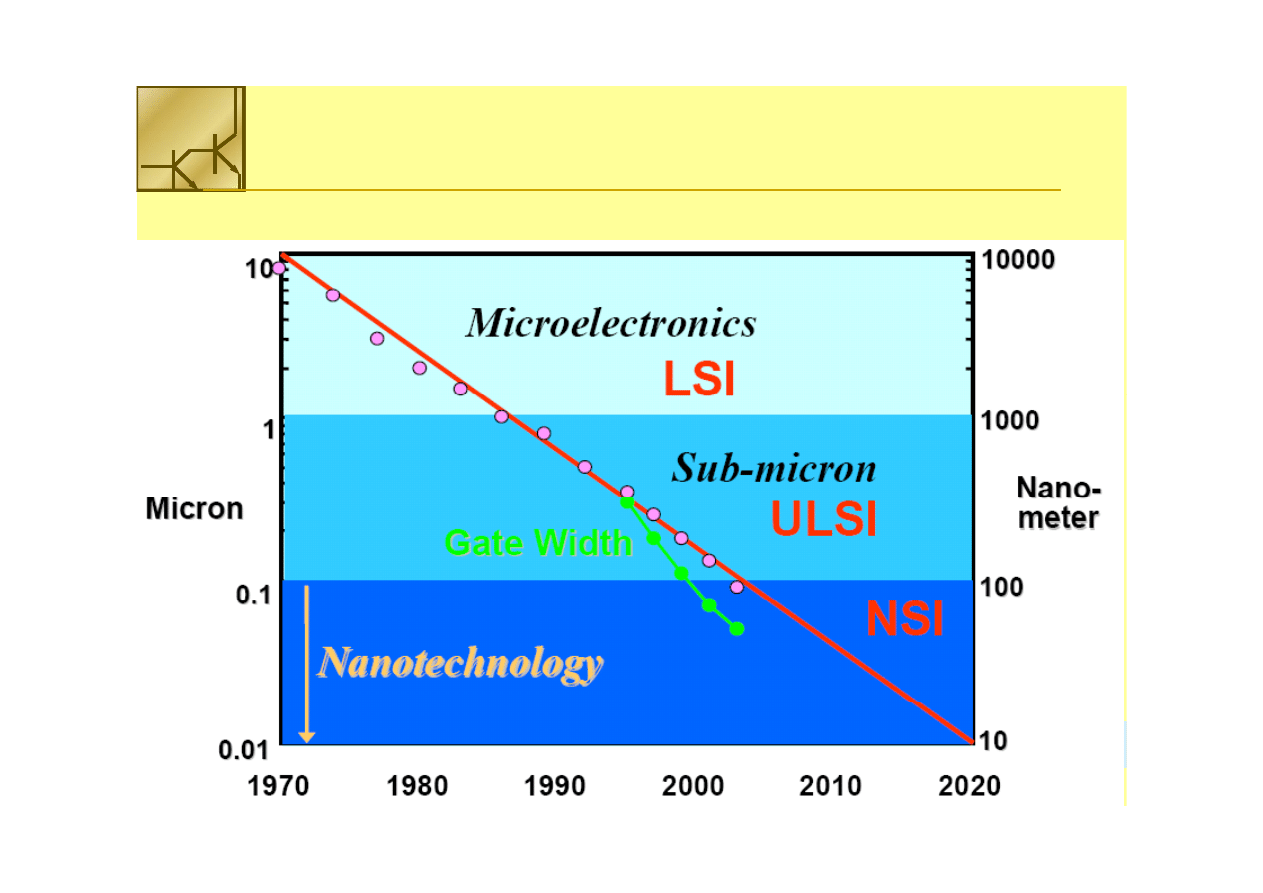

Mikroelektronika

Mikroelektronika Î

Î

Nanotechnologia

Nanotechnologia

Mikroelektronika

Mikroelektronika Î

Î

Nanotechnologia

Nanotechnologia

P. Gargini – Sailing with the ITRS into nanotechnology - 2004

6 marca 2011

Wojciech Kucewicz

23

Powierzchnia płytki krzemowej podwaja się w ciagu 8 lat

Powierzchnia płytki krzemowej podwaja się w ciagu 8 lat

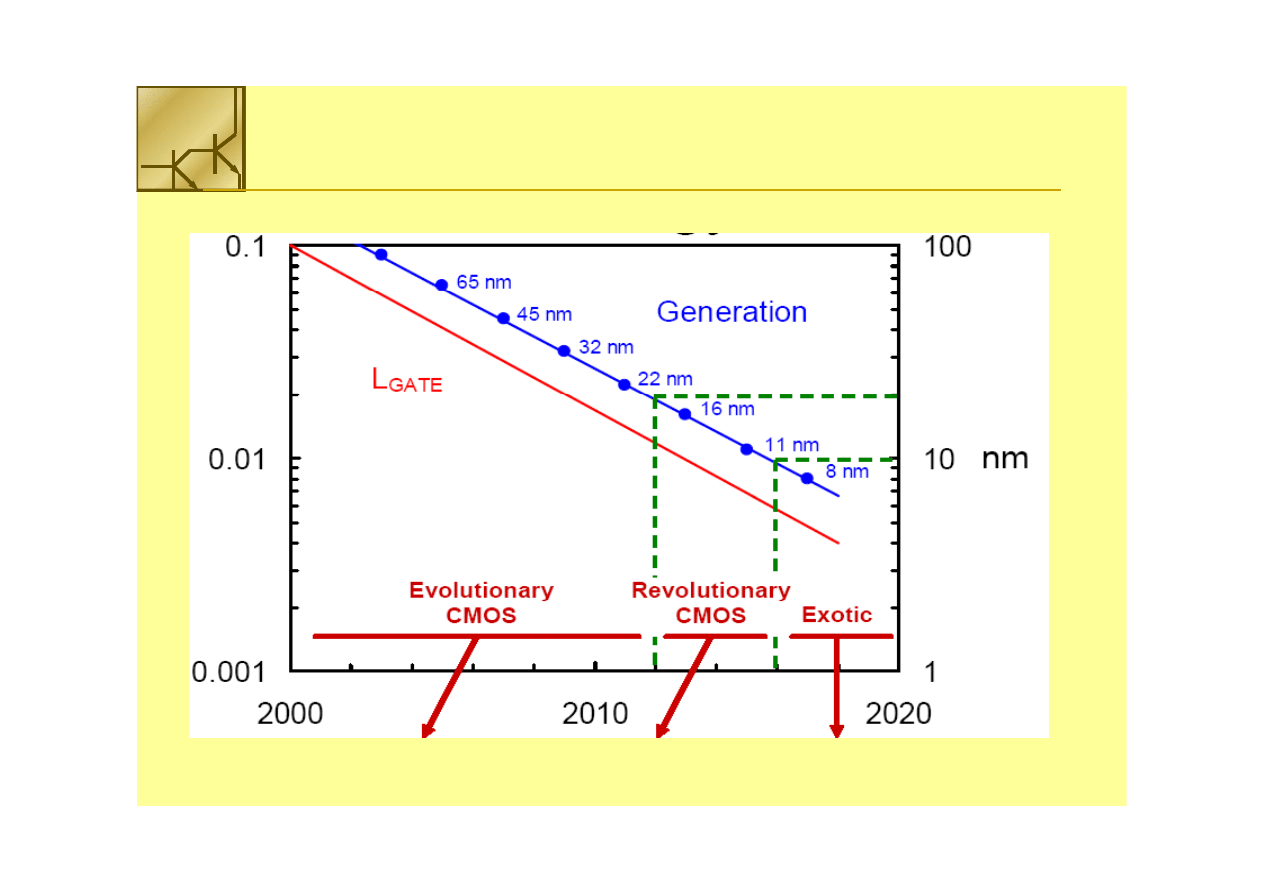

Nanotechnologia

Nanotechnologia

Nanotechnologia

Nanotechnologia

P. Gargini – Sailing with the ITRS into nanotechnology - 2004

6 marca 2011

Wojciech Kucewicz

24

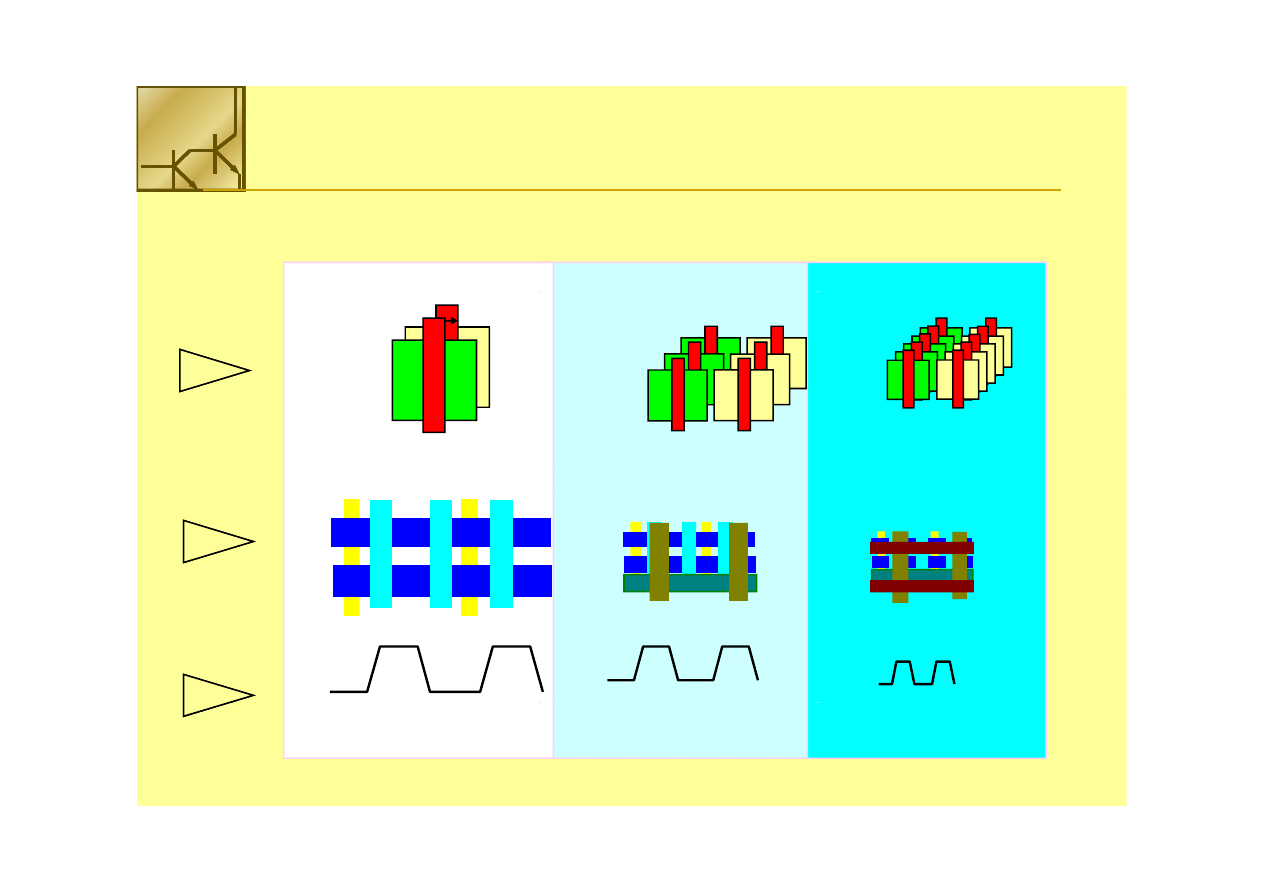

Reasonably familiar Nanotube Different technology

Reasonably familiar Nanotube Different technology

Technology influence

Technology influence

Technology influence

Technology influence

0 18 µm

0.5 µm

0 12µm

0.18 µm

0.5 µm

l

1993

0.12µm

Devices

1999

2002

1993

3 layers

7 layers

8 l

s

Interconnects

7 layers

8 layers

Frequency

6 marca 2011

Wojciech Kucewicz

25

120MHz

500MHz

1200 MHz

Moore’s Law Predictions

Moore’s Law Predictions –– 2025?

2025?

Moore’s Law Predictions

Moore’s Law Predictions –– 2025?

2025?

Assumptions in 1995 based on 1960

Assumptions in 1995 based on 1960--1995

1995

Transistors per chip doubles every 1.5 years

Transistors per chip doubles every 1.5 years

Minimum feature size is cut in half every six years

Minimum feature size is cut in half every six years

Minimum feature size is cut in half every six years

Minimum feature size is cut in half every six years

Chip area goes up 2.3 times every six years

Chip area goes up 2.3 times every six years

Manufacturing costs remain about constant

Manufacturing costs remain about constant

This leads us to the following predictions

Wafer size will be

32 inches!

32 inches!

A wafer fabrication will cost a tens of G$

The chips will be

3 by 6 inches

3 by 6 inches

The minimum feature size will be

100 Angstroms

100 Angstroms

(which is

The minimum feature size will be

100 Angstroms

100 Angstroms

(which is

about 5 photoresist molecules wide)

A Memory chip will hold

64 TERA bits

64 TERA bits

6 marca 2011

Wojciech Kucewicz

26

will they come true?!

will they come true?!

Wyszukiwarka

Podobne podstrony:

Historia elektroniki

Historia elektryczności i magnetyzmu w zarysie

Historia elektroniki

1996 05 Historia elektroniki, część 5

historia elektr

Historia elektrownii wiatrowych

HISTORIA ELEKTRYKI I ELEKTROENERGETYKI NA TERENIE DZIAŁALNOŚCI BĘDZIŃSKIEGO ZE

więcej podobnych podstron