Radioelektronik Audio-HiFi-Video 12/2001

W artykule wyjaniono,

jak powstaje to zjawisko

i podano sposoby

zapobiegania.

Z

jawisko zatrzaskiwania siê struktur

pó³przewodnikowych uk³adów

CMOS (CMOS latch-up) nie jest

problemem w wiêkszoci projekto-

wanych urz¹dzeñ, ale in¿ynier projektuj¹cy

takie uk³ady powinien byæ wiadomy istnie-

nia potencjalnej mo¿liwoci pojawienia siê

takiego zjawiska oraz powinien wiedzieæ,

co jest jego przyczyn¹, a tak¿e, w jaki spo-

sób mo¿na temu niekorzystnemu zjawisku

zapobiegaæ.

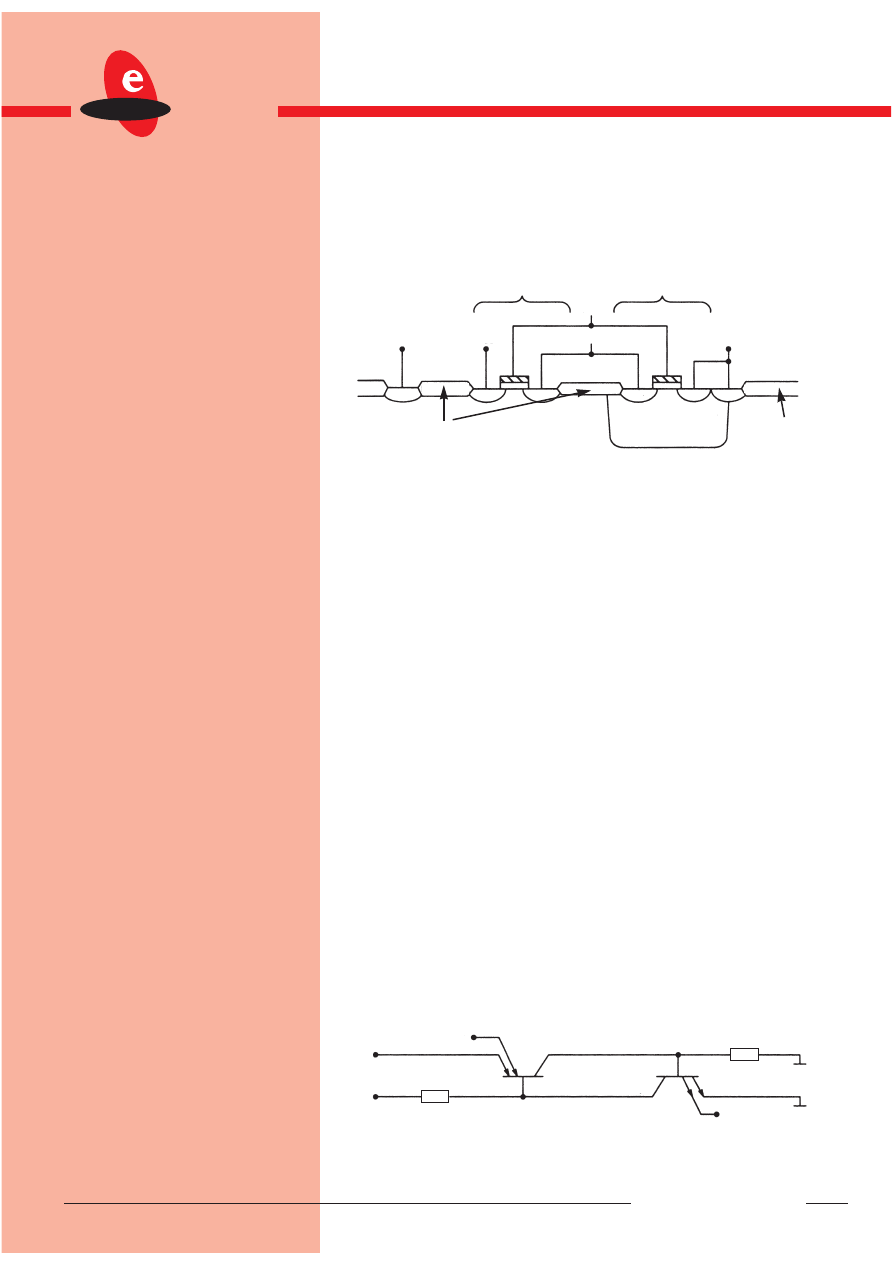

Na rys. 1 przedstawiono przekrój struktury

pó³przewodnikowej uk³adu typowego inwer-

tera wykonanego technologi¹ CMOS. Z fi-

zyczn¹ realizacj¹ takiej struktury pó³przewo-

dnikowej wi¹¿e siê nieuchronnie pojawienie

siê tzw. paso¿ytniczych tranzystorów bipolar-

nych (parasitic bipolar devices). Obwód utwo-

rzony przez takie paso¿ytnicze tranzystory

jest równowa¿ny schematowi zastêpczemu

typowego triaka, czyli przyrz¹du pó³przewo-

dnikowego, który po doprowarzeniu impulsu

pr¹dowego do jego bramki zaczyna w spo-

sób ci¹g³y przewodziæ pr¹d. Przerwanie prze-

p³ywu takiego pr¹du mo¿e zostaæ wywo³ane

jedynie przez ca³kowite wy³¹czenie danego

urz¹dzenia, tzn. przez zanik napiêcia zasila-

j¹cego doprowadzanego do jego wyprowa-

dzenia. Schemat obwodu elektrycznego

utworzonego przez tranzystory paso¿ytni-

cze przedstawiono na rys. 2.

Mechanizm powstawania

zjawiska

W sytuacji pojawienia siê zjawiska zatrza-

niêcia siê struktury CMOS, oba tranzysto-

ry T1 i T2 pozostaj¹ w stanie przewodzenia,

przy czym ka¿dy z nich dostarcza do swe-

go partnera pr¹d bazy o wartoci umo¿liwia-

j¹cej jego pozostanie w stanie przewodze-

nia przez dowolnie d³ugi okres czasu. Zatem

struktura CMOS znajduje siê w stanie za-

trzaniêcia i ze stanu tego mo¿e zostaæ wy-

prowadzona dopiero wskutek od³¹czenia

napiêcia zasilaj¹cego. W przeciwieñstwie do

konwencjonalnych struktur triaków, gdzie

w³¹czenie urz¹dzenia nastêpuje w wyniku

doprowadzenia odpowiednio wysokiego na-

piêcia do wyprowadzenia bazy tranzystora

n-p-n, powsta³a w uk³adzie CMOS struktu-

ra paso¿ytnicza zostaje w³¹czona wskutek

pojawienia siê odpowiedniego poziomu na-

piêcia na wyprowadzeniu emitera dowol-

nego z tranzystorów. Nale¿y zauwa¿yæ po-

nadto, ¿e emitery obu tranzystorów paso¿yt-

niczych s¹ po³¹czone z tym samym punk-

tem, to jest z wyjciem inwertera zaimple-

mentowanego w strukturze CMOS. Aby

struktura CMOS mog³a ulec zatrzaniêciu,

napiêcie wyjciowe musi byæ wiêksze ni¿

U

DD

+ 0,5 V lub mniejsze ni¿ _0,5 V oraz

przep³ywaj¹cy pr¹d musi mieæ równie¿ pew-

n¹ minimaln¹ wartoæ progow¹.

W wietle powy¿szej analizy wszystkie uk³a-

dy CMOS s¹ w pewnym stopniu wra¿liwe na

pojawienie siê zjawiska zatrzaskiwania oraz

w³aciwoæ ta jest nieunikniona ze wzglêdu na

istnienie paso¿ytniczej struktury p-n-p-n, która

jest immanentn¹ czêci¹ ka¿dego uk³adu

CMOS. Zjawisko zatrzaskiwania siê struktur

CMOS powstaje w sytuacji, gdy poziom na-

piêcia wejciowego przekroczy poziom na-

piêcia zasilania uk³adu i powstanie w ten

sposób obszar o niskiej impedancji ³¹cz¹cy

wyprowadzenia U

DD

i U

SS

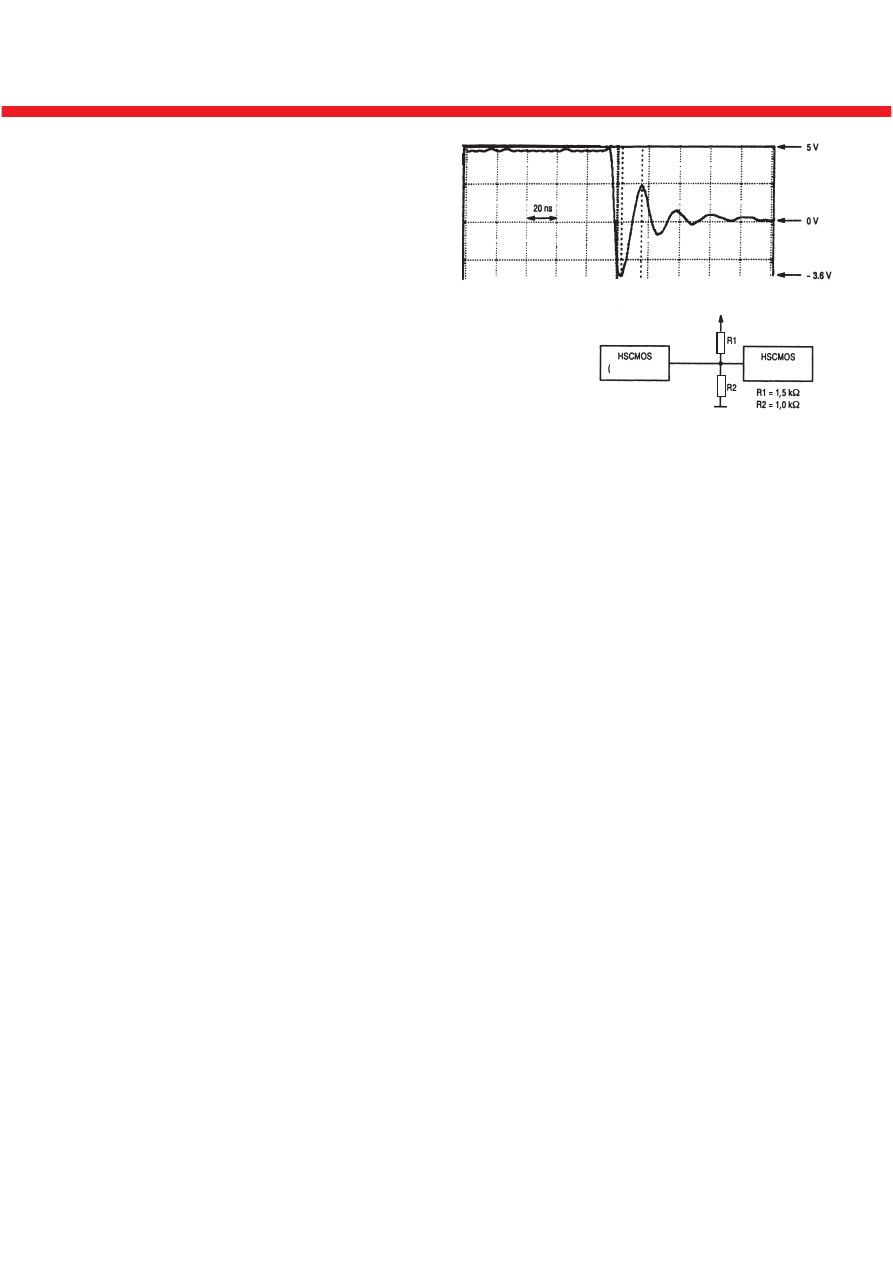

. Na rys. 3 za-

mieszczono ilustracjê przypadku, w którym

podczas wy³¹czenia sygna³u doprowadzane-

go do wejæ uk³adu CMOS, wskutek zbyt

du¿ej indukcyjnoci linii doprowadzaj¹cej

sygna³, powstaje impuls napiêciowy o ujem-

nej wartoci napiêcia. Je¿eli w wyniku poja-

wienia siê takiego impulsu napiêciowego,

napiêcie na wejciu uk³adu CMOS spadnie

poni¿ej wartoci progowej, wówczas doj-

dzie nieuchronnie do zjawiska zatrzaniêcia

siê struktury pó³przewodnikowej.

rodki zaradcze

W przypadku wyst¹pienia zjawiska zatrza-

niêcia siê struktury CMOS, je¿eli przep³y-

waj¹cy w jego wyniku pr¹d nie zostanie

w jaki sposób ograniczony, urz¹dzenie

CMOS zostanie w sposób nieodwracalny

zniszczone. Z tego powodu projektant urz¹-

dzeñ wykorzystuj¹cych uk³ady CMOS powi-

nien zjawisku temu zapobiegaæ.

Sposoby przeciwdzia³ania zatrzaskiwaniu

siê uk³adów CMOS s¹ nastêpuj¹ce:

1. Nale¿y upewniæ siê, ¿e wartoci napiêæ

wejciowych i wyjciowych s¹ ograniczone

i nie przekraczaj¹ dopuszczalnych wartoci

maksymalnych:

q

napiêcie wejciowe _ 0,3 V<U

we

<U

DD

+ 0,3 V, jako potencja³ odniesienia przyj-

mowane jest wyprowadzenie U

SS

q

napiêcie wyjciowe _0,3 V<U

we

<U

DD

+

ZJAWISKO ZATRZASKIWANIA SIÊ

UK£ADÓW CMOS

Rys. 1. Przekrój poprzez strukturê pó³przewodnikow¹ inwertera CMOS

Pod³o¿e typu n

Kana³ typu p

Kana³ typu n

Wejcie

inwertera

Wyjcie

inwertera

Wyjcie

Wyjcie

kana³u p kana³u n

Wyjcie kana³u p

Wyjcie kana³u n

Rezystancja studni potencja³u p

Rezystancja pod³o¿a typu n

Studnia potencja³u

(typ p)

U

DD

U

SS

U

SS

U

DD

U

DD

U

SS

Izoluj¹ca warstwa tlenku

Izoluj¹ca warstwa tlenku

n+ p+ p+ n+ n+ p+

Rys. 2. Schemat zastêpczy uk³adu paso¿ytniczych tranzystorów bipolarnych w strukturze CMOS

p+

p+

n_

n_

n+ n+

p_

p_

T1

T2

23

0,3 V, jako potencja³ odniesienia przyjmowa-

ne jest wyprowadzenie U

SS

q

pr¹d wejciowy I

we

<10 mA

q

pr¹d wyjciowy I

wy

<10 mA (w sytuacji

pojawienia siê przejciowych impulsów na-

piêciowych przekraczaj¹cych dopuszczalne

wartoci).

2. Je¿eli przewidywane jest pojawienie siê

na wyjciu uk³adu impulsów napiêciowych

o dostatecznie du¿ej energii, aby mog³y

wywo³aæ zjawisko zatrzaniêcia siê struktu-

ry CMOS, nale¿y zastosowaæ zewnêtrzne

diody zabezpieczaj¹ce, które ogranicz¹ do-

puszczalny zakres napiêcia wyjciowego. Al-

ternatywne rozwi¹zanie polega na zastoso-

waniu zewnêtrznego rezystora, który ogra-

niczy wartoæ pr¹du wyjciowego poni¿ej

dopuszczalnej wartoci.

3. Analogiczne rozwi¹zanie nale¿y zastoso-

waæ w przypadku mo¿liwoci pojawienia

siê impulsów napiêciowych na wejciu uk³a-

du CMOS, tzn. nale¿y zastosowaæ albo dio-

dy ograniczaj¹ce zakres napiêcia wejcio-

wego, albo te¿ rezystory ograniczaj¹ce pr¹d

wejciowy poni¿ej wartoci 10 mA. Sposób

przy³¹czenia takich rezystorów do wejcia

uk³adu CMOS przedstawiono na rys. 4.

4. Ponadto linie zasilaj¹ce uk³ady CMOS nie

powinny zawieraæ sygna³u szumu o zbyt

wysokim poziomie (zw³aszcza niebezpiecz-

ne s¹ chwilowe spadki napiêcia, które mo-

¿e w ten sposób przekroczyæ dopuszczalny

zakres).

5. Nale¿y ograniczyæ maksymaln¹ wartoæ

pr¹du zasilaj¹cego uk³ady CMOS, tak aby

w razie pojawienia siê zjawiska zatrzaniê-

cia siê uk³adu nie dosz³o do jego uszko-

dzenia, wskutek wydzielaj¹cej siê zbyt wiel-

kiej iloci energii cieplnej.

Nale¿y równie¿ zapamiêtaæ, ¿e na wyst¹pie-

nie zjawiska zatrzaskiwania siê struktur

CMOS s¹ nara¿one szczególnie urz¹dzenia

elektroniczne pracuj¹ce w warunkach prze-

mys³owych, a zw³aszcza sterowniki silni-

ków elektrycznych (wysoki poziom zak³óceñ

w liniach napiêæ zasilaj¹cych) oraz urz¹-

dzenia, w których sygna³y przesy³ane s¹

poprzez d³ugie linie transmisyjne (du¿a in-

dukcyjnoæ paso¿ytnicza takich linii powo-

duje pojawienie siê stanów nieustalonych

podczas prze³¹czania poziomów napiêæ,

w czasie trwania których napiêcie wejcio-

we mo¿e przekroczyæ dopuszczalny

poziom).

n

Miros³aw Gajer

Artyku³ opracowano na podstawie: LonWorks - Techno-

logy Device Data, materia³y firmy Motorola, DL 159/D,

REV 3, Motorola Inc. 1997

Rys. 3. Przebieg napiêcia na

wejciu inwertera CMOS

podczas stanów nieustalo-

nych, powsta³ych

w wyniku prze³¹czania

poziomów napiêæ i wywo³a-

nych du¿¹ wartoci¹

impedancji linii

doprowadzaj¹cej sygna³

Rys. 4. Sposób przy³¹czenia rezystorów

ograniczaj¹cych do wejcia uk³adu CMOS

(HSCMOS _ High Speed CMOS _ uk³ady CMOS

o du¿ej szybkoci prze³¹czania)

U

CC

Sterownik

Odbiornik

Wyszukiwarka

Podobne podstrony:

Plan rejsu Flis Notecki 12 22 06 2015

2001 12 29

1999 12 22 2757

2001 03 22

2001 09 22

2001 11 22

2001 08 22 1680

12 (22)

2001 11 22 kol 1

2001 12 Red Hat 7 2 on Test in the Linux Labs

2001 12 01

1987 12 22 Zarz MSW Urzędy Spraw Wewid 18547

2001 12 Szkoła konstruktorów klasa II

2001 12 16

2001 12 26

Everyday Practical Electronics 2001 12

12-22, Politologia - WSFiZ, Administracja publiczna - Solarz

2001 12

więcej podobnych podstron