L11: 6.111 Spring 2006

1

Introductory Digital Systems Laboratory

L11: Major/Minor

L11: Major/Minor

FSMs

FSMs

Acknowledgements:

Materials in this lecture are courtesy of the following sources and are used with permission.

Rex Min

L11: 6.111 Spring 2006

2

Introductory Digital Systems Laboratory

Quiz will be

Closed Book

Tuesday, March 21, 2006

,

7:30pm-9:30pm in 32-155 Covers Problem Sets 1-3,

Lectures 1-10 (through Analog), Labs 1-3

Some of the topics to be covered include

Combinational Logic: Boolean Algebra, Karnaugh Maps, MSP, MPS,

dealing with don’t cares

Latches and Edge Triggered Registers/Flip-flops

z

Understand the difference between latches, registers and unclocked

memory elements (e.g., SR-Flip Flop)

z

Different memory types: SR, D, JK, T

z

Understand setup/hold/propagation delay and how they are computed

System Timing (minimum clock period and hold time constraint)

z

Impact of Clock skew on timing

Counters and simple FSMs (understand how the ‘163 and ‘393 work)

FSM design (Mealy/Moore, dealing with glitches)

Combinational and sequential Verilog coding

z

Continuous assignments, blocking vs. non-blocking, etc.

Quiz

Quiz

L11: 6.111 Spring 2006

3

Introductory Digital Systems Laboratory

Quiz (cont.)

Quiz (cont.)

Tri-states basics

Dealing with glitches

z

When are glitches OK?

z

How do you deal with glitches in digital system design? (registered

outputs, appropriate techniques to gate a clock, etc.)

Memory Basics

z

Understand differences between DRAM vs. SRAM vs. EEPROM

z

Understand timing and interfacing to the 6264

Arithmetic

z

Number representation: sign – magnitude, Ones complement, Twos

complement

z

Adder Structures: Ripple carry, Carry Bypass Adder, Carry Lookahead

Adder

z

False Paths and Delay Estimation

z

Shift/add multiplier, Baugh-Wooley Multiplier (Twos complement

multiplication)

Analog Design

z

Basics of ADC and DAC, interfaces

L11: 6.111 Spring 2006

4

Introductory Digital Systems Laboratory

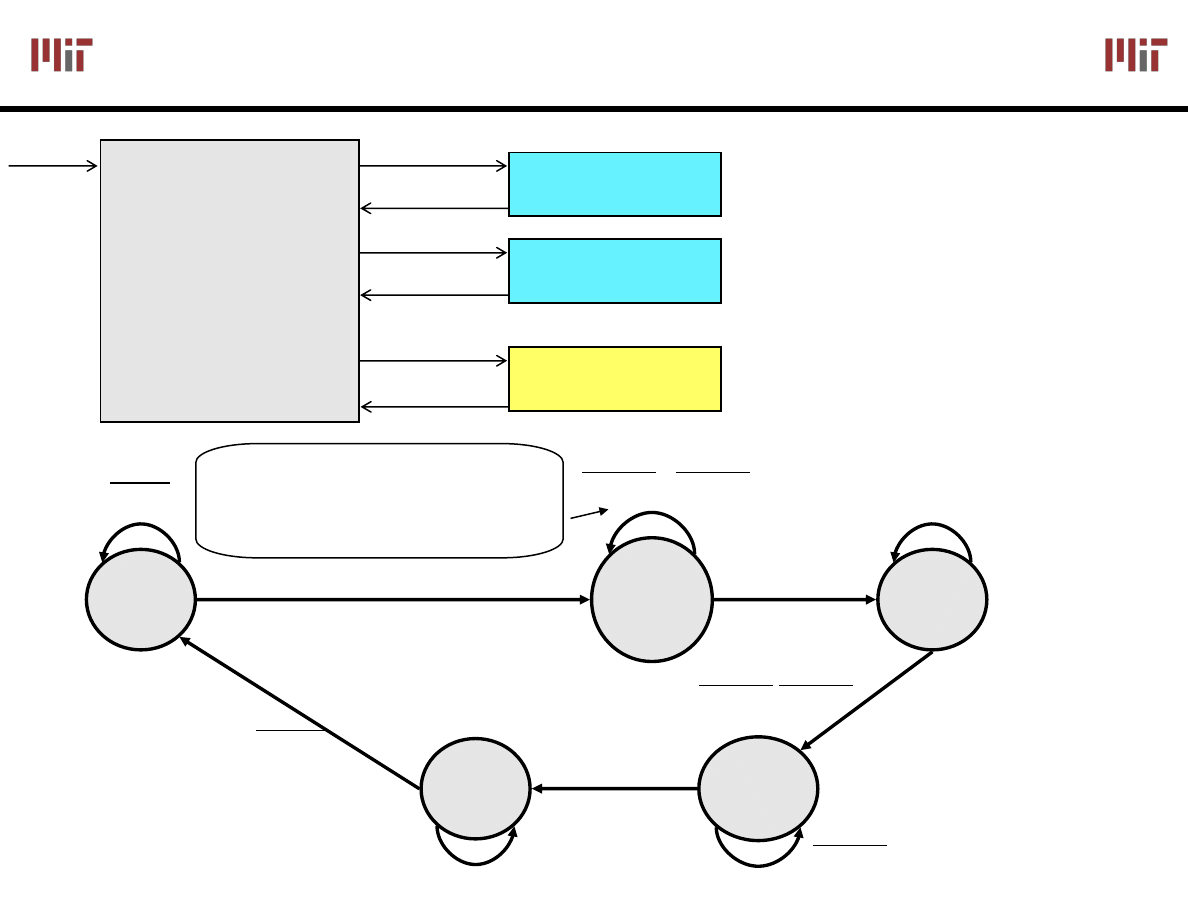

Toward FSM Modularity

Toward FSM Modularity

Consider the following abstract FSM:

S

0

a

1

b

1

c

1

d

1

S

1

S

2

S

3

S

4

S

5

S

6

S

7

S

8

S

9

a

2

b

2

c

2

d

2

a

3

b

3

c

3

d

3

Suppose that each set of states a

x

...d

x

is a “sub-FSM” that

produces exactly the same outputs.

Can we simplify the FSM by removing equivalent states?

No! The outputs may be the same, but the

next-state transitions are not.

This situation closely resembles a

procedure call

or

function call

in software...how can we apply this concept to FSMs?

L11: 6.111 Spring 2006

5

Introductory Digital Systems Laboratory

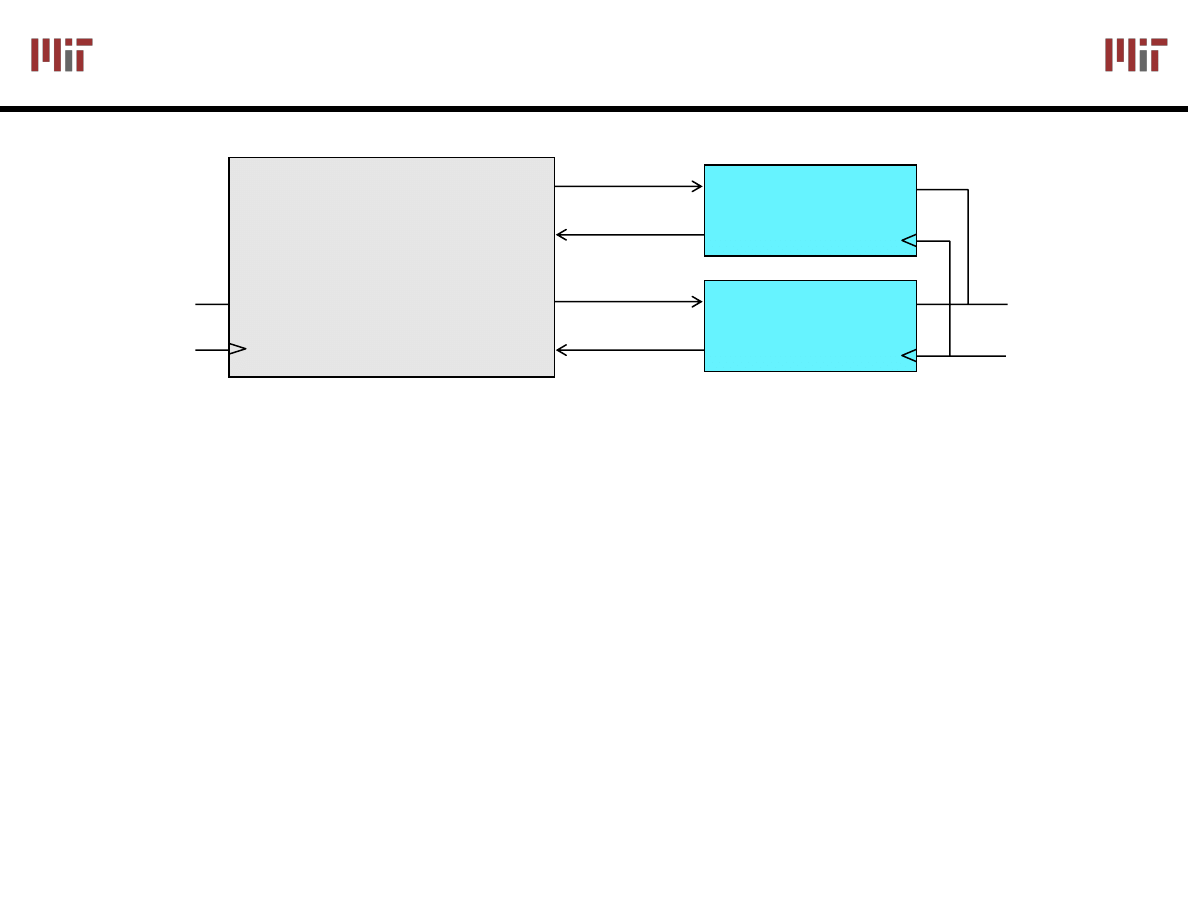

The Major/Minor FSM Abstraction

The Major/Minor FSM Abstraction

Subtasks are encapsulated in

minor FSMs

with common

reset and clock

Simple communication abstraction:

START: tells the minor FSM to begin operation (the call)

BUSY: tells the major FSM whether the minor is done (the return)

The major/minor abstraction is great for...

Modular designs (always a good thing)

Tasks that occur often but in different contexts

Tasks that require a variable/unknown period of time

Event-driven systems

Major FSM

Minor FSM A

Minor FSM B

START

A

BUSY

A

BUSY

B

START

B

CLK

RESET

RESET

CLK

L11: 6.111 Spring 2006

6

Introductory Digital Systems Laboratory

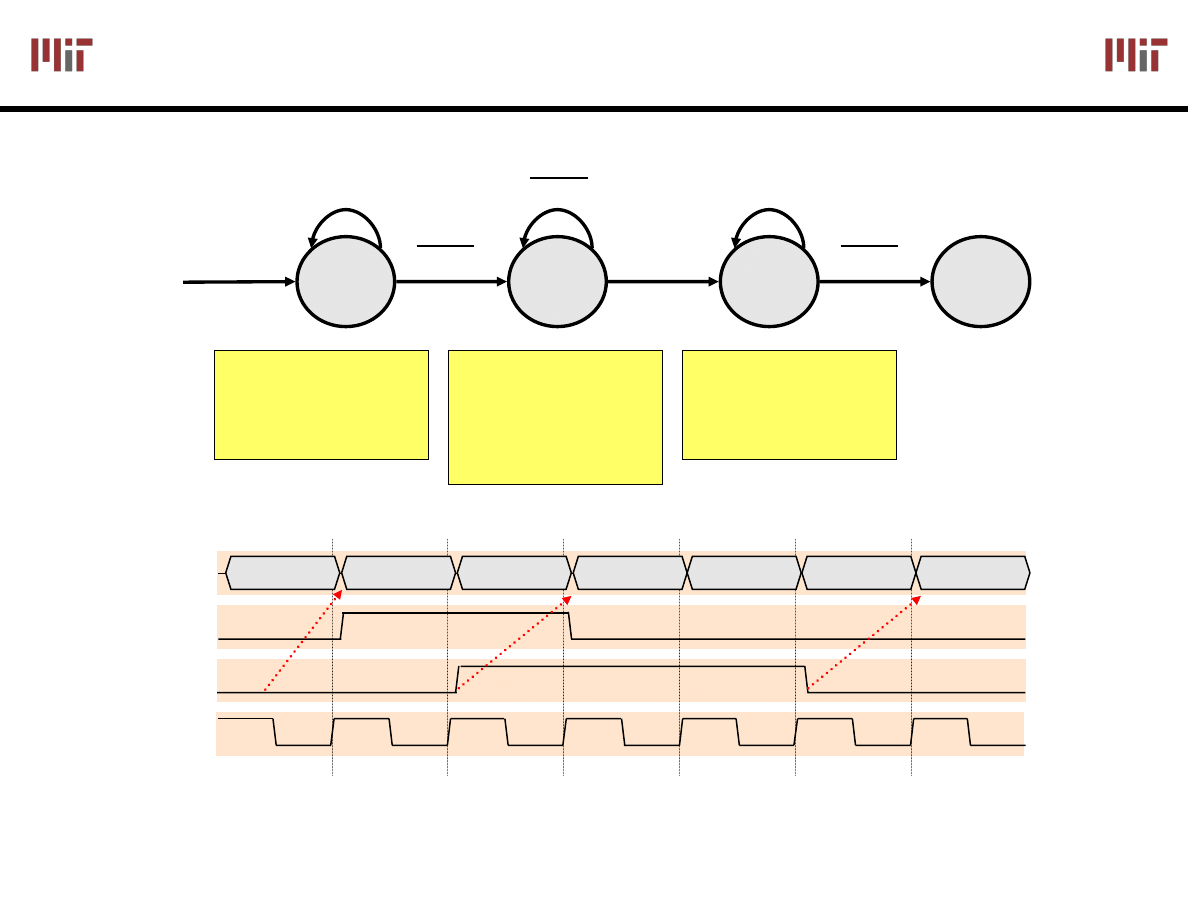

Inside the Major FSM

Inside the Major FSM

S

1

S

2

START

S

3

S

4

...

BUSY

BUSY

BUSY

BUSY

BUSY

BUSY

1. Wait until

the minor FSM

is ready

2. Trigger the

minor FSM

(and make sure

it’s started)

3. Wait until

the minor FSM

is done

START

BUSY

Major FSM

State

S

1

S

2

S

2

S

3

S

3

S

3

S

4

CLK

L11: 6.111 Spring 2006

7

Introductory Digital Systems Laboratory

Inside the Minor FSM

Inside the Minor FSM

T

2

BUSY

T

3

BUSY

T

4

BUSY

1. Wait for a

trigger from the

major FSM

2. Do some useful work

T

1

BUSY

START

START

START

BUSY

Major FSM

State

S

1

S

2

S

2

S

3

S

3

S

3

S

4

CLK

Minor FSM

State

T

1

T

1

T

2

T

3

T

4

T

1

T

1

3. Signal to the

major FSM that

work is done

can we

speed

this up?

L11: 6.111 Spring 2006

8

Introductory Digital Systems Laboratory

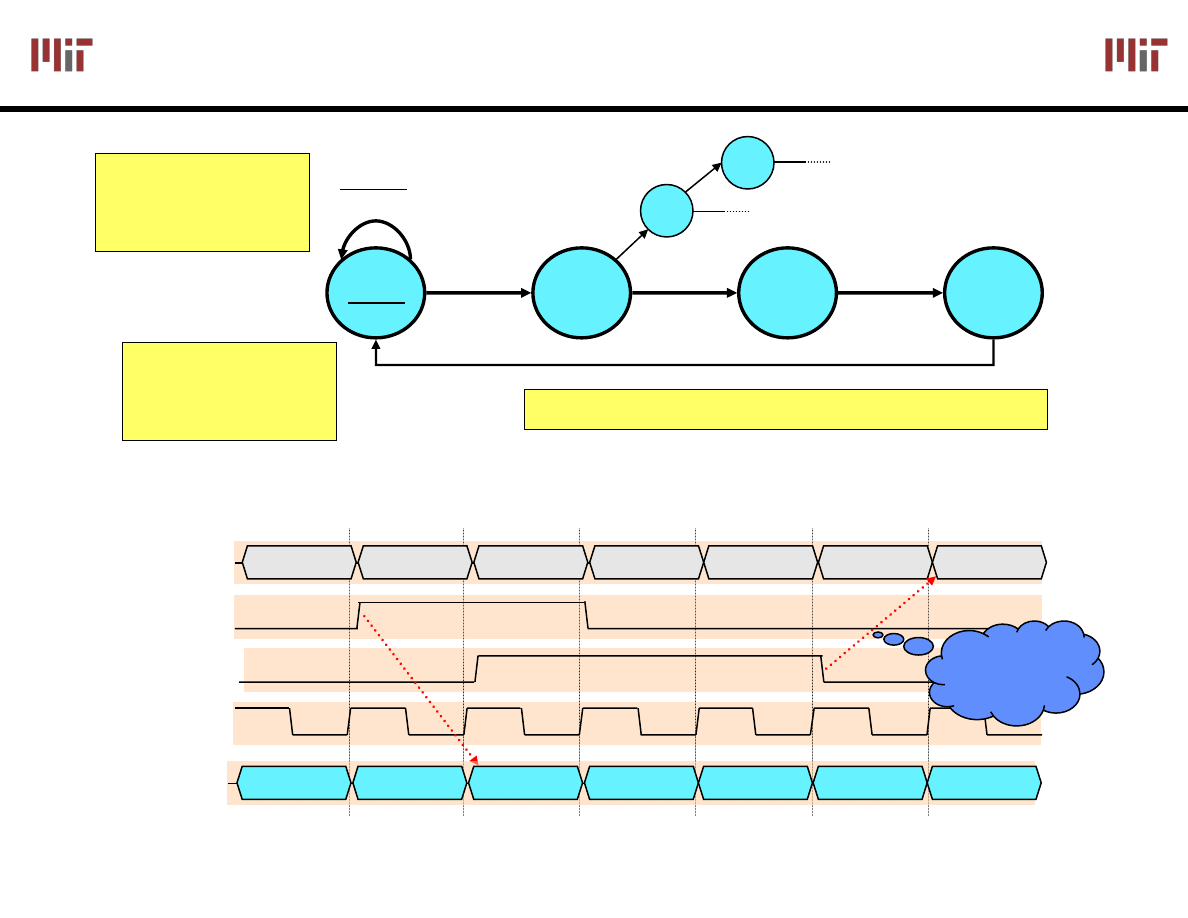

Optimizing the Minor FSM

Optimizing the Minor FSM

T

2

BUSY

T

3

BUSY

T

4

BUSY

T

1

BUSY

START

START

Good idea: de-assert BUSY one cycle early

Bad idea #1:

T

4

may not immediately return to T1

T

2

BUSY

T

3

BUSY

T

1

BUSY

START

START

T

4

BUSY

Bad idea #2:

BUSY never asserts!

T

1

BUSY

START

START

T

2

BUSY

L11: 6.111 Spring 2006

9

Introductory Digital Systems Laboratory

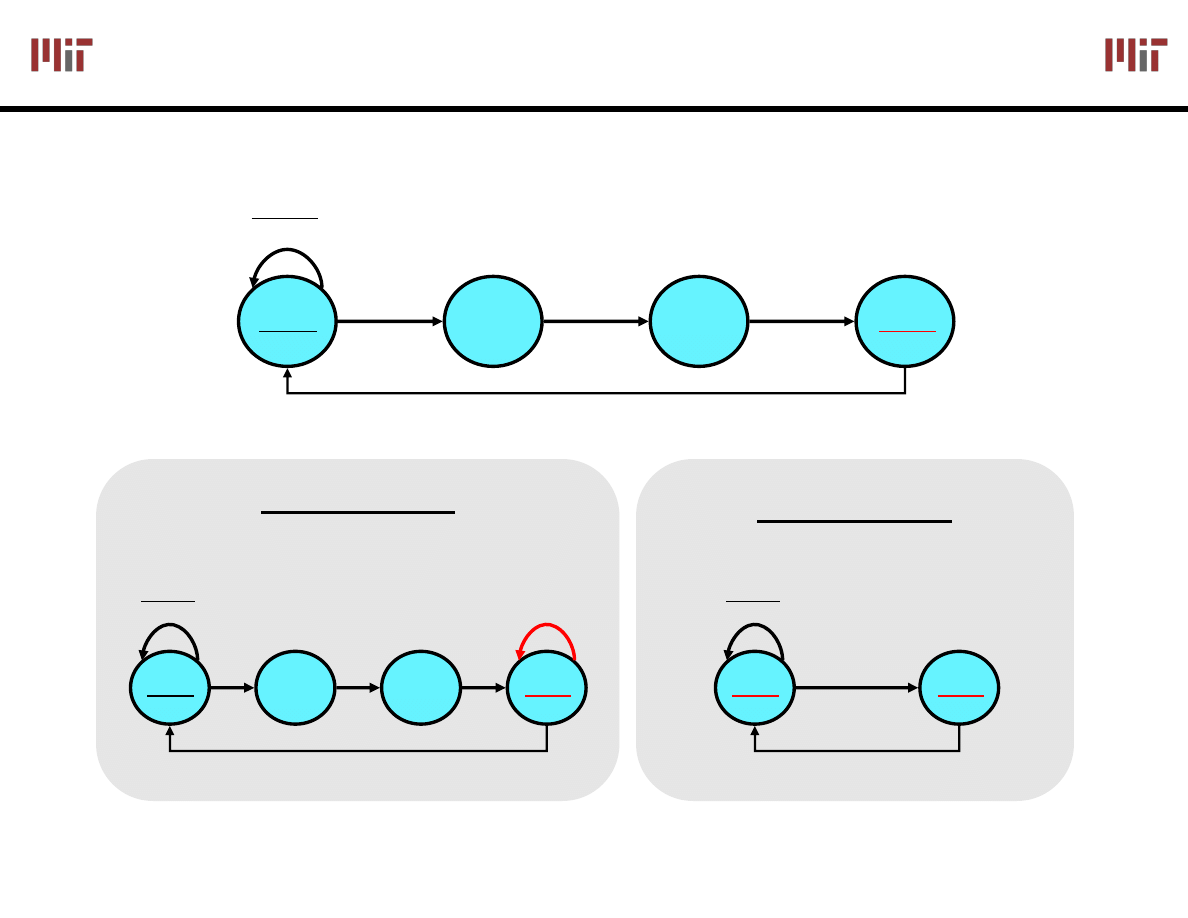

A Four

A Four

-

-

FSM Example

FSM Example

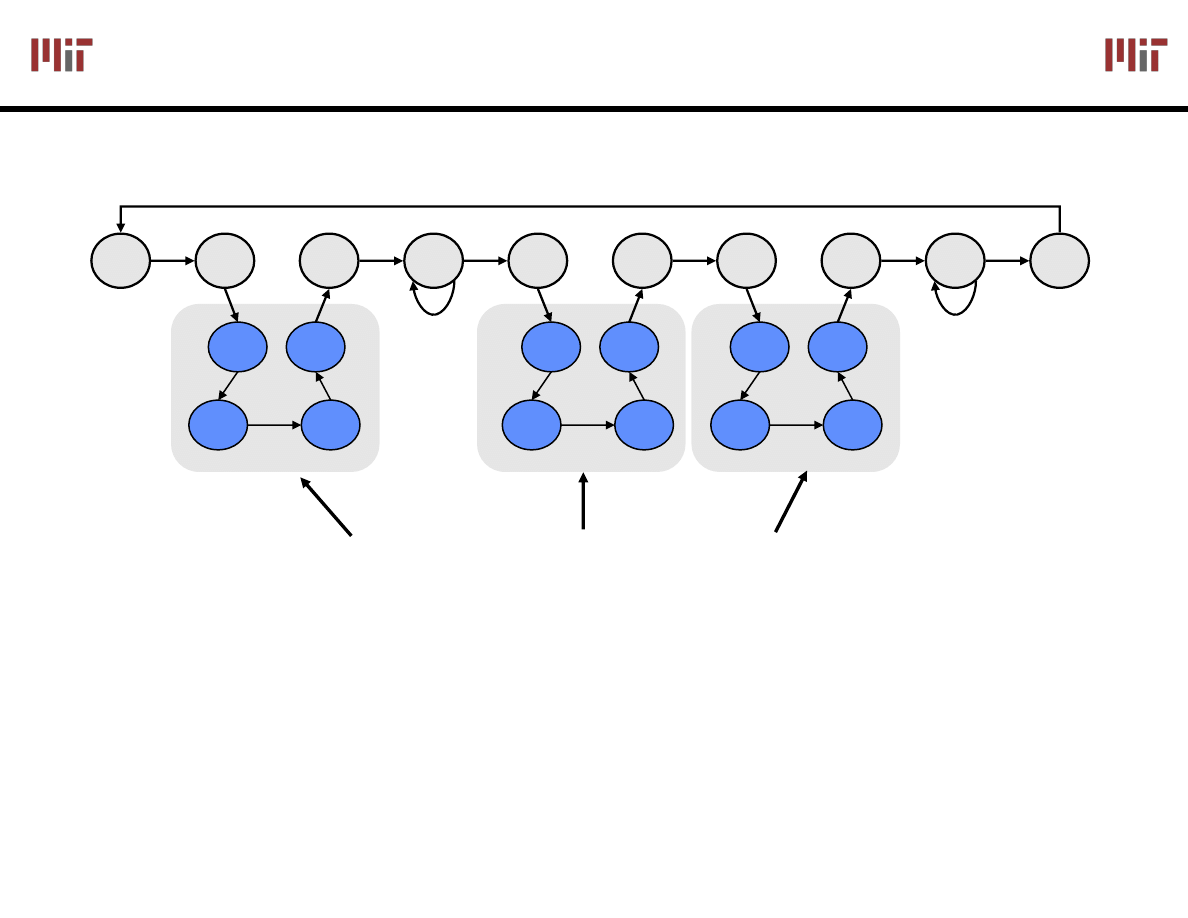

Operating Scenario:

Major FSM is triggered by

TICK

Minors A and B are started

simultaneously

Minor C is started once both

A and B complete

TICKs arriving before the

completion of C are ignored

Major FSM

Minor FSM A

Minor FSM B

START

A

START

B

BUSY

A

BUSY

B

Minor FSM C

START

C

BUSY

C

TICK

IDLE

ST

AB

START

A

START

B

WT

AB

TICK

BUSY

A

BUSY

B

TICK

BUSY

A

+BUSY

B

BUSY

A

+BUSY

B

ST

C

START

C

BUSY

A

BUSY

B

BUSY

C

WT

C

BUSY

C

BUSY

C

BUSY

C

Assume that BUSY

A

and BUSY

B

both rise before either minor

FSM completes. Otherwise, we

loop forever!

L11: 6.111 Spring 2006

10

Introductory Digital Systems Laboratory

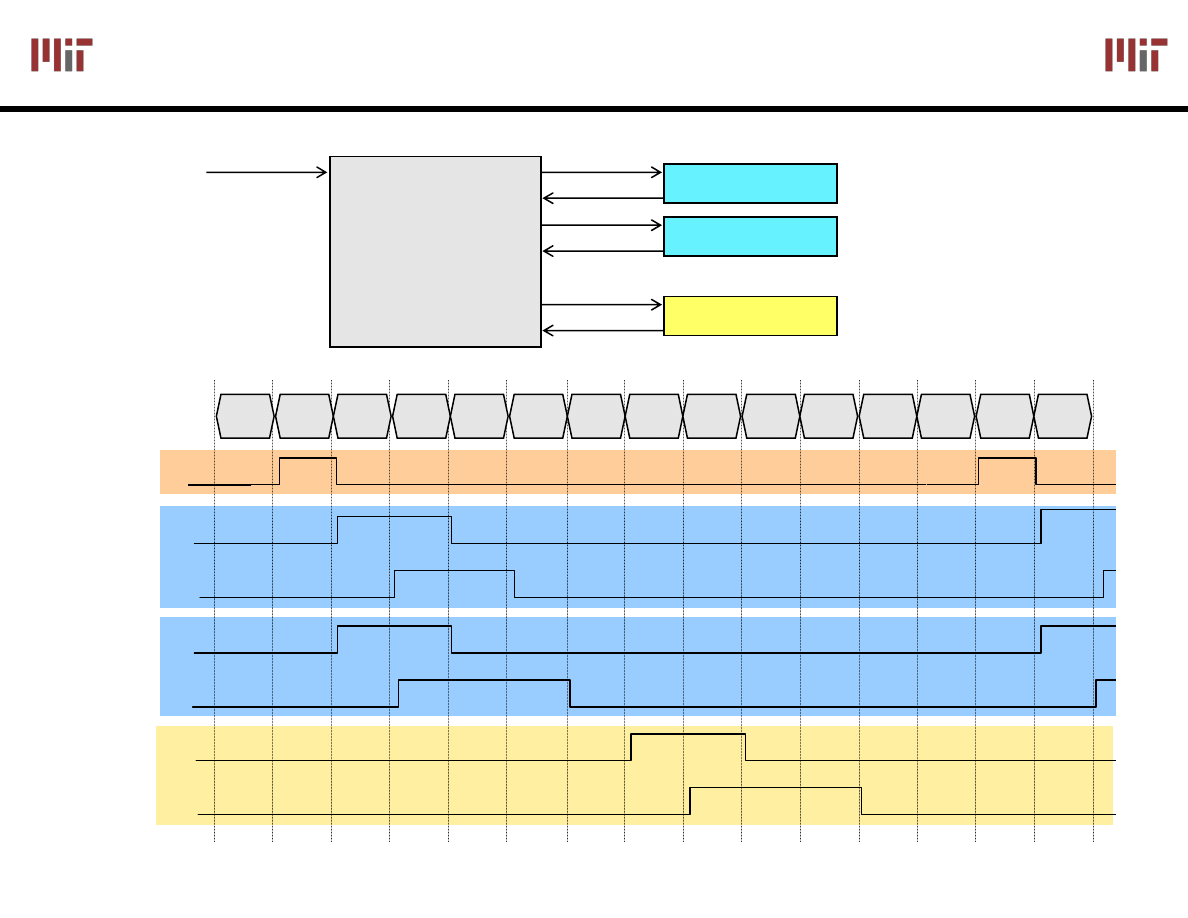

Four

Four

-

-

FSM Sample Waveform

FSM Sample Waveform

IDLE IDLE ST

AB

ST

AB

WT

AB

WT

AB

WT

AB

ST

C

ST

C

WT

C

WT

C

WT

C

IDLE IDLE ST

AB

state

tick

START

A

BUSY

A

START

B

BUSY

B

START

C

BUSY

C

Major FSM

Minor FSM A

Minor FSM B

START

A

START

B

BUSY

A

BUSY

B

Minor FSM C

START

C

BUSY

C

TICK

Document Outline

- L11: Major/Minor FSMs

- Quiz

- Quiz (cont.)

- Toward FSM Modularity

- The Major/Minor FSM Abstraction

- Inside the Major FSM

- Inside the Minor FSM

- Optimizing the Minor FSM

- A Four-FSM Example

- Four-FSM Sample Waveform

Wyszukiwarka

Podobne podstrony:

9 Zginanie uko Ťne zbrojenie min beton skr¦Öpowany

Znaki taktyczne i szkice obrona, natarcie,marsz maj 2006

17 Rozp Min Zdr w spr szk czyn Nieznany

geogr Maj 2008

Dot pyt 70 maj 2012

078c rozp zm rozp min gosp w spr szkolenia w dziedzinie bhp

2009 maj odp (2)

30 maj 2006, studia, agresja oligo itp, sztylka

ROZDZIAŁ X.1 WYBRANE OBIEKTY POŁUDNIOWEGO SKUPISKA O NIEUSTALONEJ CHRONOLOGII, MAGAZYN DO 2015, Nowe

Święci na każdy dzień -05- Maj, Dokumenty Textowe, Religia

Podatek od spadków i darowizn - informacje z Min. Fin, Prawo finansowe(19)

Maj 09 nowe pytania

więcej podobnych podstron