57

Elektronika Praktyczna 12/2005

P O D Z E S P O Ł Y

8–bitowy Lattice

Najczęstszym problemem na jaki

napotykają projektanci systemów cy-

frowych realizowanych w PLD jest

konieczność samodzielnego projek-

towania automatów (sekwenserów).

Ich opisy nie są co prawda – dzię-

ki wykorzystaniu nowoczesnych na-

rzędzi projektowych – trudne do

wykonania, ale różnorodność zadań

wymagających stosowania automa-

tów sterujących powoduje, że ich

projektowanie bywa jednym z naj-

bardziej żmudnych etapów projektu.

Niebagatelne znaczenie prak-

tyczne ma także fakt, że większość

projektantów elektroniki woli część

zadań realizować na drodze progra-

mowej, co również wiąże się z wy-

godą: łatwiej jest napisać program

obsługujący sterownik wyświetla-

cza LCD niż opisać jego działanie

w którymś z języków HDL (ale jest

to, oczywiście, możliwe!).

Jakie wyjście mają zatem użyt-

kownicy układów programowalnych?

Dość proste: do realizacji niektó-

rych zadań zastosować mikrokontro-

ler, najlepiej wbudowany w FPGA.

Od niedawna (kilku tygodni) taką

możliwość mają użytkownicy ukła-

dów PLD firmy Lattice, a to dzięki

opracowaniu o nazwie LatticeMico8.

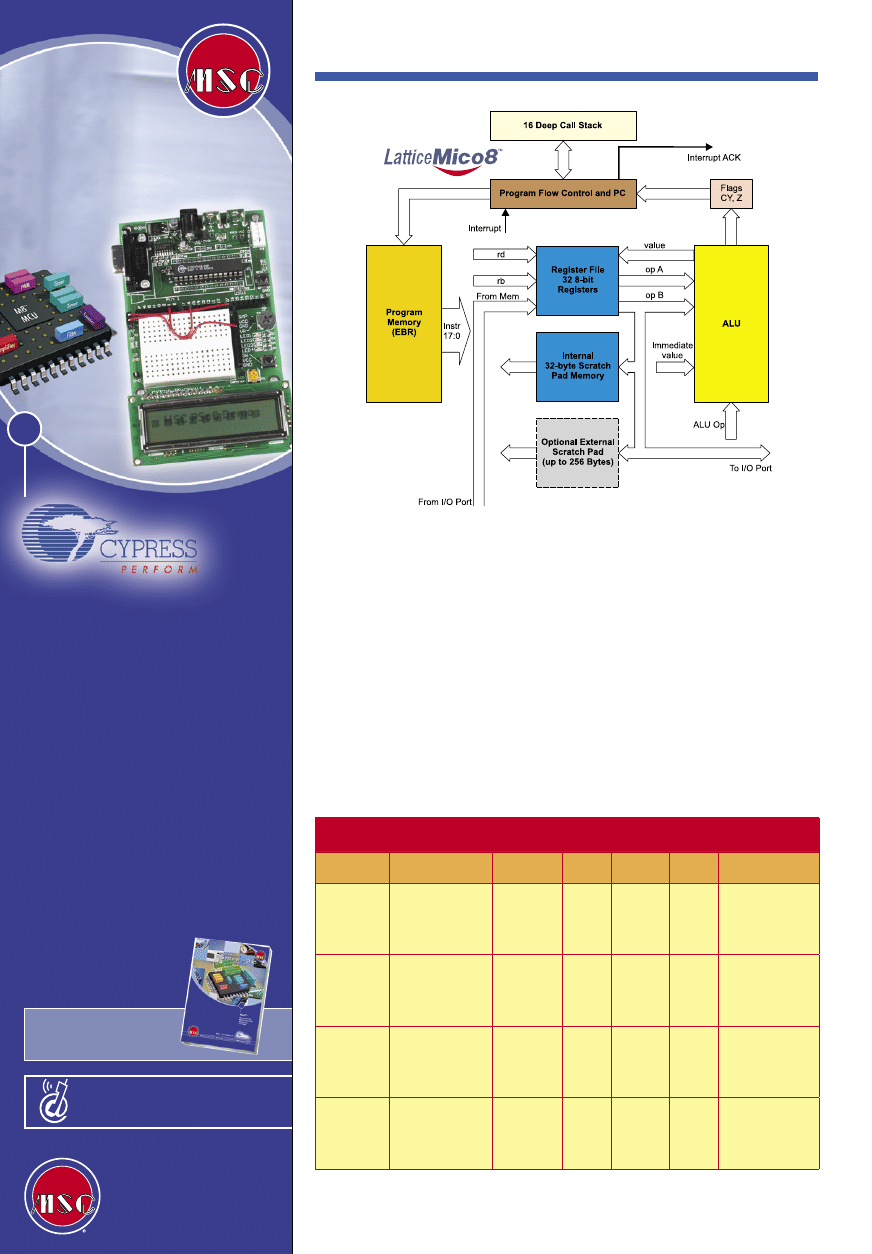

LatticeMico8 to rdzeń 8–bitowego

mikrokontrolera o dość prostej budo-

wie (

rys. 2), która jednak zapewnia

realizację wszystkich zadań stawia-

nych układom tego typu. Rdzeń skła-

da się z następujących elementów:

– 2–taktowego rdzenia zintegrowa-

nego z ALU,

– zespołu składającego się z 32 re-

jestrów 9–bitowych z możliwością

bezpośredniej wymiany ich za-

wartości z zawartością pamięci,

– 16–poziomowego stosu,

– jednostki obsługi przerwań,

– rejestru flag (jeden zestaw, bez

ich wymiany podczas obsługi

przerwań),

Mikrokontroler w FPGA

Lattice dla elektroników:

LatticeMico 8

Pierwszym producentem układów PLD, który bezpłatnie

udostępnił rdzeń (opisany w VHDL i Verilogu) mikroprocesora,

była firma Xilinx. Jej opracowanie – PicoBlaze – jest znane

Czytelnikom EP z cyklu artykułów, których publikację zaczęliśmy

w EP5/2005. Teraz przedstawiamy podobne opracowanie firmy

Lattice: LatticeMico8.

Powszechna dostępność coraz

tańszych układów FPGA umożliwia

użytkownikom integrację funkcjonal-

ną na niespotykaną wcześniej skalę.

Nawet najtańsze wersje współcze-

snych układów FPGA, niezależnie

od producenta, oferują zasoby umoż-

liwiające implementację kompletnych

systemów SoC (System–on–a–Chip),

w których coraz częściej istotną rolę

odgrywają kompletne mikroprocesory

(nawet takie jak PowerPC). Integracja

w jednej strukturze elastycznie kon-

figurowalnej logiki oraz równie ela-

stycznego (od strony programowej)

mikrokontrolera tworzą niezwykle

uniwersalną platformę sprzętowo–

–programową. Dotychczas najczęściej

oferowano układy FPGA, w których

rdzeń mikrokontrolera był wykonywa-

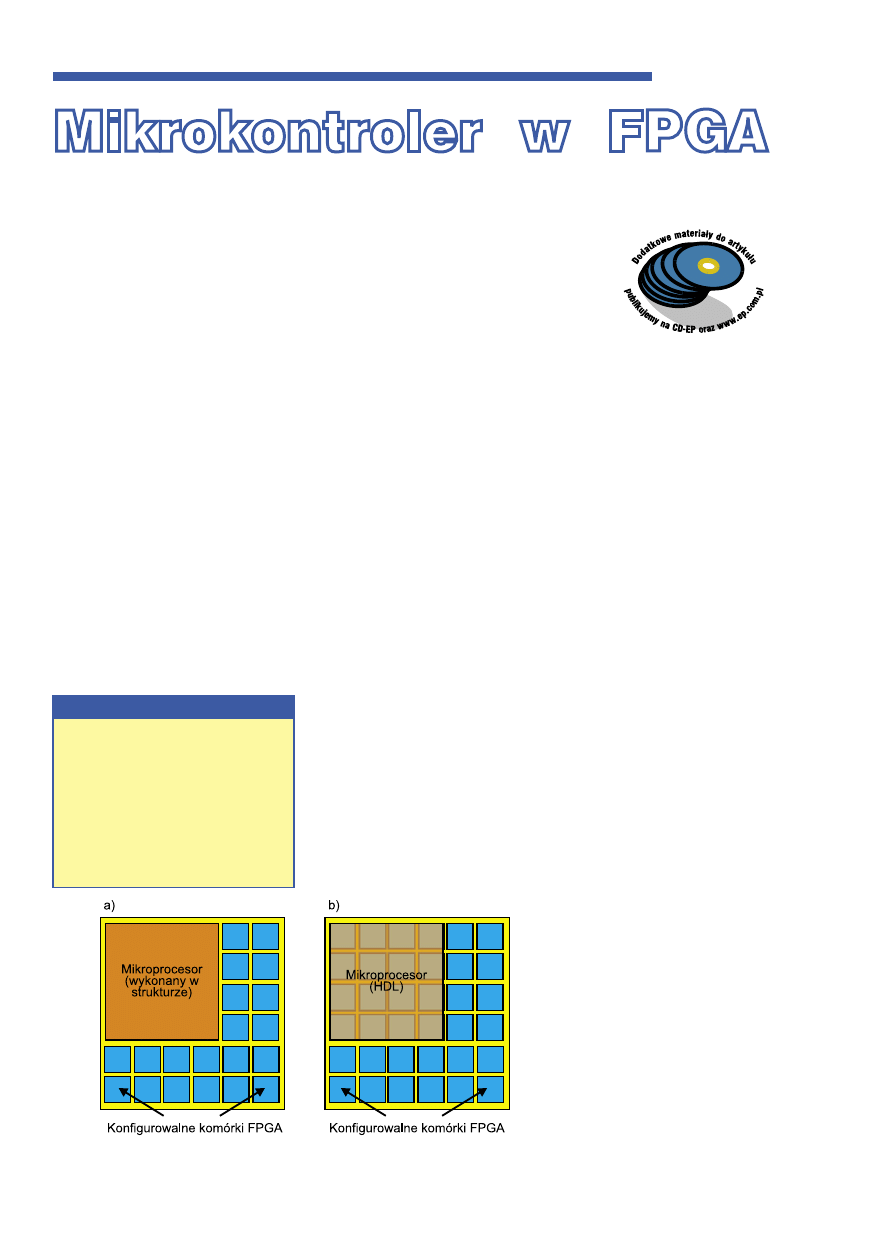

ny „na sztywno” w krzemie (

rys. 1a).

Od niedawna prym wiodą rozwią-

zania znacznie bardziej elastyczne:

rdzeń mikrokontrolera i jego peryfe-

ria są implementowane w struktu-

rze FPGA w taki sam sposób jak

pozostałe elementy logiczne –ich

opis HDL jest poddawany klasycznej

syntezie logicznej i „wpasowywaniu”

zoptymalizowanego opisu w dostępne

w układzie docelowym zasoby logicz-

ne (

rys. 1b). To drugie rozwiązanie

ma sporą zaletę: w zależności od

wymagań projektu w układ docelowy

można „wbudować” albo sam rdzeń,

albo rdzeń z wybranymi peryferia-

mi. Użytkownik ma więc możliwość

swobodnego kształtowania wykorzy-

stania zasobów platformy sprzętowej,

co nie jest możliwe w wersji z krze-

mowymi procesorami.

Rys. 1. System-on-Chip w wersji z mikroprocesorem wbudowanym w strukturę

krzemową a) i w wersji implementowanej z wykorzystaniem IPCore'a b)

Mikroprocesor na „miękko”

Coraz więcej peryferiów cyfrowych jest

dostępnych w postaci opisów HDL, często

nazywanymi peryferiami „miękkimi” (soft

cores). „Miękkość” odnosi się do sposobu

implementacji – narzędzia syntezy logicznej

potrafią dostosować opis HDL do możliwości

i budowy docelowego układu PLD (zazwyczaj

FPGA). Inaczej mówiąc, mając przygotowany

opis HDL jakiegoś modułu, możemy go

zastosować dla praktycznie dowolnego

układu docelowego (oczywiście, jeśli ma

wystarczające zasoby logiczne).

Elektronika Praktyczna 12/2005

58

P O D Z E S P O Ł Y

Rys. 2. Schemat blokowy rdzenia Mico8

– 32–bajtowej pamięci SRAM dla

podręcznych danych z możliwo-

ścią powiększenia jej pojemności

do 256 bajtów,

– do 256 linii I/O.

Pamięć programu LatticeMico8

jest implementowana w blokach EBR

(Embedded Block RAM – uniwersal-

ne zespoły SRAM) układów FPGA.

Słowo rozkazowe ma szerokość 18

bitów. Standardowo przestrzeń ad-

resowa (dla pamięci programu) jest

9–bitowa, co pozwala zaadresować

do 512 słów programu. Niewielka

modyfikacja w opisie HDL umożliwia

powiększenie przestrzeni adresowej,

co może spowodować zmniejszenie

maksymalnej dopuszczalnej częstotli-

wości taktowania rdzenia.

Lista rozkazów LatticeMico8

składa się z 50 instrukcji, wśród

których są dostępne zarówno in-

strukcje operacji logicznych i aryt-

metycznych (w tym porównań), sko-

ków i wywołań procedur, operacji

na znacznikach oraz portach I/O,

a także instrukcje sterujące.

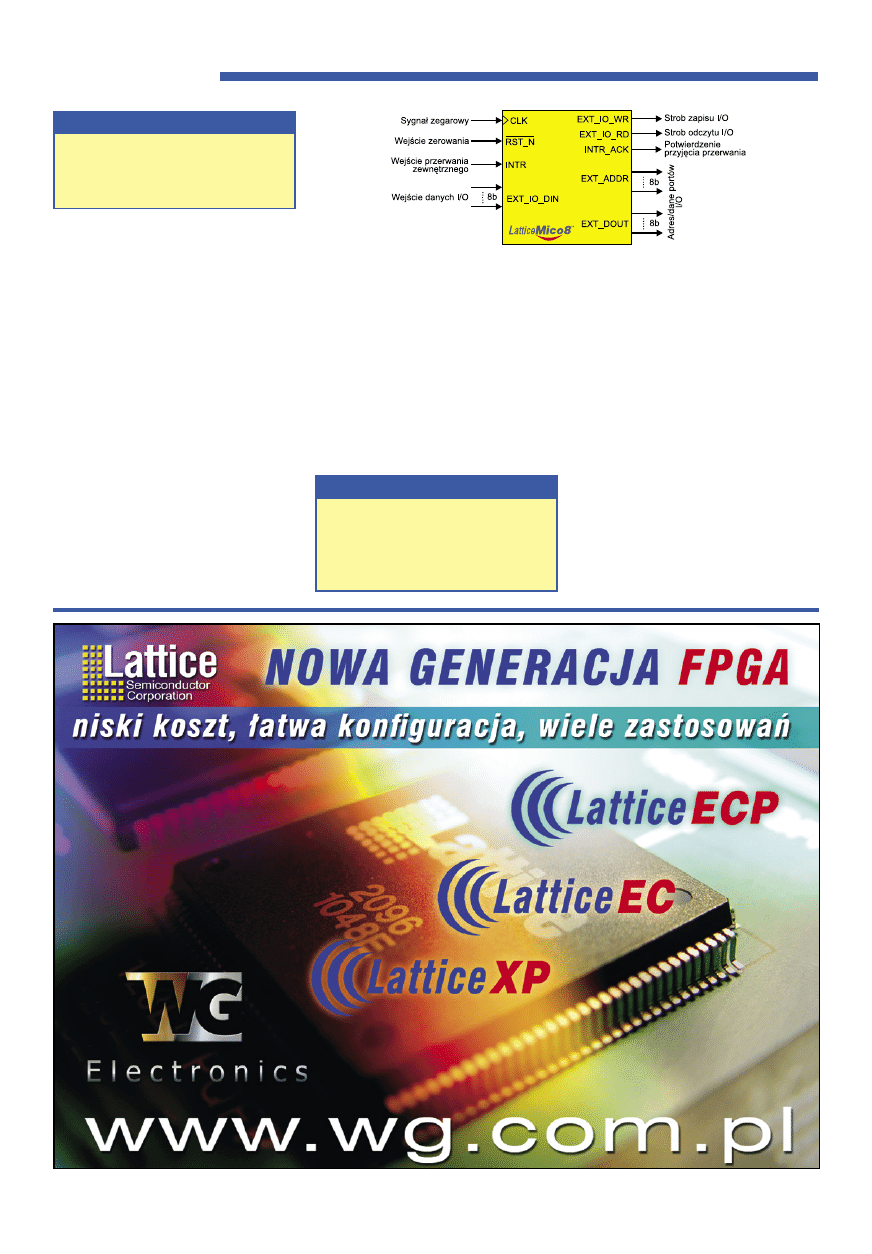

Prezentowany projekt został opra-

cowany wyłącznie (jak na razie)

w języku Verilog. Symbol graficzny

modułu mikrokontrolera utworzo-

ny po zsyntezowaniu jego opisu

Tab. 1. Zestawienie najważniejszych parametrów wybranych implementacji

rdzenia LatticeMico8 w układach FPGA firmy Lattice

Numer

konfiguracji

Opis konfiguracji

Typ

układu

Liczba

LUT

Rejestry

Liczba

SLICE

f

MAX

[MHz]

1

16 rejestrów

uniwersalnych,

16 B SP, bez

zewnętrznej

pamięci SRAM

LFXP3C–4,

LFEC3E–4

198

71

114

71,4 (LFXP3C–4)

77,1 (LFEC3E–4)

2

32 rejestry

uniwersalne,

16 B SP, bez

zewnętrznej

pamięci SRAM

LFXP3C–4,

LFEC3E–4

247

71

138

62,4 (LFXP3C–4)

68,8 (LFEC3E–4)

3

32 rejestry

uniwersalne,

32 B SP, bez

zewnętrznej

pamięci SRAM

LFXP3C–4,

LFEC3E–4

243

71

136

63,4 (LFXP3C–4)

70,0 (LFEC3E–4)

4

32 rejestry

uniwersalne,

32 B SP, bez

zewnętrznej

pamięci SRAM

LFXP3C–4,

LFEC3E–4

275

73

151

62,3 (LFXP3C–4)

65,6 (LFEC3E–4)

���������

�

������������

�

��

��

�����

����

��

�

�����������

���

���������������

������������������

����

����

���������������������

�����������

■�

������������������������������������

■�

���������

■�

��������������

■�

���������

■�

������������������������������

�����������������

��������������

■�

���������������������������������

■�

�������������������

■� �

�������������������������������

������������

����

����

�������

■�

�

�����������������������������������

�������������������������������

�������������

■�

�

����������������

������������������

��������������

�������������

���������������������

�����������������������

��������������

���������������������

��������������������

�������������

��������������

��������������

������������������

59

Elektronika Praktyczna 12/2005

P O D Z E S P O Ł Y

Konwerter 1–Wire –> SPI opisany w Verilogu

sterowniki.pl Sp. z o.o.

tel. (22) 499–88–39, www.sterowniki.pl

e–mail:sterowniki@sterowniki.pl

• Rockwell Automation posiada

w swej ofercie przemiennik czę-

stotliwości dedykowany aplikacjom

zmiennomomentowym. Po napędach

serii x4 oraz x40 przyszedł czas

na PowerFlex 400.

• Oferowany przez firmę Woodhead

GATEway: Ethernet TCP – Profibus

– Serial jest pierwszą platformą

sprzętową, która pozwala na rów-

noczesną komunikację pomiędzy

urządzeniami przemysłowymi przy

użyciu 20 różnych protokołów

Ethernetowych, Profibusowych i sze-

regowych.

• Międzynarodowy, niezależny koncern

TÜV Rheinland Group, zajmujący

się zapewnieniem oraz rozwojem

bezpieczeństwa i jakości produktów,

nadał wszystkim modułom Systemu

X67 certyfikat EX dla grupy II we-

dług standardu ATEX 7201.

• Budujemy bezprzewodową sieć.

Podłączenie przemysłowych urzą-

dzeń do bezprzewodowej sieci

Ethernet nie jest po prostu kolej-

nym wymysłem i jednosezonową

modą. Bezprzewodowa sieć WLAN

jest w rzeczywistości bardzo ko-

rzystnym rozwiązaniem dla wielu

aplikacji ze względu na elastycz-

ność pozwalającą zestawiać sieć

gdziekolwiek i kiedykolwiek oraz ła-

twość implementacji – bezprzewo-

dową sieć może zostać szybko ze-

stawiona w miejscach które np. nie

mają infrastruktury sieciowej lub

zbudowanie infrastruktury sieciowej

jest niemożliwe do zrealizowania.

• Działanie sterowników S7–200. Ro-

dzina sterowników PLC SIMATIC

S7–200 składa się z pięciu jedno-

stek centralnych: CPU221, CPU222,

CPU224, CPU226 i CPU226XM.

Różnią się one między sobą ilo-

ścią dostępnej pamięci programu

oraz pamięci danych, a także liczbą

zintegrowanych wejść–wyjść binar-

nych.

• Interfejs PROFIBUS od Hilscher.

Karty serii RIF rozszerzają możli-

wości komunikacyjne rodziny pro-

duktów FlexLogix i DriveLogix firmy

Rockwell Automation o standard

PROFIBUS. Były one testowane na

zgodność z najnowszymi wersjami

standardu PROFIBUS. Są tak za-

projektowane, aby można ich było

używać zarówno w sterownikach

PLC jak i w aplikacjach wykorzystu-

jących DriveLogix.

•

Przenośne systemy pomiarowe.

Systemy pomiarowe można po-

dzielić na 3 podstawowe grupy:

laboratoryjne, rozproszone i przeno-

śne. Systemy laboratoryjne i roz-

proszone są zazwyczaj systemami

stacjonarnymi, ponieważ to badany

obiekt jest dostarczany do systemu

pomiarowego.

01/12/2005 ControlLogix podstawy

programowania z RSLo-

gix 5000 – ELMARK

02/12/2005 ControlLogix podstawy

programowania z RSLo-

gix 5000 – ELMARK

05/12/2005 Napędy – KINETIX

– INTROL

06/12/2005 SLC–500 – Zaawanso-

wany kurs programo-

wania z RSLogix 500

– ELMARK

PLC–5 – Zaawansowany

kurs programowania

z RSLogix 5 – ELMARK

07/12/2005 SLC–500 – Zaawanso-

wany kurs programo-

wania z RSLogix 500

– ELMARK

08/12/2005 SLC–500 – Zaawanso-

wany kurs programo-

wania z RSLogix 500

– ELMARK

PLC–5 – Zaawansowany

kurs programowania

z RSLogix 5 – ELMARK

09/12/2005 SLC–500 – Zaawanso-

wany kurs programo-

wania z RSLogix 500

– ELMARK

PLC–5 – Zaawansowany

kurs programowania

z RSLogix 5 – ELMARK

12/12/2005 Sieć Przemysłowa Devi-

ceNet – ELMARK

ContolLogix zaawanso-

wany kurs programowa-

nia – INTROL

13/12/2005 Sieć Przemysłowa Devi-

ceNet – ELMARK

14/12/2005 Sieć Przemysłowa Con-

trolNet – ELMARK

15/12/2005 Sieć Przemysłowa Con-

trolNet – ELMARK

19/12/2005 ControlLogix – Obsługa

bieżąca i lokalizacja

uszkodzeń – ELMARK

20/12/2005 ControlLogix – Obsługa

bieżąca i lokalizacja

uszkodzeń – ELMARK

21/12/2005 ControlLogix – Obsługa

bieżąca i lokalizacja

uszkodzeń – ELMARK

Elektronika Praktyczna 12/2005

60

P O D Z E S P O Ł Y

Rys. 3. Symbol biblioteczny mikrokontrolera Mico8

(w wersji bez magistrali zewnętrz-

nej pamięci danych) pokazano na

rys. 3. W odróżnieniu od PicoBlaze’a.

prezentowany mikroprocesor nie ma

wyprowadzonych na „zewnątrz” ma-

gistral danych i adresowej, służących

do dostępu do pamięci programu

– jest ona zintegrowana z rdzeniem.

Narzędzia

Nawet najlepszy mikroprocesor nie

jest wiele wart bez kompilatora umoż-

liwiającego kompilację programów

napisanych w jakimś języku mnemo-

nicznym. Firma Lattice zadbała o po-

tencjalnych użytkowników mikroproce-

sora LatticeMico8 i przygotowała dwa

proste (niestety bez IDE, ale pracują

pod WinXP) programy narzędziowe:

kompilator i symulator. Udostępnione

zostały programy źródłowe obydwu

programów, co ułatwi samodzielne

udoskonalanie tych narzędzi.

PLD vs FPGA

PLD (Programmable Logic Devices) to

nazwa wszystkich programowalnych układów

logicznych, wśród których jedną z podrodzin

tworzą układy FPGA (Field Programmable

Logic Devices).

Przenosiny? Nie tak łatwo!

Zastosowanie opisu HDL przygotowanego

przez firmę Lattice nie da się bezpośrednio

przenieść do innego środowiska projektowego

niż ispLever. Wynika to z faktu wykorzystania

przez twórców opisu LatticeMico8 makr

predefiniowanych w tym środowisku.

Implementacja

Implementacja mikroprocesora

LatticeMico8 jest możliwa przy uży-

ciu bezpłatnego środowiska ispLever

(dostępne na stronie www.latticese-

mi.com

). Zsyntezowany rdzeń zaj-

muje 198…275 komórek LUT oraz

71…73 rejestrów (w zależności od

wersji –

tab. 1). Biorąc pod uwa-

gę, że najmniejsze dostępne układy

FPGA z rodziny LatticeXP wyposa-

żono w 3100 komórek LUT, w poje-

dynczym układzie tego typu można

zintegrować kilka mikroprocesorów

Mico8 (ograniczeniem będzie liczba

dostępnych bloków konfigurowalnej

pamięci) oraz zaawansowane pery-

feria. Biorąc dodatkowo pod uwa-

gę, że wydajność każdego mikro-

procesora przekracza (w najgorszym

przypadku) 30 MIPS, a niektórych

przypadkach dochodzi do 39 MIPS,

zyskujemy wydajną (w stosunku

do ceny) platformę obliczeniową,

której zaletą jest możliwość prak-

tycznie dowolnej aranżacji budo-

wy sprzętowej. Mówiąc w skrócie:

nowa jakość.

Piotr Zbysiński, EP

piotr.zbysinski@ep.com.pl

Wyszukiwarka

Podobne podstrony:

12 2005 035 038

12 2005 144 145

12 2005 048 056

12 2005 083 084

12 2005 090 093

12 2005 111 114

12 2005 071 074

12 2005 087 089

12 2005 075 078

Zjazd 6 - 11.12.2005, Zootechnika SGGW, Bydło(1)

12 2005 023 030

PO komun 07 12 12 2005

6 Rozp MG z dnia 15 12 2005 w sprawie wymagańdla sprzętu elektr

12 2005 031 032

ZDNA 12[1] 2005 A L

Antropologia kultury - wyk+éad z 09-12-2005, SOCJOLOgia, Antropologia

12 2005 127 129

cz06 12 2005

więcej podobnych podstron