Realizacja programów

Realizacja programów

przez komputer

przez komputer

w pierwszych komputerach programy były

wbudowane w procesor realizując zawsze ten sam

cykl rozkazów

koncepcja przypisywana von Neumannowi zakłada

reprezentację rozkazów (podobnie jak danych) jako

ciągu bitów składowanych w pamięci komputera i

jest dziś standardowym podejściem

komputer sterowany programem przechowywanym

w pamięci należy tak zaprojektować, aby

rozpoznawał różne rozkazy (ciągi bitów)

zestaw rozkazów wykonywanych bezpośrednio

przez komputer (procesor) tworzy język maszynowy

Cykl maszynowy (von

Cykl maszynowy (von

Neumanna

Neumanna

)

)

1.

Pobierz rozkaz z pamięci operacyjnej i umieść go w

rejestrze rozkazów

2.

Zmodyfikuj

licznik rozkazów

o 1

3.

Dekoduj rozkaz

4.

Wykonaj rozkaz (ew. pobierz dane niezbędne do

wykonania rozkazu, zapisz wyniki)

5.

Jeżeli licznik rozkazów nie wskazuje wartości

większej niż długość listy rozkazów to przejdź do

początku cyklu

Uwaga ! Dane tak jak rozkazy są reprezentowane w

postaci ciągu bitów więc pobranie zamiast rozkazu

bloku danych może skutkować próbą ich realizacji

jako rozkazu.

W przypadku gdy możliwość

W przypadku gdy możliwość

wykonywania rozkazu jest przypisana

wykonywania rozkazu jest przypisana

bezpośrednio procesorowi mówimy o

bezpośrednio procesorowi mówimy o

sprzętowej realizacji polecenia

sprzętowej realizacji polecenia

. Jeżeli

. Jeżeli

zaś rozkaz jest najpierw zamieniany

zaś rozkaz jest najpierw zamieniany

na cykl poleceń możliwych do

na cykl poleceń możliwych do

wykonania przez elementy sprzętowe

wykonania przez elementy sprzętowe

mówimy

mówimy

o programowej realizacji

o programowej realizacji

polecenia.

polecenia.

Model N-poziomowego

Model N-poziomowego

wirtualnego urządzenia

wirtualnego urządzenia

komputerowego

komputerowego

tylko najniższy poziom (P

1

)

jest poziomem rzeczywistej,

sprzętowej realizacji poleceń

są tworzone kolejne poziomy ,

(P

2

,..P

n

), dla których polecenia

wykonywane są programowo,

a następnie przez

odpowiednie translatory

sprowadzane (tłumaczone) na

poziom niższy

każdy poziom jest zatem ściśle

określony przez swój język

i zasady działania translatora

tego poziomu

P

1

P

2

P

n

L

1

L

2

L

n

Poziomy rzeczywistych

Poziomy rzeczywistych

urządzeń komputerowych

urządzeń komputerowych

poziom języka maszynowego

(wewnętrznego) realizowanego przez

procesor, czyli poziom programowania w

języku elektroniki (mikroprogramowania

sprzętowego) -P

1

konwencjonalny poziom maszynowy

(poziom asemblera) - P

2

poziom systemu operacyjnego - P

3

poziomy wyższe (języka symbolicznego,

języków programowania wysokiego rzędu)

Język asemblera

Język asemblera

każda instrukcja odpowiada w układzie 1:1

instrukcji języka maszynowego (procesora)

w miejsce kodu binarnego (język maszynowy)

instrukcje i argumenty zapisuje się w sposób

symboliczny, czytelny dla człowieka

asembler to kompilator języka asemblerowego

programowanie w języku asemblera daje możliwość

bezpośredniego operowania na zasobach komputera

każda rodzina procesorów o wspólnym tzw. modelu

programowym procesora ma odrębny asembler

program w języku asemblera składa się z dyrektyw

dla kompilatora oraz instrukcji procesora

Metody tłumaczenia (translacji)

Metody tłumaczenia (translacji)

rozkazów języka wyższego

rozkazów języka wyższego

poziomu na język niższego

poziomu na język niższego

poziomu w ujęciu teoretycznym

poziomu w ujęciu teoretycznym

kompilacja -ciąg rozkazów języka wyższego

poziomu jest tłumaczony na ciąg rozkazów

języka niższego poziomu. Docelowo powstaje

program w języku asemblera, który

następnie jest wykonywany. Czasami

poprzedza jego powstanie postać pośrednia

interpretacja - polecenia języka wyższego

poziomu są tłumaczone po kolei na polecenia

języka niższego poziomu i od razu

wykonywany. Nie powstaje program w języku

niższego poziomu, ani postać pośrednia

Inne pojęcia związane z

Inne pojęcia związane z

tworzeniem programów

tworzeniem programów

określonego poziomu

określonego poziomu

asemblacja – plik w języku asemblera lub

tymczasowy wygenerowany w efekcie

kompilacji jest zamieniany na postać

pośrednią lub od razu wynikową (jeśli

program składa się z jednego tylko modułu)

łączenie (konsolidacja)- proces

przekształcenia postaci pośredniej poprzez

połączenie m.innymi z tzw. bibliotekami w

postać wynikową

Pierwsza koncepcja modelu

Pierwsza koncepcja modelu

procesora służąca realizacji cyklu

procesora służąca realizacji cyklu

von Neumanna(realizacji programów

von Neumanna(realizacji programów

napisanych w języku wysokiego

napisanych w języku wysokiego

poziomu)

poziomu)

w projektowaniu pierwszych komputerów

szło o wykonanie urządzenia, które

dostatecznie długo mogłoby pracować

bezawaryjnie

obecne architektury komputerów

projektowane są z ideą dostosowania się do

programowania komputerów w językach

wysokiego poziomu (idzie o wydajną

translację i wykonanie tak napisanych

programów)

Pierwsza koncepcja modelu

Pierwsza koncepcja modelu

procesora służąca realizacji cyklu

procesora służąca realizacji cyklu

von Neumanna(realizacji programów

von Neumanna(realizacji programów

napisanych w języku wysokiego

napisanych w języku wysokiego

poziomu)

poziomu)

rejestry: rejestr danych (tzw. akumulator),

licznik instrukcji(wskazuje adres kolejnej

wykonywanej instrukcji, powiększony po jej

wykonaniu)

stos (przechowywanie parametrów i zmiennych

wywoływanych instrukcji i procedur), ale bez

określania szczegółów realizacyjnych

argumenty na stosie są umieszczane w

kolejności od ostatniego do pierwszego

stos jest tworzony w pamięci operacyjnej

komputera

Odwołanie do stosu we

Odwołanie do stosu we

współczesnych

współczesnych

architekturach

architekturach

ograniczenie odwołań stosu do pamięci

(bo wolniejszy dostęp)

umieszczenie wybranych obiektów stosu

bezpośrednio w rejestrach procesora

skutek uboczny: skomplikowanie

wywoływania procedur

nowe rejestry i metody adresowania

odwołanie do zmiennych poprzez

adresowanie względem wskaźnika stosu, a

nie przez nazwę

Definicja użytkowego

Definicja użytkowego

modelu programowego

modelu programowego

procesora

procesora

zestaw zasobów logicznych komputera, które

są do dyspozycji bądź kompilatora

tłumaczącego program napisany w języku

wysokiego poziomu bądź programisty

piszącego w języku asemblera –synonim pojęcia

architektura

jest strukturą logiczną – nie mającą żadnego

związku z budową i strukturą komputera, wiele

różnych rodzin komputerów czy też procesorów

może mieć identyczny model programowy

Składniki modelu

Składniki modelu

programowego

programowego

liczba i funkcjonalność rejestrów

procesora

typy adresowania (sposoby określania

argumentów operacji)

model wykonywania operacji

warunkowych

lista instrukcji procesora, czyli

zestawienie możliwych do wykonania

przez niego operacji

Funkcje rejestrów

Funkcje rejestrów

akumulator – argument źródła i

przeznaczenie dla operacji arytmetycznych i

logicznych

rejestry adresowe – służą do uzyskania

adresu danej umieszczonej w pamięci.

Zależnie od trybu adresowania mamy

rejestry bazowy, indeksowy, wskaźnik stosu

itp.

liczniki pętli- liczą liczbę wykonań

powtórzeń instrukcji (pętli)

Wybrane koncepcje

Wybrane koncepcje

organizacji zestawu

organizacji zestawu

rejestrów

rejestrów

architektury bezrejestrowe - istnieją 1-3 rejestry

służące wyłącznie do przechowywania adresów,

operacje arytmetyczno-logiczne wykonywane są w

układzie pamięć-pamięć bez pośrednictwa

rejestrów- model dziś już praktycznie nie istniejący

architektury z minimalnym zestawem rejestrów –

istnieje akumulator (do przechowywania wartości),

wskaźnik stosu i licznik instrukcji –wolna

realizacja programów, gdyż wymaga zbyt częstych

odwołań do pamięci. Architektura bardziej

popularna dziś w mikrokontrolerach niż w

klasycznych komputerach

Wybrane koncepcje

Wybrane koncepcje

organizacji zestawu

organizacji zestawu

rejestrów

rejestrów

mały zestaw rejestrów specjalizowanych –

rozwinięcie poprzedniej architektury o 6-8

dodatkowych rejestrów o bardzo sztywno

określonych zadaniach. Rejestry te wykorzystuje się

jednak wyłącznie w procesach obliczeniowych,

głownie do przechowywania tymczasowych wyników

pośrednich, a nie danych i parametrów tych

procesów. Mimo znaczącej pojemności tych rejestrów

nie można ich zbyt efektywnie wykorzystać

mały zestaw rejestrów uniwersalnych – również 6-8

rejestrów, ale o zadaniach uniwersalnych (mogą być

wykorzystywane dowolnie jako akumulatory lub

rejestrów adresowych), 3-4 z nich mogą być

Wybrane koncepcje organizacji

Wybrane koncepcje organizacji

zestawu rejestrów

zestawu rejestrów

mały zestaw rejestrów uniwersalnych cd. - też wykorzystane

do przechowywania danych, co znacznie przyspiesza

wykonywanie programów, koncepcja znacznie

elastyczniejsza , pojawiły się wraz z procesorami 32-

bitowymi

duży zestaw rejestrów uniwersalnych – 16-32 uniwersalne

rejestry o dowolnym przeznaczeniu,może być

przekazywanych kilka zmiennych i parametrów,

ograniczenie odwołań do pamięci. Architektura

charakterystyczna dla współczesnych jednostek

stosowy zestaw rejestrów – 3-8 rejestrów o strukturze

stosowej bez-nazwowych, operacje wykonywane na

wierzchołkach stosu. Architektura ta upraszcza proces

kompilacji choć jest trudna do realizacji we współczesnych

jednostkach.

Tryby adresowania

Tryby adresowania

pojęcie to odnosi się do sposobu w jaki

podane zostają argumenty danej operacji

zależnie od kontekstu pojęcie to może

mieć dwa znaczenia: adresowanie

odpowiedniego obszaru pamięci ( z

danymi) oraz w wersji rozszerzonej

dodatkowo odnosić się może do danych z

rejestrów i stałych używanych w różnych

operacjach

Podstawowe tryby

Podstawowe tryby

adresowania

adresowania

Adresowanie bezpośrednie:

–

tryb natychmiastowy – argumenty operacji podane

bezpośrednio w instrukcji

–

tryb rejestrowy bezpośredni – argumenty operacji

pobierane do rejestru

Adresowanie pośrednie

–

tryb rejestrowy pośredni -dane generalnie w pamięci, a w

rejestrze tylko ich adres, w zależności od szczegółowych

wariantów może to być pełny adres, lub jego część (druga

część jest uzupełniana przy pomocy zawartości innego

rejestru, stałej z pamięci, albo powstaje przez

przekształcenie zawartości rejestru w kombinacji z

danymi z pamięci)

–

tryb pamięciowy pośredni – dane zawarte w pamięci pod

adresem, którego część pozyskuje się również z pamięci

(dwukrotne odwołanie do pamięci)

Przeznaczenie trybów

Przeznaczenie trybów

adresowania

adresowania

natychmiastowy- ładowanie do rejestru stałych lub

adresów danych statycznych (nieprzemieszczalnych

w pamięci)

bezpośredni rejestrowy – działania związane wprost

ze wstawieniem do rejestru argumentów

statycznych operacji

tryby pośrednie rejestrowe- adresowanie danych

względem adresu bieżącej instrukcji, danych

wplecionych w kod programu lub logicznie do niego

należących, bardzo optymalne dla procesorów 64-

bitowych

tryby pośrednie pamięciowe-mało elastyczne,

charakterystyczne dla złożonych architektur, dzisiaj

raczej zastępowane bezpośrednim fragmentem kodu

programu

Modele realizacji instrukcji

Modele realizacji instrukcji

warunkowych

warunkowych

w realizowanych instrukcjach jest wiele

momentów decyzyjnych i sposób w jaki

następuje dla danego procesora rozstrzyganie

tych momentów warunkowych jest istotnym

składnikiem jego modelu programowego

wchodzą w grę następujące możliwości

–

wykorzystanie znaczników operacji – wybrane

operacje zależnie od ich wyniku (zero lub nie, znak

liczby, parzysta liczba bitów lub nie) ustawiają w

rejestrze bit 0 lub 1, kolejna instrukcja przyjmuje

postać zależną od wartości tego bitu (znacznika)

Modele realizacji instrukcji

Modele realizacji instrukcji

warunkowych-cd

warunkowych-cd

kolejne możliwości

–

model z predykatami –znaczniki występujące w

większej liczbie i dotyczące licznych wcześniej

wykonanych operacji, wykonanie określonej

instrukcji warunkowej zależy od

przetestowania znacznika (predykatu) o

określonym numerze-model stosowany np. w

architekturze Intela Itanium

–

model bez znaczników – operacja uzależniona

od testu relacji np. od testu argumentów

aktualnie znajdujących się w rejestrze

Ogólne informacje o strukturze

Ogólne informacje o strukturze

rozkazu maszynowego

rozkazu maszynowego

ciąg bitów tworzących rozkaz można podzielić na

niezależne dwa pole tzw. kod operacji i pole

argumentu

pole kodu operacji określa typ operacji jaką należy

wykonać

pole argumentu zawiera szczegóły zależne od

operacji (np. informację, w której komórce pamięci

umieścić wynik operacji)

szczegółowe formaty rozkazów, sposoby

adresowania komórek pamięci i tzw. lista rozkazów

są charakterystyczne dla danego typu procesora.

Przykładowe rozkazy

Przykładowe rozkazy

realizowane przez procesory

realizowane przez procesory

arytmetyka stało i zmiennopozycyjna

arytmetyka wysokiej precyzji

rozkazy cykliczne (pętle)

rozkazy wywoływania procedur

rozkazy zliczające (np. dodanie 1 do zmiennej)

rozkazy operujące na ciągach znaków

rozkazy związane z przemieszczaniem

programów w pamięci (alokacja)

realizacja systemów przerwań

Wybrane modele

Wybrane modele

programowe

programowe

podejście CISC

podejście RISC

podejście VLIW

Ogólna charakterystyka

Ogólna charakterystyka

procesorów CISC-podejście

procesorów CISC-podejście

starsze

starsze

każdej instrukcji języka wysokiego poziomu

odpowiada (jedno lub więcej ) instrukcja procesora

rejestry przechowują adresy i wyniki pośrednie, a

dane są w pamięci

maksymalnie 16 rejestrów, praktycznie wszystkie

tryby adresowania

operacje warunkowe z użyciem znaczników

wady: skomplikowane instrukcje, spowalniająca

wykonanie programu duża liczba odwołań do

pamięci, długie rozkazy ( pole argumentu) ze

względu na skomplikowane i liczne tryby

adresowania

Ogólna charakterystyka

Ogólna charakterystyka

procesorów RISC-podejście do

procesorów RISC-podejście do

większości procesorów po 1985

większości procesorów po 1985

wybrane dane procedur przechowywane także w

rejestrach

od 16 do 32 rejestrów

dane lokalne nie są „zamazywane” w trakcie

realizacji obliczeń

rzadkie odwołania do pamięci – niepotrzebne

skomplikowane tryby adresowania (krótsze i

prostsze kody instrukcji)

uproszczona konstrukcja jednostki wykonawczej

procesora

większość instrukcji działa na rejestrach, a tylko

niektóre na pamięci

Ogólna charakterystyka

Ogólna charakterystyka

procesorów RISC

procesorów RISC

jeden lub dwa tryby adresowania

(pośrednie)

więcej, ale krótszych instrukcji

(stała długość instrukcji)

RISC stanowi odzwierciedlenie

koncepcji szybkiego procesora o

prostej budowie

Architektura komputera-

Architektura komputera-

przetwarzanie potokowe

przetwarzanie potokowe

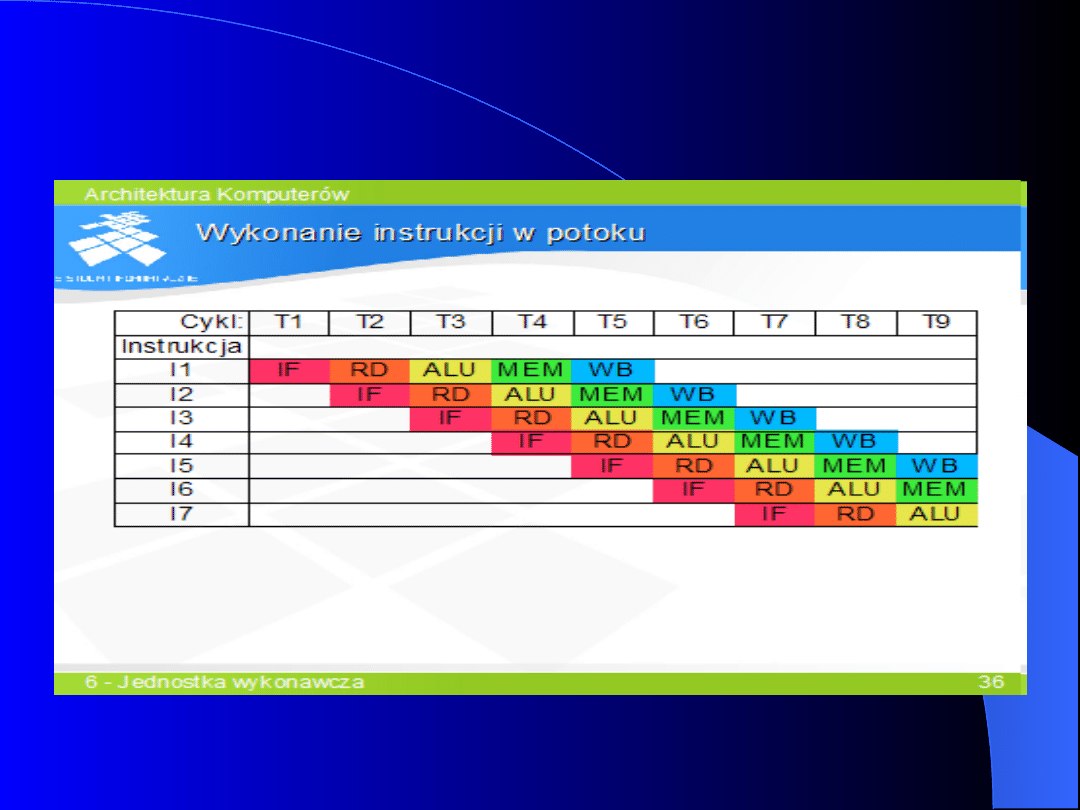

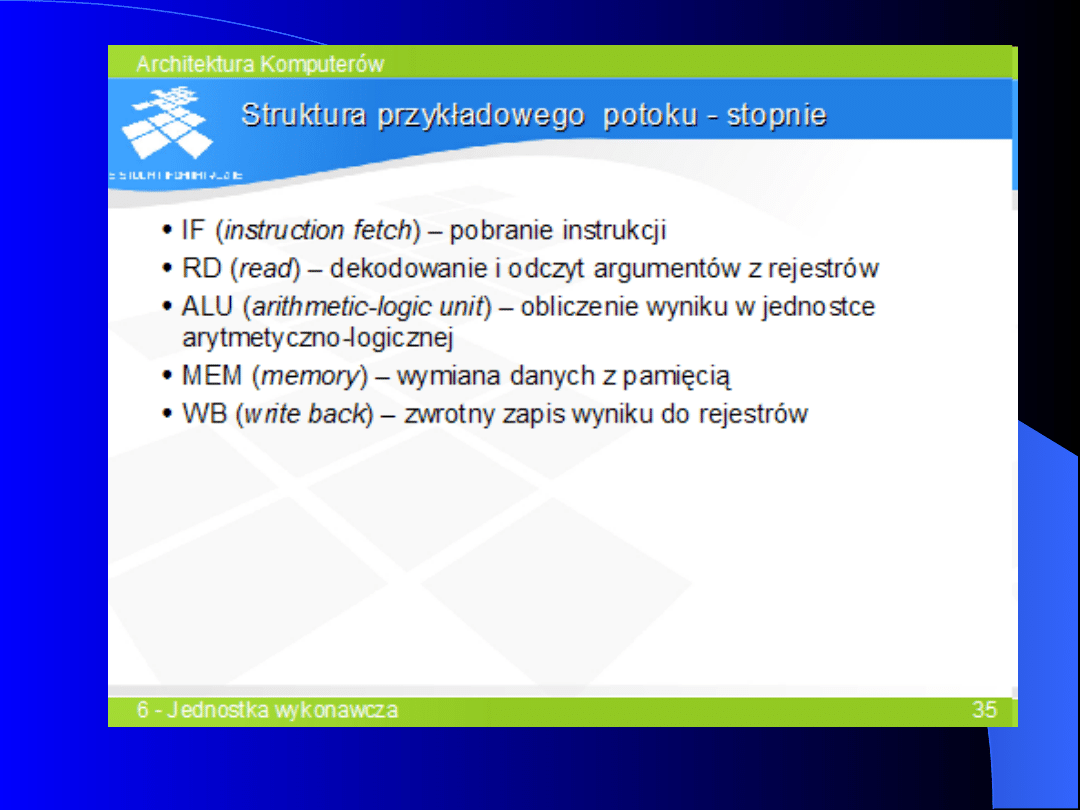

następuje podział czasu pracy nad

kolejnym rozkazem na odrębne fazy

przetwarzanie przypomina taśmę

produkcyjną (potok przetwarzania)

potok pracuje jednocześnie nad kilkoma

rozkazami, z których każdy znajduje się

w innej fazie przetwarzania

w przeciwieństwie do taśmy

produkcyjnej w momencie wystąpienia

błędu czyszczony jest cały potok

Idea procesora

Idea procesora

potokowego (potoku)

potokowego (potoku)

Źródło: mimuw.ważniak.edu.pl

Źródło: mimuw.ważniak.edu.pl

Problemy i uwagi związane z

Problemy i uwagi związane z

potokiem

potokiem

hazard

konieczność wstawiania pustych instrukcji

opóźnienia

wzrost częstotliwości procesorów oddziaływuje także na

potoki (w skrajnym przypadku bardziej złożone stopnie

mogą przestać działać, dostęp do hierarchii pamięci w

jednym cyklu utrudniony)-przyspieszenie potoku na

drodze zwiększania częstotliwości procesora ma zatem

ograniczenie, inna metodą jest zwiększenie liczby stopni

co prowadzi do konstrukcji superpotoku

potok jest dostosowany do koncepcji RISC, dostosowanie

potoku do modelu programowego CISC wiąże się z

konstrukcja mieszaną (jednostka pobierająca instrukcje-

CISC, jednostka wykonawcza-RISC)

Od procesora potokowego do

Od procesora potokowego do

wielopotokowego (superskalarnego)

wielopotokowego (superskalarnego)

teoretyczna wydajność procesora

potokowego to jedna instrukcja na cykl

nie ma możliwości wykonania instrukcji

w ułamku cyklu, ale można doprowadzić

do konstrukcji, w której w jednym cyklu

będzie wykonana więcej niż jedna

instrukcja-taki procesor musi mieć kilka

potoków wykonawczych

Superskalar

Superskalar

Źródło: mimuw.ważniak.edu.pl

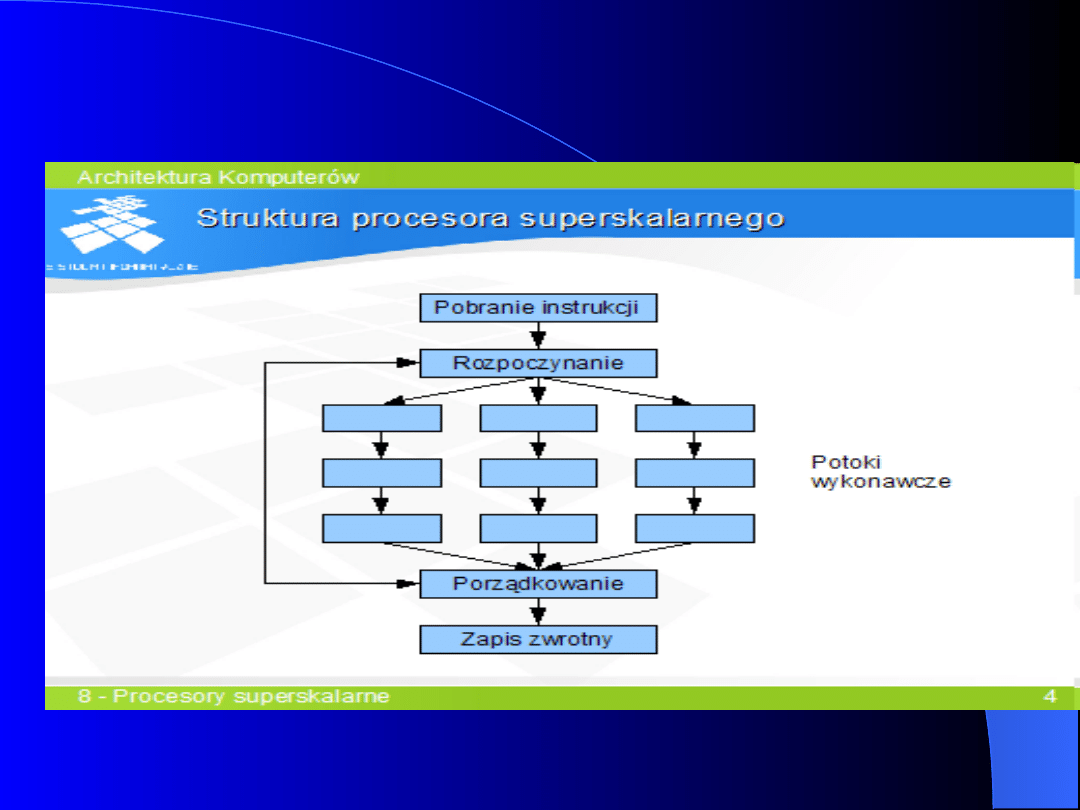

Superskalar-działanie

Superskalar-działanie

pierwsze stopnie potoku pobierają i dekodują

kilka strumieni instrukcji

każdy strumień instrukcji trafia do

indywidualnego potoku wykonawczego, które

wykonują pojedyncze instrukcje

stopień porządkujący decyduje o zatwierdzeniu

wykonania instrukcji i modyfikacji licznika

rozkazów

stopień zapisu dokonuje nieodwracalnej

modyfikacji rejestru i pamięci ( w prostych

superskalarach każdy potok wykonawczy ma swój

stopień zapisu)

Systemy

Systemy

wieloprocesorowe

wieloprocesorowe

przetwarzanie klasyczne równoległe a nie

tylko częściowo (procesory

wielordzeniowe)

inne problemy : efektywne wykorzystanie

procesorów (równoważenie obciążeń,

skalowanie), panowanie nad koordynacją

i złożonością rozproszonego przydziału

zadań procesorom

sieci neuronowe ?

Potrzeba ochrony zasobów

Potrzeba ochrony zasobów

w warunkach pracy potokowej, czy

uogólniając wieloprocesorowej ważne

jest, aby realizowane niezależnie

procesy wzajemnie nie zakłócały

swojej pracy, ani też nie „szpiegowały

się”

mechanizmy ochrony maja

zagwarantować niezakłóconą

realizacje poszczególnych procesów

Co podlega ochronie

Co podlega ochronie

procesor –nie może go zmonopolizować

jeden proces

pamięć – procesy mogą mieć dostęp

tylko do przydzielonych zasobów

pamięci

wejście-wyjście – dostęp do tych

urządzeń ma być taki, aby realizowane

procesy wzajemnie nie przeszkadzały

sobie

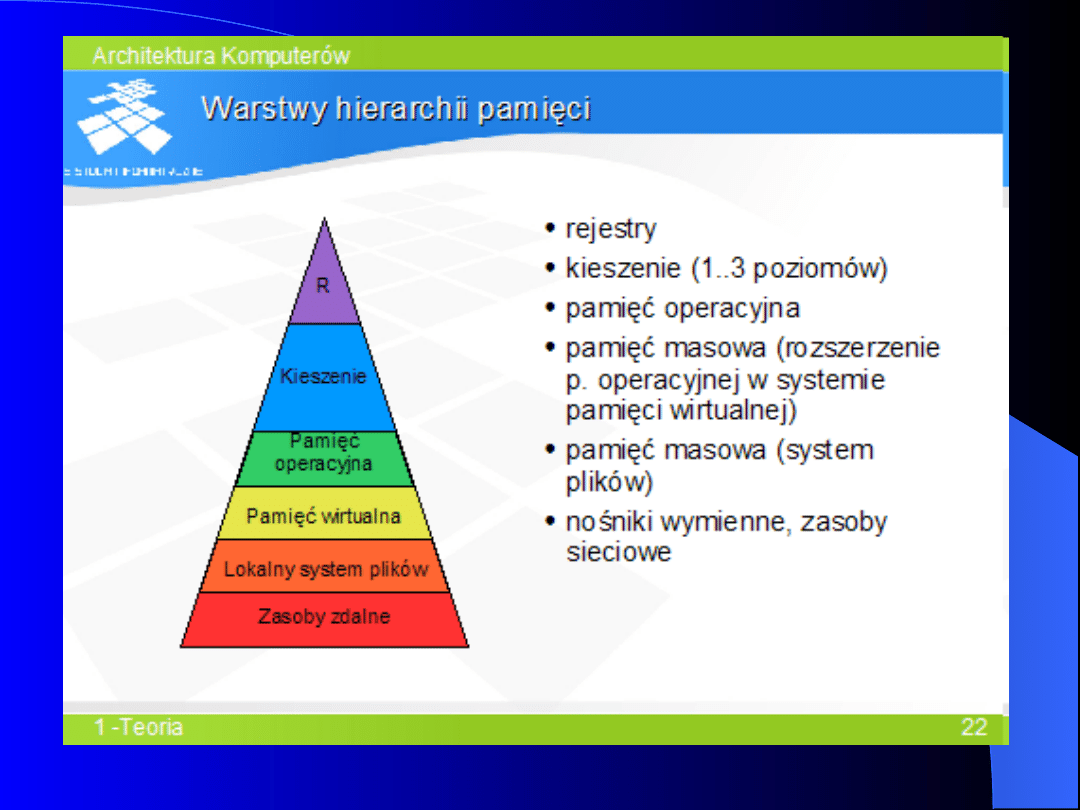

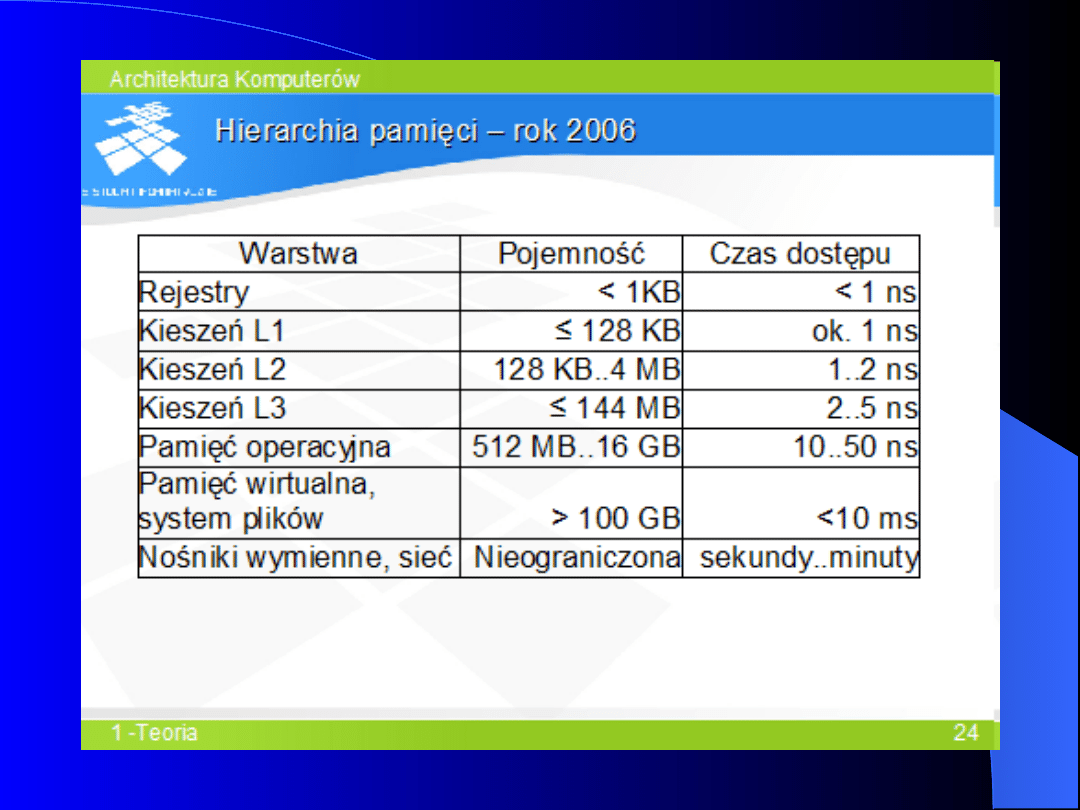

Hierarchia pamięci

Hierarchia pamięci

zwiększanie pojemności pamięci jest wprost

proporcjonalne do czasu dostępu do

pamięci- nie da się skonstruować pamięci o

dowolnie krótkim dostępie

odpowiedzią na powyższy problem jest

warstwowa struktura pamięci-hierarchię

pamięci tworzą warstwy o zróżnicowanej

pojemności i szybkości

im dalsza w stosunku do procesora warstwa

tym coraz większa jej pojemność i czas

dostępu

Żródło:wazniak.mimum.edu.pl

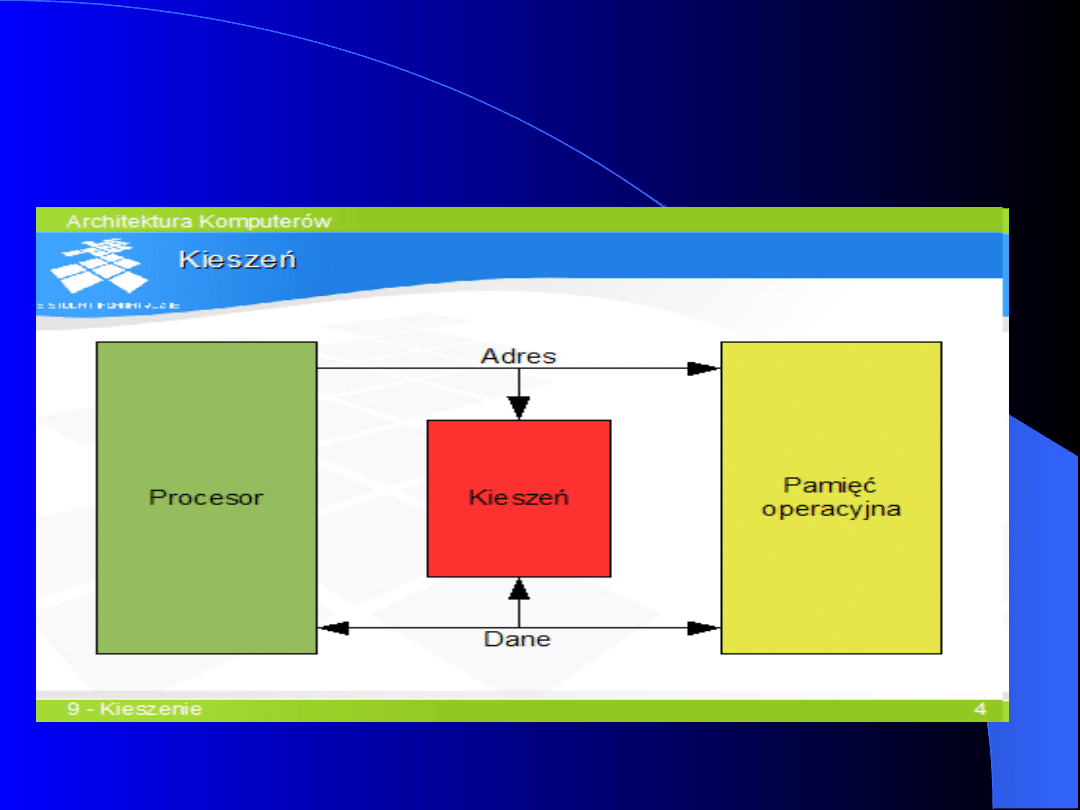

Kieszenie- schemat

Kieszenie- schemat

funkcjonalny

funkcjonalny

Żródło:wazniak.mimum.edu.pl

Sterowanie

Sterowanie

poszczególnymi

poszczególnymi

warstwami pamięci

warstwami pamięci

rejestry – dostęp bardzo szybki, bo fizycznie

umieszczone w procesorze, dane umieszcza programista

lub kompilator

kieszenie – bufor między rejestrami, a pamięcią

operacyjną przyspieszający dostęp do tej pamięci, styk

kieszeni i pamięci operacyjnej jest sterowany sprzętowo

pamięć operacyjna – dostęp w pełnym tego słowa

znaczeniu bezpośredni

pamięć wirtualna – rozszerza pamięć operacyjną,

stykiem pamięci operacyjnej i wirtualnej steruje system

operacyjny, dane w pamięci wirtualnej umieszcza

użytkownik otwierając plik z danymi lub uruchamiając

program

Sterowanie

Sterowanie

poszczególnymi

poszczególnymi

warstwami pamięci

warstwami pamięci

lokalny system plików rozszerzony o

zasoby zdalne (nośniki)- naturalne

rozszerzenie pamięci o możliwości

nieograniczonego pojemnościowo ( w

sensie całości zasobów) zapisu danych,

dane, przemieszczaniem danych w tych

warstwach hierarchii steruje użytkownik.

Czas dostępu do zasobów lokalnych jest

zróżnicowany zależnie od nośników (dysk,

taśma, dysk optyczny)

Żródło:wazniak.mimum.edu.pl

Document Outline

- Slide 1

- Slide 2

- Slide 3

- Slide 4

- Slide 5

- Slide 6

- Slide 7

- Slide 8

- Slide 9

- Slide 10

- Slide 11

- Slide 12

- Slide 13

- Slide 14

- Slide 15

- Slide 16

- Slide 17

- Slide 18

- Slide 19

- Slide 20

- Slide 21

- Slide 22

- Slide 23

- Slide 24

- Slide 25

- Slide 26

- Slide 27

- Slide 28

- Slide 29

- Slide 30

- Slide 31

- Slide 32

- Slide 33

- Slide 34

- Slide 35

- Slide 36

- Slide 37

- Slide 38

- Slide 39

- Slide 40

- Slide 41

- Slide 42

- Slide 43

- Slide 44

Wyszukiwarka

Podobne podstrony:

spr aok ilona2, Wojskowa Akademia Techniczna (WAT) INFORMATYKA, SEM1, Architektura i Organizacja Kom

AOK ściąga, Wojskowa Akademia Techniczna (WAT) INFORMATYKA, SEM1, Architektura i Organizacja Kompute

Organizacje komputery ludzie studium postępu technicznego

ORGANIZACJA KOMPUTERÓW

mazurkiewicz,Technika Cyfrowa, organizacjie komputerów

Organizacja stanowiska pracy z komputerem

Organizacja pamięci komputerów, szkola, systemy operacyjne, klasa 1

Szkolenie BHP, ORGANIZACJA STANOWISKA PRACY Z KOMPUTEREM, ORGANIZACJA STANOWISKA PRACY Z KOMPUTEREM

Architektura i organizacja komuterów W3 Działanie komput

Zagadnienia na zaliczenie z organizacji i architektury kompu, Urządzenia techniki komputerowej (UTK)

Organizacja stanowiska pracy z komputerami

komputery w chemii organicznej

Organizacja stanowisk pracy z komput

Architektura i organizacja komuterów W3 Działanie komputera

Organizacja pracy przy komputerze

Praca przy komputerze, Organizacja stanowisk pracy

więcej podobnych podstron